Verilog FPGA编程实战教程:数字电路与信号处理

"本资源是一份关于Verilog HDL的教程,主要针对FPGA编程,内容涵盖基础概念、实例解析及练习题目,包括加法器、乘法器、比较器等组合逻辑电路的设计。教程首先介绍了数字信号处理、计算、程序、算法以及硬线逻辑在现代电子系统中的应用,强调了专用集成电路在实时和高性能需求中的重要性。"

这篇教程旨在帮助读者掌握Verilog这一重要的FPGA编程语言,通过学习,读者能够理解和应用Verilog来设计和实现数字逻辑电路。Verilog HDL(硬件描述语言)是一种用于描述电子系统的文本语言,它允许工程师以抽象的方式定义电路行为,从而可以被综合成实际的硬件。

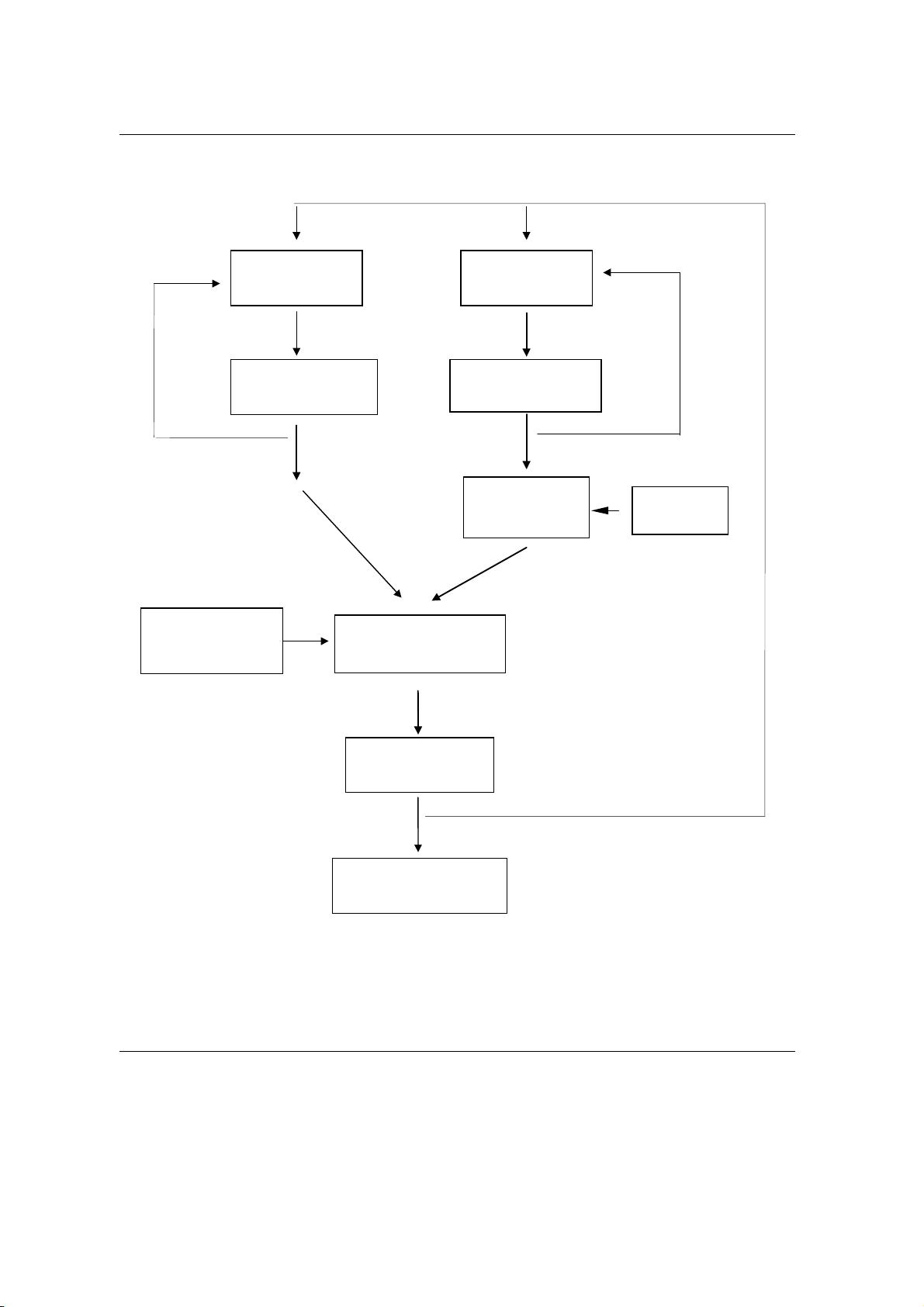

在教程的第一章,作者阐述了数字信号处理的基础,包括滤波、变换、编码等数学运算在通信系统中的应用。这些操作通常可以通过软件实现,如使用C、Pascal或汇编语言编写程序。然而,对于需要实时处理的场景,例如军用通信和雷达系统,通用计算机的处理速度无法满足需求,这时就需要使用硬件实现,如通过FPGA(现场可编程门阵列)来设计高速、定制化的硬线逻辑电路。

FPGA是一种可重构的半导体器件,可以快速原型验证和实现数字逻辑设计。通过Verilog HDL,工程师可以描述电路的逻辑功能,然后将其编译到FPGA中,实现高效、灵活的硬件解决方案。与通用微处理器相比,FPGA的优势在于其并行处理能力,无需经过指令集架构的限制,可以直接执行硬件描述的逻辑操作,这对于时间敏感的应用至关重要。

教程中会涉及的实例,如加法器、乘法器和比较器,这些都是数字逻辑设计的基础元素,广泛应用于各种数字系统中。通过这些实例,学习者可以逐步掌握Verilog的语法和设计方法,同时,通过练习题目进一步巩固理论知识,提高实际设计能力。

这个Verilog教程适合对FPGA编程感兴趣或者需要在硬件级别实现数字逻辑的工程师和学生,通过学习,他们将能够有效地设计和实现复杂的数字系统。

288 浏览量

2013-04-20 上传

2012-04-04 上传

149 浏览量

number_zhangteng

- 粉丝: 0

- 资源: 3

最新资源

- 通过多线程任务处理大批量耗时业务并返回结果

- yii1-another-ueditor-extension:yii1的百度编辑器ueditor扩展

- faq-uitableview-collapsible:本机UI Tableview可折叠

- chafen_无穷小量_

- guake_intuivo_cli:Bash适用于喜欢使用有关Guake Terminal的bash进行编程的人的工具

- kitaminka.github.io

- lyncs.quda:python的点阵QUDA接口

- androidormliteexample:使用 ORMLite 的简单 Android 应用程序示例

- Angular.js Web页面框架 v1.8.2

- filterbypass:浏览器的XSS筛选器旁路备忘单

- angular-hubspot-messenger:Hubspot Messenger吐司通知库的AngularJS包装器

- 号码系统转换器Android应用

- 下一个初学者尾风

- EIA1-Semester21

- 易语言-易语言置入代码例程 多项选择执行子程序

- Suitecrm 2020年11月最新中文语言包 SuiteCRM-7.11.18 SuiteCRM core (zh-CN).zip