版图设计:反相器实例与DRC/LVS模拟步骤详解

需积分: 0 59 浏览量

更新于2024-08-04

2

收藏 248KB DOCX 举报

本文档主要介绍了如何在虚拟环境下进行反相器的版图设计与验证过程,涉及到了使用VNC远程登录服务器、 Virtuoso软件的操作步骤以及版图绘制的具体细节。以下是主要内容的详细解读:

1. **远程登录与VNC端口创建**

- 使用MobaXterm创建新的会话,输入远程主机IP(10.20.20.46),账号和密码,然后输入vncs来建立VNC连接。

- 登录后,通过VNCs访问10.20.20.46的服务器,输入相应的服务器地址和密码,以便进入 Virtuoso工作环境。

2. **Virtuoso软件操作**

- 打开Virtuoso,选择"Tools" -> "LibraryManager",然后创建一个新的库,命名为"Tuotorial-layout",并选择已有的技术库进行关联。

- 创建CellView,如inv,选择layout视图,以方便版图设计。

3. **版图设计步骤**

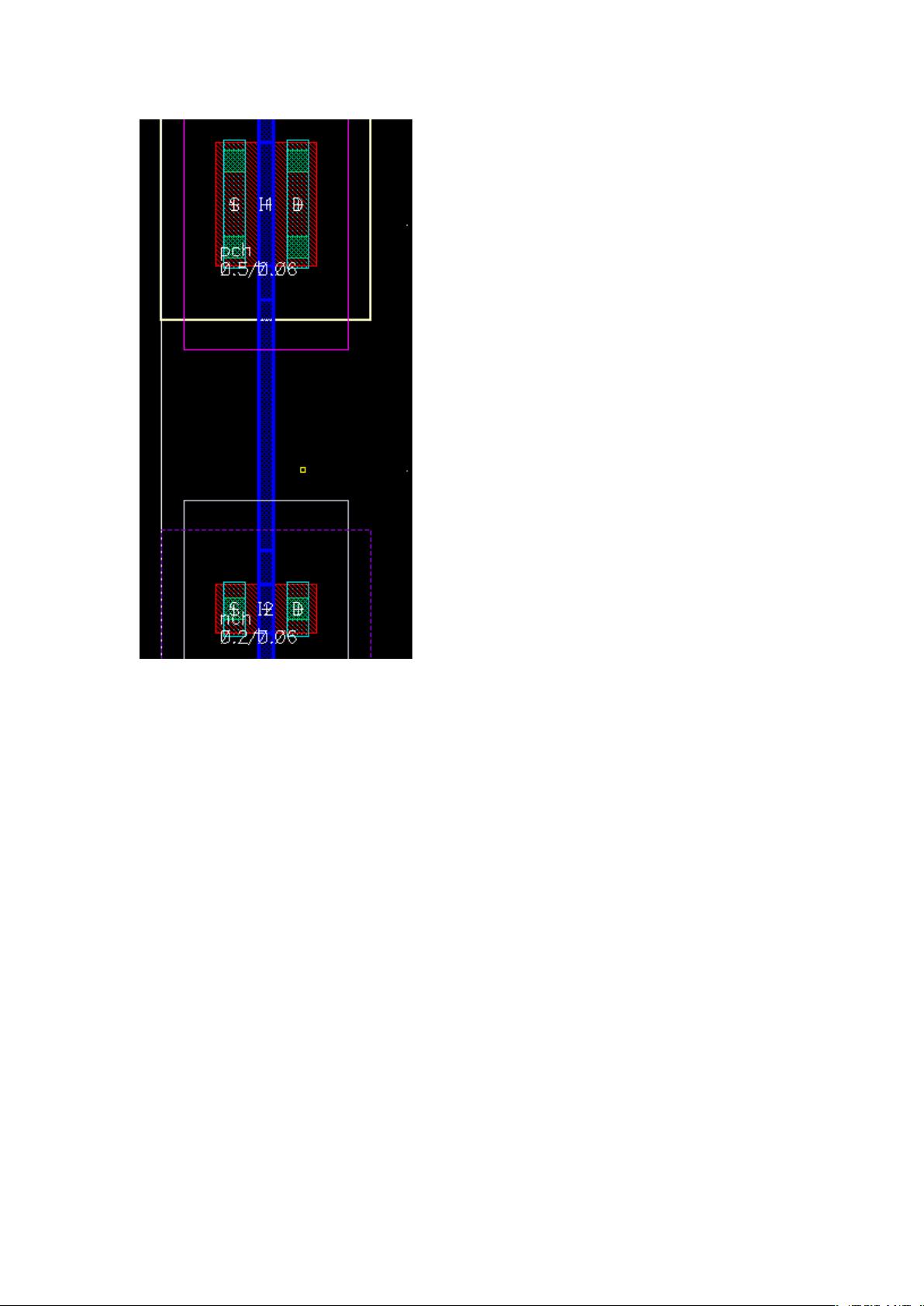

- 在版图编辑窗口中,利用Create -> Instance功能添加TSMC N65库中的元件,如pch和nch,按照指定位置和尺寸布局。

- 通过LSW窗口和快捷键(如R键)绘制多晶硅区和金属层,确保电气连接的正确性。注意不同层之间的距离要求,例如M1层的矩形框需与MOSFET的漏区和源区对齐。

- 通过创建contacts和金属框,以及Create -> Via功能添加输入端口,保持与多晶硅区的对齐。

- 最后,创建引脚并输入终端名称,设置相应的参数,包括与衬底的连接,如vd。

4. **DRC(Design Rule Checking)与LVS(Layout Versus Schematic)仿真**

- 在完成版图设计后,通常需要进行DRC检查以确保设计符合规则,而LVS则用于比较版图和电路原理图的一致性,确保信号完整性。

- 未在描述中明确提及具体步骤,但这是版图设计流程中的重要环节,一般使用类似Virtuoso或特定EDA工具(如Cadence、Synopsys等)进行这两项验证。

本篇文档提供了反相器版图设计过程中,从远程登录、Virtuoso操作到版图绘制、电气连接和验证的详细指南,适合进行集成电路设计初学者或工程师参考。在实际操作中,熟练掌握各种工具和技术规范是至关重要的。

2019-04-22 上传

2022-09-13 上传

2013-07-26 上传

2010-11-21 上传

2010-03-20 上传

2022-06-27 上传

胡说先森

- 粉丝: 452

- 资源: 280

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全