TMS320C64x+ DSP上CRC的高效软件实现及其应用

125 浏览量

更新于2024-08-30

收藏 111KB PDF 举报

嵌入式系统/ARM技术中的CRC(循环冗余校验)算法在TMS320C64x+系列数字信号处理器(DSP)上的高效实现是本文关注的核心。CRC是一种常用的差错检测技术,它的主要特点是信息字段和校验字段的长度可以根据需要灵活设置,如GCRC16(X)的生成多项式为X16+X12+X5+1。

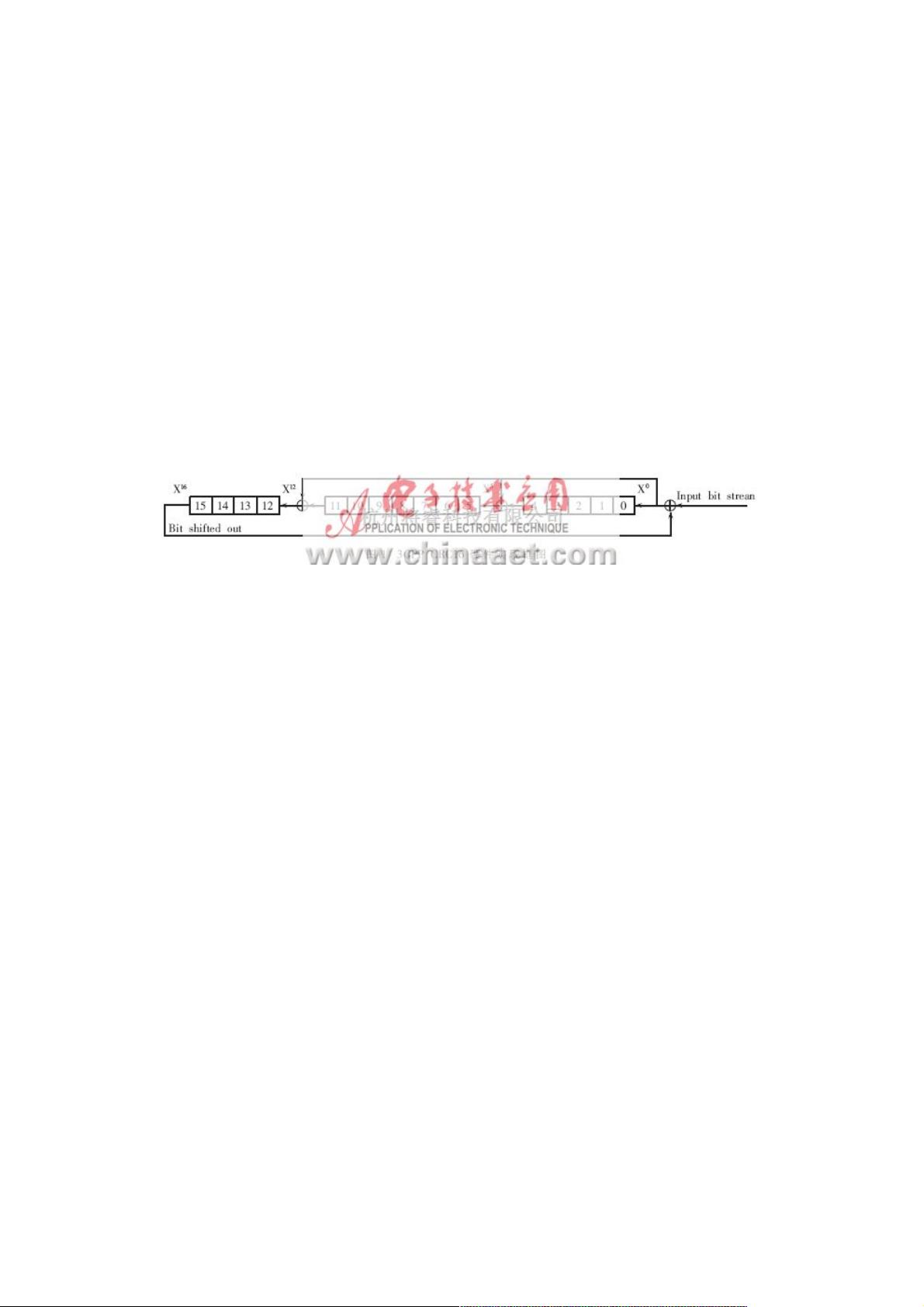

常规的CRC实现方式通常依赖于硬件,例如通过硬件移位寄存器来完成,如3GPP CRC16的结构所示。这个过程涉及到异或(XOR)运算,其中移位寄存器的状态与生成多项式的系数对应,操作前移位寄存器会被清零,然后数据逐位加载,每个新数据位都会进行异或运算,最终寄存器的结果就是CRC码。

然而,在TMS320C64x+ DSP上,为了提高软件实现的灵活性,CRC校验也可以在软件层面完成。一个简单的软件实现伪代码通过循环处理输入数据的每一位,根据输入比特的值更新CRC值。如果输入为1,执行异或操作(如与0x1021进行),如果输入为0,则不做任何操作。这种方法虽然灵活,但效率较低,因为每次循环只处理一个位,这限制了处理速度。

为了优化软件实现,可以考虑使用并行处理或者预先计算部分计算结果,减少重复操作。此外,还可以利用硬件加速,比如使用专门的CRC计算单元,结合软件控制,以提高整体性能。在实际应用中,设计者需要权衡软件实现的灵活性和硬件加速带来的性能提升,根据具体的应用场景和资源限制选择合适的方案。

总结来说,本文提供了CRC在TMS320C64x+ DSP上的软件实现策略,包括理论推导、硬件与软件比较以及具体的代码示例,这对于嵌入式系统的开发者来说,是一项重要的参考和技术指导,特别是在需要高效数据传输和错误检测的实时应用中。

2020-10-22 上传

2020-10-26 上传

2020-12-10 上传

2017-11-24 上传

2021-09-18 上传

2020-10-22 上传

2020-10-21 上传

2020-11-02 上传

weixin_38744778

- 粉丝: 7

- 资源: 917

最新资源

- PyPI 官网下载 | vam.whittaker-2.0.1-cp36-cp36m-win_amd64.whl

- 自定义横幅CollectionView布局-Swift开发

- ASP-online-shopping-system.rar_百货/超市行业_ASP_

- java jdk 8.0安装包

- 一种从命令行打开拉取请求的便携式无魔术方式

- 2018-2019年华东师范大学825计算机学科基础考研真题

- autofan-开源

- intelliPWR:intelliPWR的核心

- 人工智能实践课程小项目——对话机器人.zip

- 参考资料-412A.混凝土路面砖试验报告.zip

- Ant Lob Accessor-开源

- FTP.zip_Ftp客户端_Visual_C++_

- MATLAB-Improved-ABC-Algorithm:MATLAB改进的ABC算法

- atp-website:Surigao del Sur行动追踪和保护网站

- 家居装饰:使用虚拟现实的家居装饰

- LKCMS日历黄历修正版 v1.0