基于FPGA、DSP与VLIW DSP的DRM信道编码器模块实现与比较

需积分: 5 121 浏览量

更新于2024-08-12

收藏 884KB PDF 举报

本文主要探讨了2005年关于DRM(Digital Radio Mondiale,数字广播全球化)系统信道编码器模块的实现技术研究。作者陈伟、邓纶晖和陈远知基于欧洲广播联盟(EBU)发布的ETSI DRM系统标准,针对FPGA(Field-Programmable Gate Array,现场可编程门阵列)、普通DSP(Digital Signal Processor,数字信号处理器)以及VLIW DSP(Very Long Instruction Word Digital Signal Processor,非常长指令字数字信号处理器)三种不同的硬件平台进行了信道编码器模块的构建。

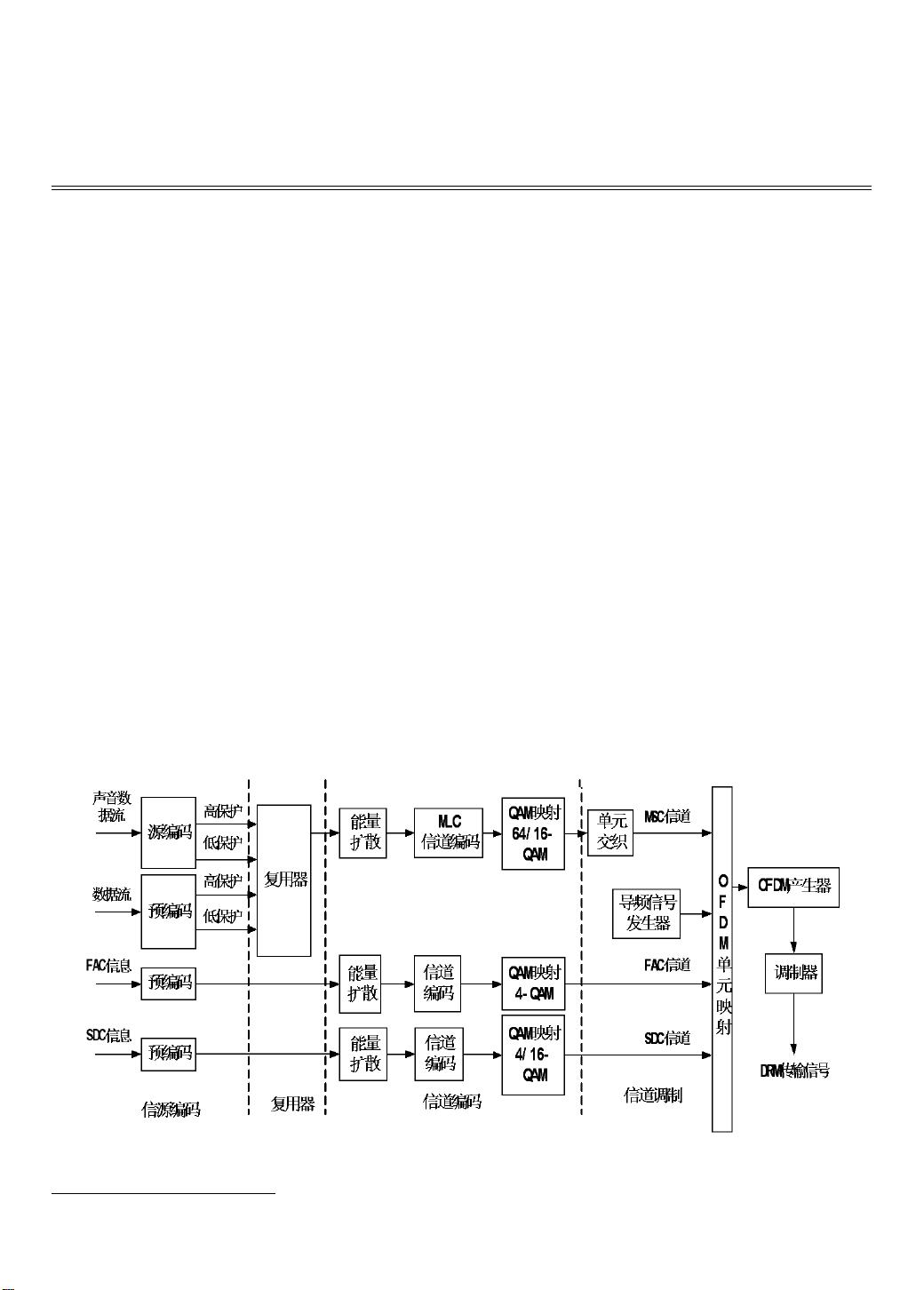

首先,DRM系统被设计用于调幅广播的数字化,因其具有统一标准、成本低和覆盖广泛的优势。DRM系统能够在30MHz以下的长、中、短波段工作,并能适应各种信道传输条件。发送端主要包括源编码器和预编码器,支持MPEG-4AAC、MPEG-4CELP和MPEG-4HVXC等多种编码方案,以提供高质量音频编码。

在硬件实现上,信道编码器是关键组件,它包含了能量扩散、MLC编码(分层可删除卷积编码)和伪比特交织等功能,确保数据的安全性和可靠性。此外,还采用了QAM(Quadrature Amplitude Modulation,正交幅度调制)映射,以提高信号的传输效率。在VLIW DSP平台上,高效的并行处理能力使得编码过程更为快速和精确。

文章通过对比基于FPGA、普通DSP和VLIW DSP平台的实现,分析了它们在资源占用、性能优化和实现复杂度等方面的差异。这种比较有助于评估不同硬件平台对于DRM信道编码器的实际应用价值,为硬件选择和系统设计提供了实用参考。

总结来说,本文的核心内容是介绍了一种根据ETSI DRM标准的信道编码器模块在不同硬件平台上的设计与实现策略,并通过深入分析,揭示了这些硬件平台在DRM系统中的优势和局限性,对于理解和改进DRM系统的硬件实现有着重要的学术价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-05-31 上传

2021-05-17 上传

2021-05-17 上传

2021-04-28 上传

2021-05-15 上传

102 浏览量

weixin_38747087

- 粉丝: 77

- 资源: 1267

最新资源

- 易语言写图片源码,易语言缩略图源码,易语言超级列表框显示缩略图

- orca-endeavours

- befchina.github.io

- hidden:超轻便的MacOS实用程序,可帮助隐藏菜单栏图标

- assignment-2015-1:2015 年课程的第一个作业

- 算法_halfway9ya_MPDA算法_PDA_Kalmanfilter_pda算法

- Hello-World:协调性测试解决方案

- 光栅化器:OBJ文件光栅化器

- mod_rpaf-0.6.tar.gz

- 包括微博等评论以及对应的情感,分为积极和消极两种,适用于情感分析训练

- 易语言超级列表框时钟刷新

- NanoVNA:非常微小的掌上型矢量网络分析仪

- 系统-SISWalletAdmin

- 从0开始学习微服务架构

- Toastmasters - Pathways Keyboard Navigation-crx插件

- finance-node