CPLD/FPGA实现多串口扩展:工业控制通讯新方案

96 浏览量

更新于2024-09-01

收藏 285KB PDF 举报

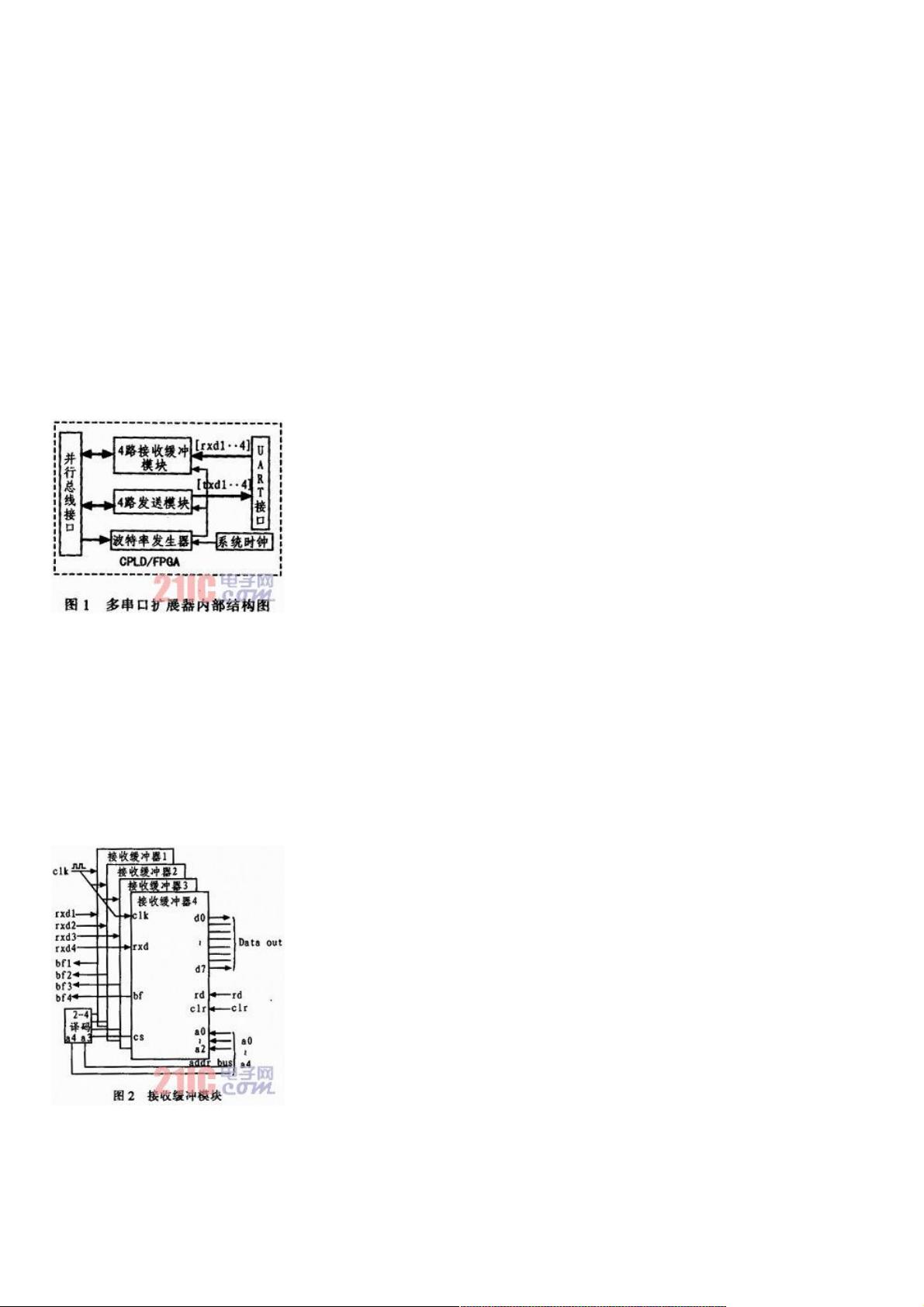

"基于CPLD/FPGA的多串口设计实现了工业控制中串口通讯的扩展和优化,通过嵌入式技术确保了系统的可靠性和集成性。设计利用CPLD/FPGA芯片,构建了一个包括并行总线接口、接收缓冲器、发送器、波特率发生器和UART接口的系统结构,解决了高速CPU与RS232设备间的速度匹配问题。每个UART接收器具有8个接收缓冲单元,可以根据需要调整串口数量和缓冲单元数量。系统设计包括接收缓冲模块、发送模块以及波特率发生器等关键功能模块。"

在工业控制领域,串口通信因其简单高效而被广泛应用。然而,传统方法如PCI扩展卡或复杂扩展芯片在成本和设计复杂性上存在问题。随着嵌入式技术的发展,CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的多串口扩展方案应运而生,它们能以更低的成本和更简洁的硬件设计实现多个串口的管理和扩展。

该设计方案的核心是CPLD/FPGA芯片,它通过内部编程实现并行总线到多个串行接口的转换。系统包含四个主要部分:并行总线接口用于连接嵌入式CPU,4路接收缓冲器用于处理串行数据接收,4路发送器用于发送数据,波特率发生器则可根据需求调整波特率,以适应不同的通讯设备。接收缓冲器的创新之处在于每个接收器都有8个接收缓冲单元,这提高了数据传输的实时性,确保高速CPU与RS232设备间的速率匹配。

接收缓冲模块是系统的关键组成部分,其结构设计包括4个独立的接收缓冲器,每个都具有自己的rxd、bf和cs引脚。这些引脚分别负责串行数据输入、接收状态指示和缓冲器的选择。接收缓冲器通过2-4译码器进行片选,根据地址线选择相应的缓冲器。数据总线、读缓冲信号和缓冲单元地址线则是所有接收缓冲器共享的资源。

此外,发送模块虽然在描述中没有详述,但通常会包含类似的结构,用于将CPU的并行数据转化为串行数据输出。波特率发生器则根据外部晶振提供的时钟信号生成适当的波特率,以确保数据传输的准确性和效率。

总结来说,基于CPLD/FPGA的多串口设计是一种高效、灵活的解决方案,它可以适应不同环境下的串口扩展需求,提高系统集成度,增强通讯可靠性,并且可以通过调整接收缓冲单元数量来优化数据传输性能。这样的设计对于工业控制系统尤其是嵌入式系统的应用具有重大意义。

2014-08-17 上传

2021-04-18 上传

2014-08-04 上传

2024-08-10 上传

2023-05-24 上传

2023-04-19 上传

2024-06-14 上传

2024-02-02 上传

2023-07-21 上传

weixin_38635996

- 粉丝: 3

- 资源: 851

最新资源

- 高效办公必备:可易文件夹批量生成器

- 吉林大学图形学与人机交互课程作业解析

- 8086与8255打造简易乒乓球游戏机教程

- Win10下C++开发工具包:Bongo Cat Mver、GLEW、GLFW

- Bootstrap前端开发:六页果蔬展示页面

- MacOS兼容版VSCode 1.85.1:最后支持10.13.x版本

- 掌握cpp2uml工具及其使用方法指南

- C51单片机星形流水灯设计与Proteus仿真教程

- 深度远程启动管理器使用教程与工具包

- SAAS云建站平台,一台服务器支持数万独立网站

- Java开发的博客API系统:完整功能与接口文档

- 掌握SecureCRT:打造高效SSH超级终端

- JAVA飞机大战游戏实现与源码分享

- SSM框架开发的在线考试系统设计与实现

- MEMS捷联惯导解算与MATLAB仿真指南

- Java实现的学生考试系统开发实战教程