I2C总线规范V2.1更新:Hs模式详解

需积分: 13 177 浏览量

更新于2024-07-17

收藏 844KB PDF 举报

"I2C总线规范.pdf"

本文档详细介绍了I2C(Inter-Integrated Circuit)总线规范的V2.1版,该版本相较于早期版本进行了一些微小的调整,特别是在高速(Hs)模式下。I2C是一种两线式串行通信协议,由飞利浦(现为NXP半导体)开发,用于设备间的短距离通信。

1. 版本更新:

- 版本1.0于1992年发布,奠定了I2C的基本框架。

- 版本2.0在1998年推出,对协议进行了增强。

- 版本2.1在2000年发布,主要增加了Hs模式的详细规范。

2. I2C的优势:

- 对于设计人员,I2C提供了简单、高效的接口,减少了所需的引脚数量,降低了硬件复杂性。

- 对于厂商,I2C的标准化使得不同制造商的设备可以轻松互连,扩大了市场潜力。

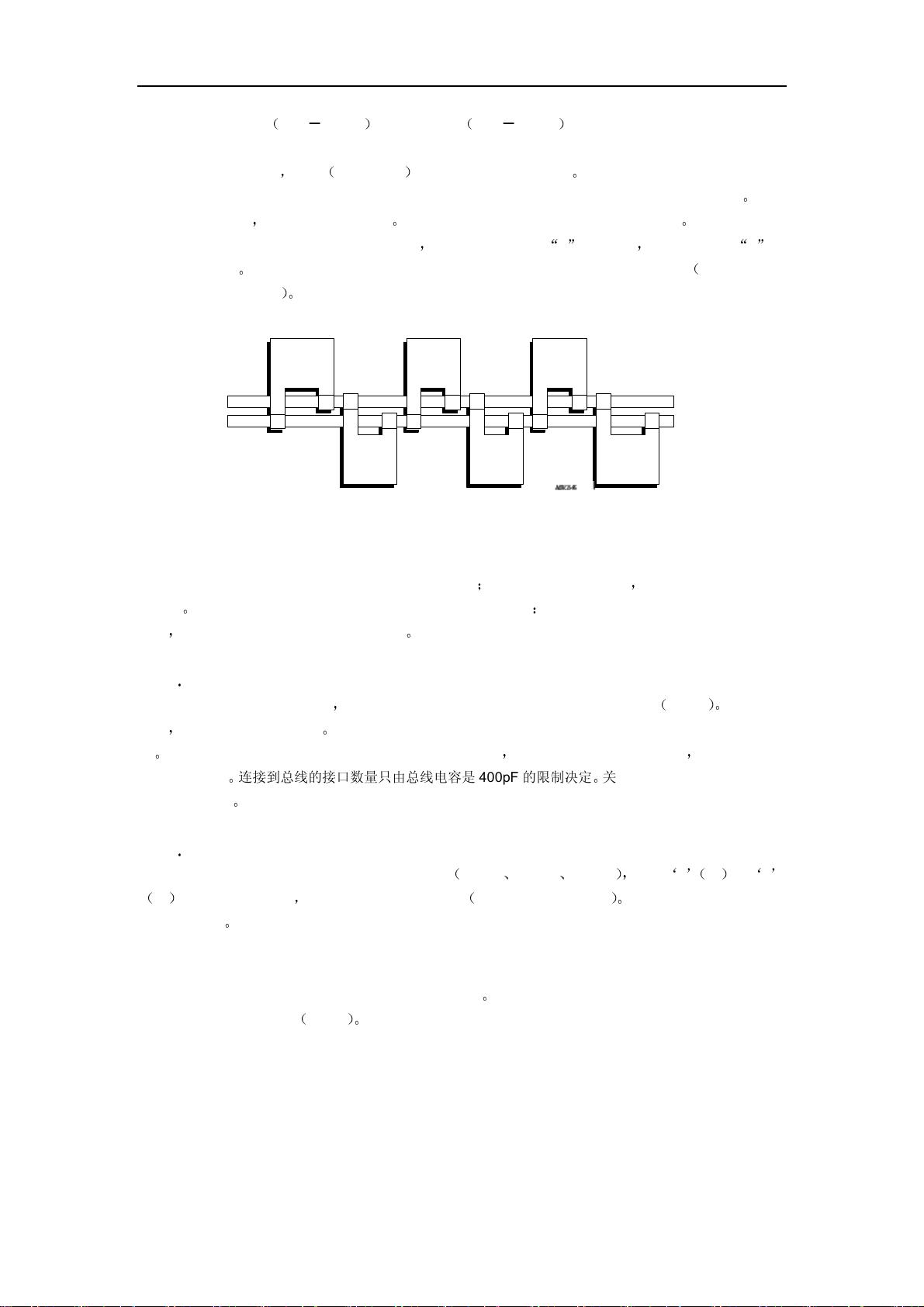

3. I2C总线概念:

- I2C总线由两条线组成:数据线SDA(Serial Data Line)和时钟线SCL(Serial Clock Line)。

- 它支持多主控器和多个从设备的环境,通过总线仲裁来避免冲突。

4. 总线特征:

- 包括标准模式、快速模式和高速模式,分别对应不同的数据传输速率。

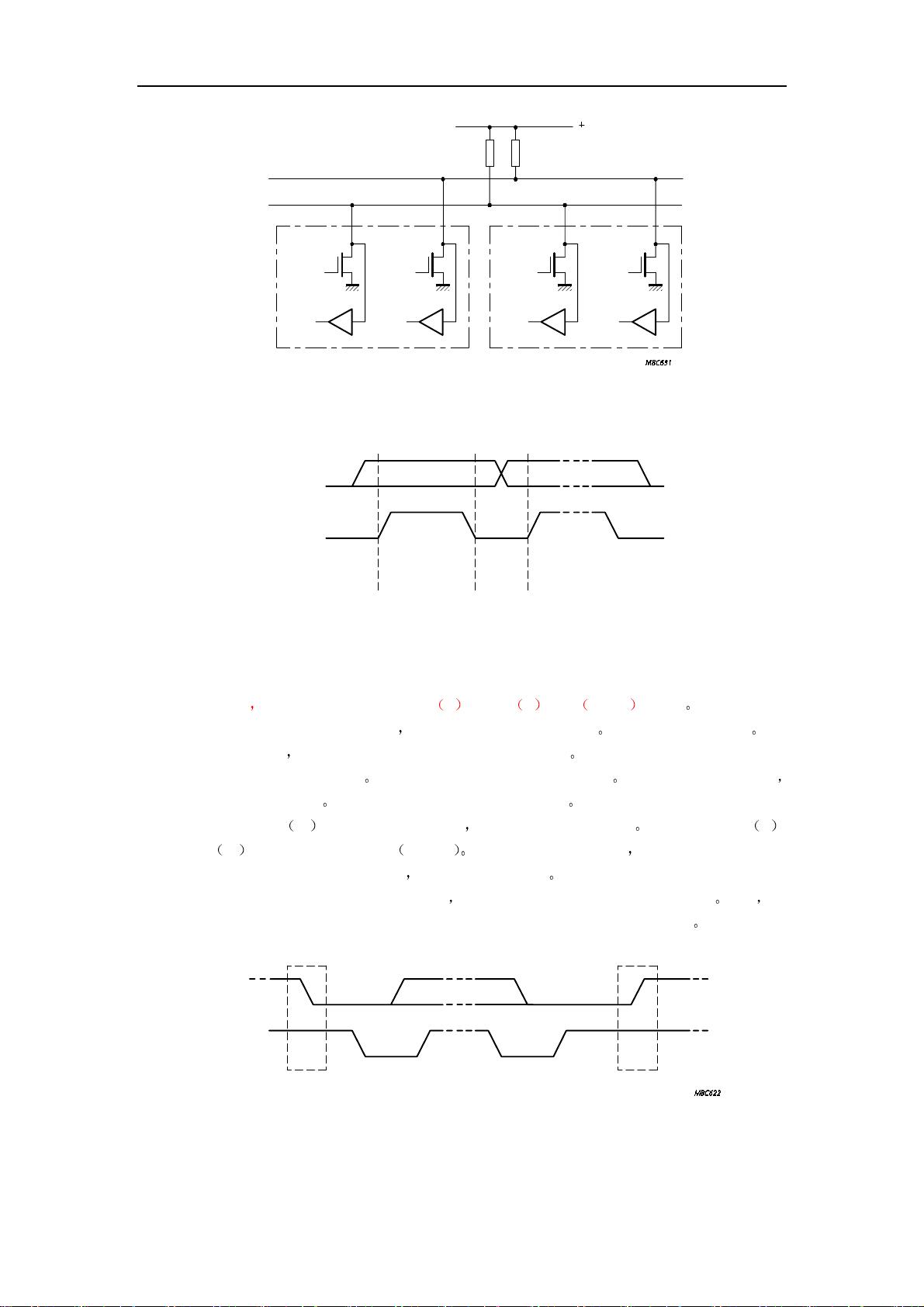

- 在Hs模式下,重复起始条件后的时钟信号SCLH可以被延长,这是V2.1的一个重要改动。

5. 位传输:

- 数据有效性取决于SDA和SCL线的状态。

- 起始和停止条件是数据传输的关键转折点,它们由特定的SDA和SCL组合表示。

6. 传输数据:

- 字节以MSB(最高有效位)先发送,每个字节后跟一个应答位。

- 响应分为ACK(确认)和NAK(否定应答),通过从设备的SDA线反馈给主控器。

7. 寻址:

- I2C支持7位和10位寻址,允许最多128个或1024个设备共享总线。

- 广播呼叫地址允许向所有设备发送同一消息。

8. 时序和仲裁:

- 同步通过共同的时钟信号SCL实现。

- 仲裁发生在多个主控器同时尝试发送数据时,通过比较SDA线上发送的数据来确定主控权。

9. 电气规范和时序:

- 不同模式下,SDA和SCL线的电压电平、上升时间、下降时间和最大数据速率都有特定要求。

- Hs模式对电气特性有更严格的规定,以支持更高的传输速度。

10. 混合速度模式:

- 允许F/S(快速/标准)模式和Hs模式的设备共存于同一总线,通过特定的切换和兼容性考虑确保通信顺畅。

11. 应用信息:

- 快速模式I2C器件需要考虑斜率控制和开关上拉电路的设计,以满足高速传输的要求。

- 连接到总线的器件需要符合规定的输入和输出阻抗,以维持信号完整性和总线稳定性。

I2C规范V2.1版的这些改动和扩展,旨在提高系统性能,增加灵活性,并适应更广泛的应用场景,尤其是在需要高速数据传输的场合。理解并正确应用这些规范对于设计和实现基于I2C的系统至关重要。

203 浏览量

119 浏览量

240 浏览量

499 浏览量

2021-12-12 上传

2019-09-13 上传

u011132970

- 粉丝: 1

- 资源: 6