没有合适的资源?快使用搜索试试~ 我知道了~

首页JESD209-2F:定义LPDDR2标准,涵盖64Mb至32Gb内存技术

JESD209-2F:定义LPDDR2标准,涵盖64Mb至32Gb内存技术

JESD209-2F是JEDEC(固态技术协会)制定的一份标准文档,专门针对低功耗双数据速率2(LPDDR2)内存技术。该标准定义了一系列LPDDR2的不同版本,包括LPDDR2-S2A、LPDDR2-S2B、LPDDR2-S4A、LPDDR2-S4B、LPDDR2-N-A和LPDDR2-N-B,涵盖了从64Mb到8Gb的x8、x16和x32 SDRAM设备,以及从64Mb到32Gb的NVM(非易失性内存)设备。LPDDR2继承了DDR2(JESD79-2)、DDR3(JESD79-3)和LPDDR(JESD209)的技术基础,并在N07-NV1A的基础上进行了扩展。

该标准详细规定了LPDDR2的各种特性,如功能和性能规格、电气特性和信号分配,同时还包括封装形式和球栅阵列(Ball Grid Array,BGA)布局。标准的制定过程经过了委员会投票和审批,确保了其技术的准确性和一致性。值得注意的是,JEDEC声明了可能与该标准相关的专利情况,但并未提供任何关于许可的保证或拒绝,因此任何使用该标准的个人或公司都需自行承担由此产生的法律责任。

JESD209-2F标准旨在消除制造商间的误解,促进技术创新和发展,通过公开透明的方式推动行业规范,为低功耗内存市场提供了统一的技术依据。遵循这一标准,制造商能够确保他们的产品符合JEDEC的合规要求,从而在市场上具有竞争力。同时,该标准也强调了法律上的免责声明,明确表示JEDEC不对专利的效力或相关性做出判断,用户在使用过程中应自行评估潜在风险。

JESD209-2F是电子行业内的一个关键参考文档,对于开发和设计低功耗双数据速率内存产品,以及理解LPDDR2技术的最新进展和标准规范至关重要。

JEDEC Standard No. 209-2F

Page 10

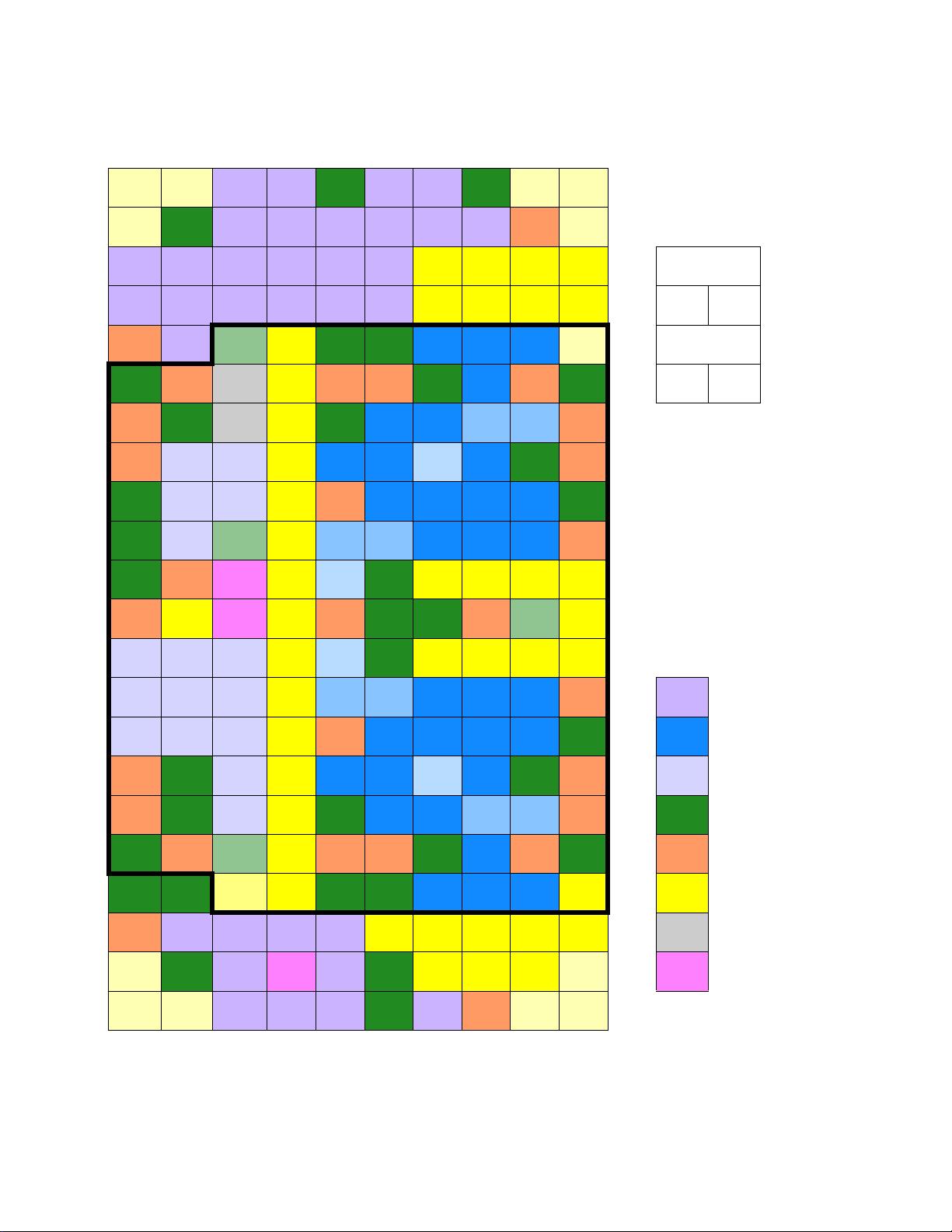

2.9 180-ball x16/x32 LPDDR2, SDR-Flash, and e-MMC package ballout

NOTE 1: 0.5mm (x32, x16) or 0.65mm pitch (x32, x16), 22 rows

NOTE 2: 180 Ball Count

NOTE 3: Top View, A1 in Top Left Corner

NOTE 4: See JESD21-C, Section 3.12.1

1 2 3 45678 910

A DNU DNU WP_n CLE VCCN

IO4

DQ4

IO7

DQ7

VCCN DNU DNU

B

DNU VCCN

IO11

DQS

ALE RE_n

IO5

DQ5

IO14

NC

IO15

NC

VSS DNU

C

IO10

NC

IO1

DQ1

IO3

DQ3

WE_n R/B_n

IO6

DQ6

NB NB NB NB

SDR NVM Ball Definition

where 2 labels are pres-

ent

D

IO8

NC

IO0

DQ0

IO2

DQ2

CE_n

IO12

NC

IO13

NC

NB NB NB NB

1st Row

2nd Row

NVM device

ONFI

device

E VSS

IO9

NC

VACC NB VDD2 VDD1

DQ31

NC

DQ29

NC

DQ26

NC

DNU

LPDDR2 Ball Definition

where 2 labels are pres-

ent

F VDD1 VSS ZQ1 NB VSS VSSQ VDDQ

DQ25

NC

VSSQ VDDQ

1st Row

2nd Row

x32 device

x16 device

G

VSS VDD2 ZQ0 NB VDDQ

DQ30

NC

DQ27

NC

DQS3_t

NC

DQS3_c

NC

VSSQ

H VSSCA CA9 CA8 NB

DQ28

NC

DQ24

NC

DM3

NC

DQ15 VDDQ VSSQ

J

VDDCA CA6 CA7 NB VSSQ DQ11 DQ13 DQ14 DQ12 VDDQ

K VDD2 CA5 Vref(CA) NB DQS1_c DQS1_t DQ10 DQ9 DQ8 VSSQ

L VDDCA VSS CK_c NB DM1 VDDQ NB NB NB NB

M VSSCA NC CK_t NB VSSQ VDDQ VDD2 VSS Vref(DQ) NB

N CKE0 CKE1 CKE2 NB DM0 VDDQ NB NB NB NB

P CS0_n CS1_n CS2_n NB DQS0_c DQS0_t DQ5 DQ6 DQ7 VSSQ

Flash Memory

(eMMC/NVM/ONFI) ADD/CTRL

R CA4 CA3 CA2 NB VSSQ DQ4 DQ2 DQ1 DQ3 VDDQ LPDDR2 DQ

T VSSCA VDDCA CA1 NB

DQ19

NC

DQ23

NC

DM2

NC

DQ0 VDDQ VSSQ LPDDR2 CA

U

VSS VDD2 CA0 NB VDDQ

DQ17

NC

DQ20

NC

DQS2_t

NC

DQS2_c

NC

VSSQ Power

V VDD1 VSS VACC NB VSS VSSQ VDDQ

DQ22

NC

VSSQ VDDQ Ground

W VCCm VDDIm NC NB VDD2 VDD1

DQ16

NC

DQ18

NC

DQ21

NC

DNU

Do Not Use/NC/No

Ball

Y VSS DAT2 CMD DAT6 DAT1 NB NB NB NB NB ZQ

AA

DNU VCCQm DAT4 CLKm DAT0 VCCm NB NB NB DNU Clock

AB DNU DNU DAT3 DAT5 DAT7 VCCQm RST_n VSS DNU DNU

JEDEC Standard No. 209-2F

Page 11

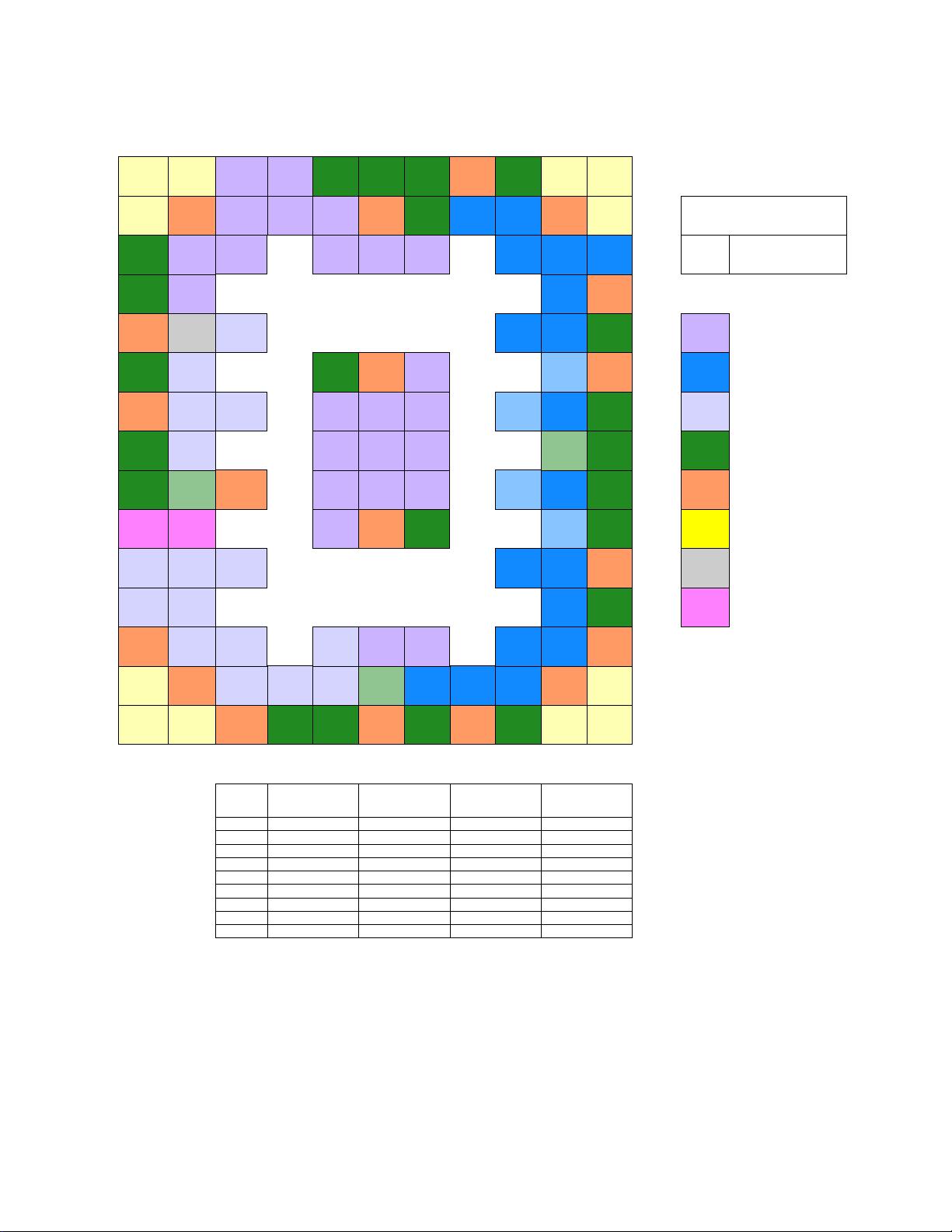

2.10 121-ball x16 LPDDR2, SDR Flash-NVM, and e-MMC package ballout

NOTE 1: 0.5mm pitch, 15 rows

NOTE 2: 121 Ball Count

NOTE 3: Top View, A1 in Top Left Corner

NOTE 4: See JESD21-C, Section 3.12.2

1234567891011

A NC NC

DAT2

ADQ9

DQ2

DAT5

ADQ2

DQ5

VDDI

VCCQx

VCC VDD2 VSS VDDQ NC NC

B

NC VSSx

DAT3

ADQ1

DQ3

DAT6

ADQ11

DQ6

DAT7

ADQ3

DQ7

VSSx VDD1 DQ15 DQ14 VSSQ NC

SDR NVM Ball Definition

where 3 labels are present

C VCCQ

DAT0

ADQ8

DQ0

DAT4

ADQ10

DQ4

CLK e

CLK o,f

DQS i

CMD e

RDY o

WAIT f

RST_n e,f

RP_n o

CLE n,i

DQ11 DQ12 DQ13

1st Row

2nd Row

3rd Row

eMMC (e)

OneNAND (o) / AAD Nor (f)

Raw NAND (n) / ONFI2 (i)

D

VDD2

DAT1

ADQ0

DQ1

DQ10 VSSQ

E VSS ZQ CA9 DQ8 DQ9 VDDQ

Flash Memory

(eMMC/Raw NAND/One-

NAND)

F VDD1 CA8 VCCx VSSx

WE_n

CLK i

DQS1_t VSSQ LPDDR2 DQ

G VSSCA CA7 CA6

-

ADQ12

DQ12

OE_n o,f

RE_n n,i

W/R_n i

CE_n DQS1_c DM1 VDDQ LPDDR2 CA

H VDDCA CA5

-

ADQ13

DQ13

-

ADQ6

DQ11

-

ADQ4

DQ9

Vref(DQ) VDD2 Power

J VDD2 Vref(CA) VSS

-

ADQ14

DQ14

-

ADQ7

DQ10

-

ADQ5

DQ8

DQS0_c DM0 VDD1 Ground

K CK_t CK_c

-

ADQ15

DQ15

VSSx VCCx DQS0_t VDDQ Do Not Use/NC/No Ball

L CS0_n CS1_n CS2_n DQ7 DQ6 VSSQ ZQ

M CA4 CA3 DQ5 VDDQ Clock

N VDDCA CA2 CA1 CKE0

AVD_n o

ADV_n f

ALE n,i

-

INT o

WP_n f,n,i

DQ3 DQ2 VSSQ

P NC VSSCA CA0 CKE2 CKE1

VACC

VPP

DQ0 DQ1 DQ4 VSSQ NC

R NC NC VSS VDD2 VDD1 VSS VDD2 VSS VDDQ NC NC

Ball eMMC (e)

OneNAND (o)

AAD NOR (f)

NAND (n)

NAND

DDR (i)

- DAT[7:0] ADQ[15:0] DQ[15:0] DQ[15:0]

C5 CLK CLK - DQS

C6 CMD RDY / WAIT R/B_n R/B_n

C7 RST_n RP_n/RST_n CLE CLE

F7 - WE_n WE_n WE_n, CLK

G6 - OE_n RE_n RE_n, W/R_n

G7 - CE_n CE_n CE_n

N6 - AVD_n/AVD_n ALE ALE

N7 - INT / WP_n WP_n WP_n

VSSx/VCCx represents common Flash VSS/VCC

JEDEC Standard No. 209-2F

Page 12

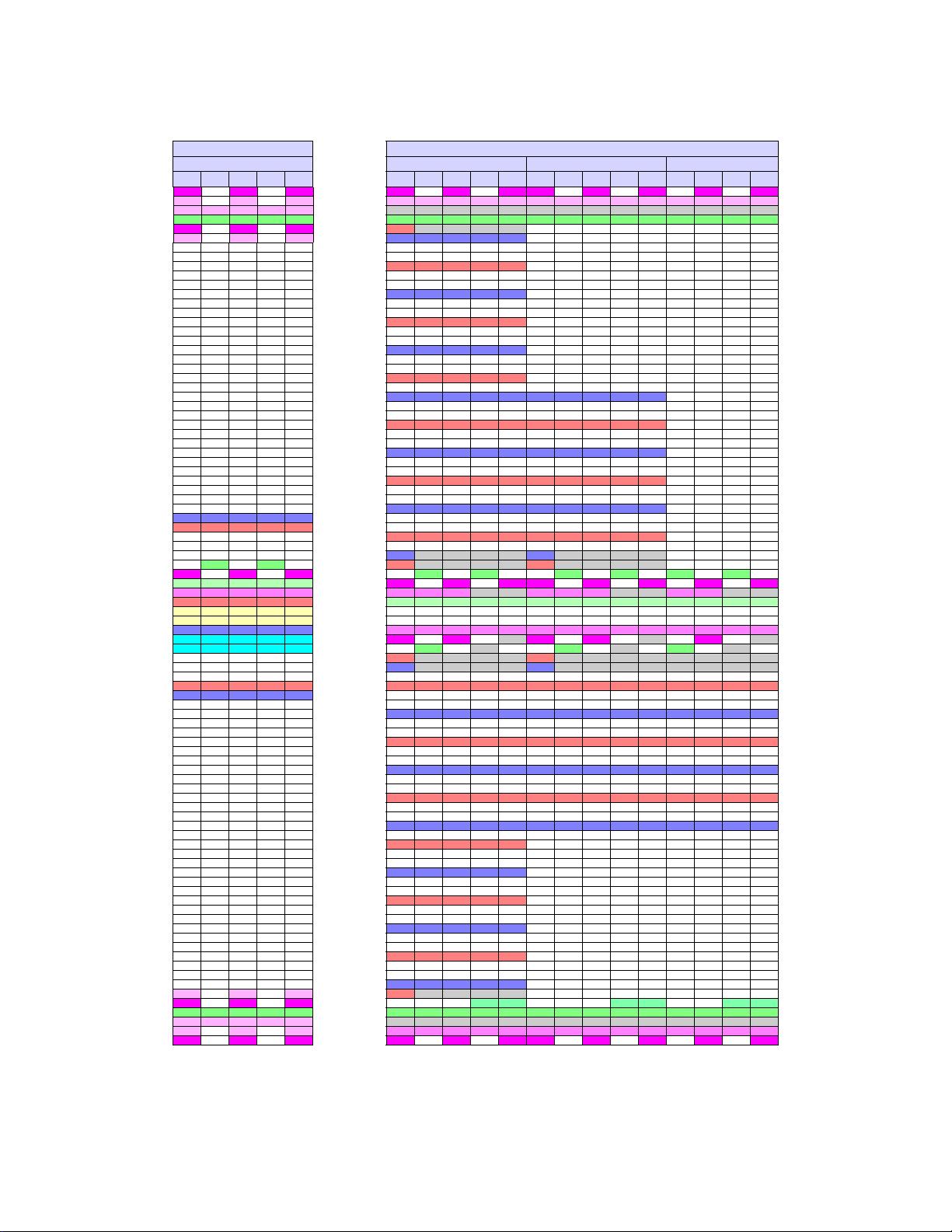

2.11 LPDDR2 Pad Sequence

NOTE 1 Pads with (*1) are optional.

NOTE 2 Ordering of DQ bits shall be maintained in the system, including within the package and on the PCB.

DQ byte swapping and DQ bit Swapping are not allowed in the system.

NOTE 3 CA pads and DQ pads shall be separated on opposite sides of die from top of silicon view.

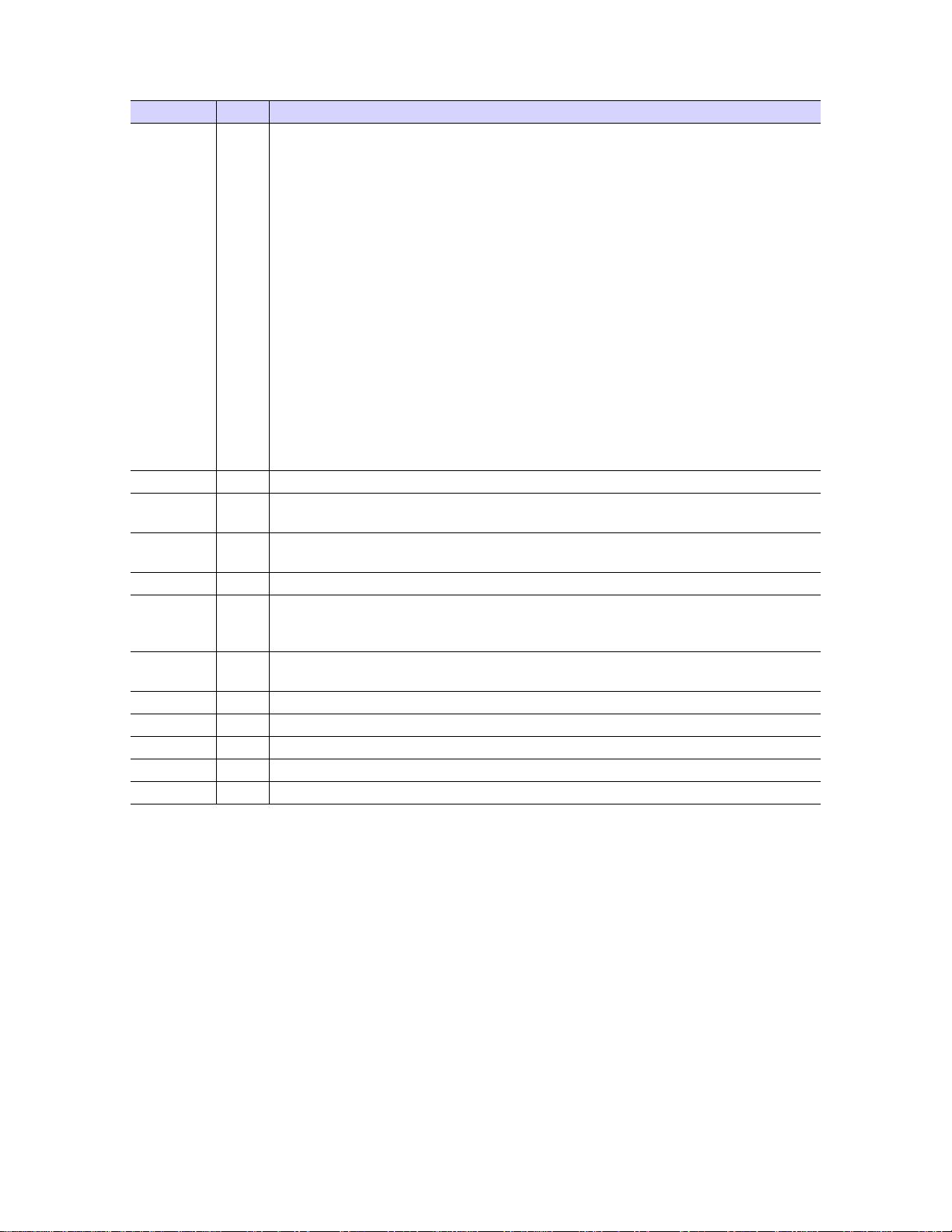

Table 1 — LPDDR2 Pad Sequence

CA Pad Sequence DQ Pad Sequence

x32 x16 x8

S4 S2A S2B N-A N-B S4 S2A S2B N-A N-B S4 S2A S2B N-A N-B S2A S2B N-A N-B

VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1

VDD2 VDD2 VDD2 VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VSS VSS VSS VSSQ VSSQ VSSQ VSSQ VSSQ

DQ31 DQ31 DQ31 DQ31 DQ31

DQ30 DQ30 DQ30 DQ30 DQ30

VDDQ VDDQ VDDQ VDDQ VDDQ

DQ29 DQ29 DQ29 DQ29 DQ29

DQ28 DQ28 DQ28 DQ28 DQ28

VSSQ VSSQ VSSQ VSSQ VSSQ

DQ27 DQ27 DQ27 DQ27 DQ27

DQ26 DQ26 DQ26 DQ26 DQ26

VDDQ VDDQ VDDQ VDDQ VDDQ

DQ25 DQ25 DQ25 DQ25 DQ25

DQ24 DQ24 DQ24 DQ24 DQ24

VSSQ VSSQ VSSQ VSSQ VSSQ

DQS3_t DQS3_t DQS3_t DQS3_t DQS3_t

DQS3_c DQS3_c DQS3_c DQS3_c DQS3_c

VDDQ VDDQ VDDQ VDDQ VDDQ

DM3 DM3 DM3 DM3 DM3

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

DQ15 DQ15 DQ15 DQ15 DQ15 DQ15 DQ15 DQ15 DQ15 DQ15

DQ14 DQ14 DQ14 DQ14 DQ14 DQ14 DQ14 DQ14 DQ14 DQ14

VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

DQ13 DQ13 DQ13 DQ13 DQ13 DQ13 DQ13 DQ13 DQ13 DQ13

DQ12 DQ12 DQ12 DQ12 DQ12 DQ12 DQ12 DQ12 DQ12 DQ12

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

DQ11 DQ11 DQ11 DQ11 DQ11 DQ11 DQ11 DQ11 DQ11 DQ11

DQ10 DQ10 DQ10 DQ10 DQ10 DQ10 DQ10 DQ10 DQ10 DQ10

VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

ZQ ZQ ZQ DQ9 DQ9 DQ9 DQ9 DQ9 DQ9 DQ9 DQ9 DQ9 DQ9

CA9 CA9 CA9 CA9 CA9 DQ8 DQ8 DQ8 DQ8 DQ8 DQ8 DQ8 DQ8 DQ8 DQ8

CA8 CA8 CA8 CA8 CA8

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

VSSCA VSSCA VSSCA VSSCA VSSCA DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t DQS1_t

VDDCA VDDCA VDDCA VDDCA VDDCA DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c DQS1_c

CA7 CA7 CA7 CA7 CA7

VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

CA6 CA6 CA6 CA6 CA6 DM1 DM1 DM1 DM1 DM1 DM1 DM1 DM1 DM1 DM1

CA5 CA5 CA5 CA5 CA5

VSSQ VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VDD1 VDD1 VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDD2 VDD2 VDD2 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1

Vref(CA) Vref(CA) Vref(CA) Vref(CA) Vref(CA) VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2

VSS VSS VSS VSS VSS VSS VSS VSS VSS

*1

VSS

*1

VSS VSS VSS VSS

*1

VSS

*1

VSS VSS VSS

*1

VSS

VDDCA VDDCA VDDCA VDDCA VDDCA Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ) Vref(DQ)

CK_c CK_c CK_c CK_c CK_c

CK_t CK_t CK_t CK_t CK_t

VSSCA VSSCA VSSCA VSSCA VSSCA VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

CKE CKE CKE CKE CKE VDD2 VDD2 VDD2

*1

VDD2 VDD2 VDD2

*1

VDD2 VDD2

*1

CS_N CS_N CS_N CS_N CS_N VDD1 VDD1

*1

VDD1 VDD1

*1

VDD1 VDD1

*1

CA4 CA4 CA4 CA4 CA4 VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

CA3 CA3 CA3 CA3 CA3 VSSQ VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

VSSQ

*1

CA2 CA2 CA2 CA2 CA2 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0 DM0

VDDCA VDDCA VDDCA VDDCA VDDCA VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

VSSCA VSSCA VSSCA VSSCA VSSCA DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c DQS0_c

CA1 CA1 CA1 CA1 CA1 DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t DQS0_t

CA0 CA0 CA0 CA0 CA0

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7 DQ7

DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6 DQ6

VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5 DQ5

DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4 DQ4

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3 DQ3

DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2 DQ2

VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1 DQ1

DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0 DQ0

VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ VSSQ

DM2 DM2 DM2 DM2 DM2

VDDQ VDDQ VDDQ VDDQ VDDQ

DQS2_c DQS2_c DQS2_c DQS2_c DQS2_c

DQS2_t DQS2_t DQS2_t DQS2_t DQS2_t

VSSQ VSSQ VSSQ VSSQ VSSQ

DQ23 DQ23 DQ23 DQ23 DQ23

DQ22 DQ22 DQ22 DQ22 DQ22

VDDQ VDDQ VDDQ VDDQ VDDQ

DQ21 DQ21 DQ21 DQ21 DQ21

DQ20 DQ20 DQ20 DQ20 DQ20

VSSQ VSSQ VSSQ VSSQ VSSQ

DQ19 DQ19 DQ19 DQ19 DQ19

DQ18 DQ18 DQ18 DQ18 DQ18

VDDQ VDDQ VDDQ VDDQ VDDQ

DQ17 DQ17 DQ17 DQ17 DQ17

DQ16 DQ16 DQ16 DQ16 DQ16

VSSQ VSSQ VSSQ VSSQ VSSQ

VSS VSS VSS VDDQ VDDQ

*1

VDDQ

*1

VDDQ

*1

VDDQ

*1

VDD2 VDD2 VDD2 VACC VACC VACC VACC VACC VACC

VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1 VDD1

VSS VSS VSS VSS VSS VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS

*1

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2 VDD2

JEDEC Standard No. 209-2F

Page 13

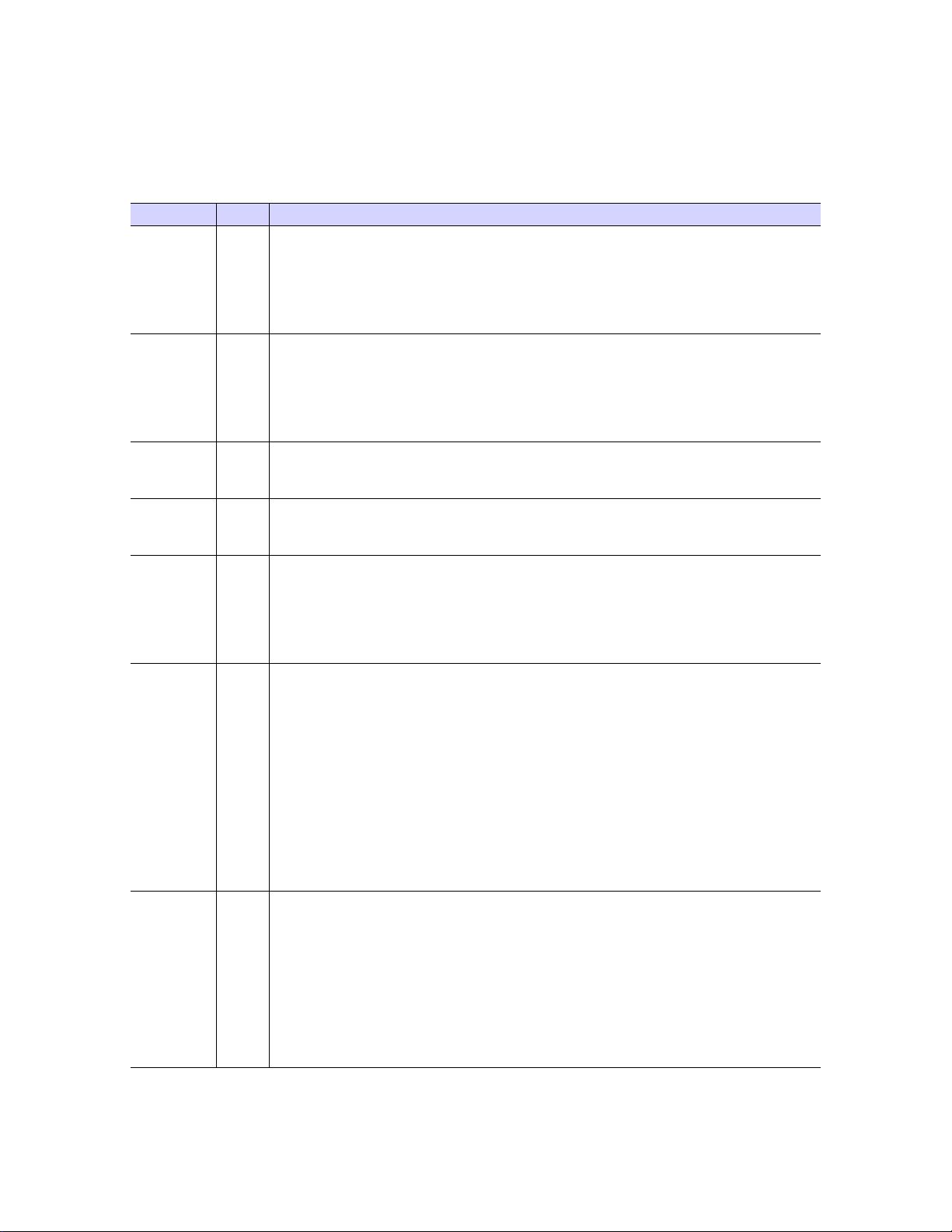

2.12 Input/output functional description

2.12.1 Pad Definition and Description

Table 2 — Pad Definition and Description

Name Type Description

CK_t, CK_c Input Clock: CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA

inputs are sampled on both positive and negative edge of CK_t. Single Data Rate (SDR)

inputs, CS_n and CKE, are sampled at the positive Clock edge.

Clock is defined as the differential pair, CK_t and CK_c. The positive Clock edge is

defined by the crosspoint of a rising CK_t and a falling CK_c. The negative Clock edge is

defined by the crosspoint of a falling CK_t and a rising CK_c.

CKE Input Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and

therefore device input buffers and output drivers. Power savings modes are entered and

exited through CKE transitions.

CKE is considered part of the command code. See Table 60 for command code

descriptions.

CKE is sampled at the positive Clock edge.

CS_n Input Chip Select: CS_n is considered part of the command code. See Table 60 for command

code descriptions.

CS_n is sampled at the positive Clock edge.

CA0 - CA9 Input DDR Command/Address Inputs: Uni-directional command/address bus inputs.

CA is considered part of the command code. See Table 6 0 for command code

descriptions.

DQ0-DQ7

(x8)

DQ0 - DQ15

(x16)

DQ0 - DQ31

(x32)

I/O Data Inputs/Output: Bi-directional data bus

DQS0_t,

DQS0_c

(x8)

DQS0_t,

DQS0_c,

DQS1_t,

DQS1_c

(x16)

DQS0_t -

DQS3_t,

DQS0_c -

DQS3_c

(x32)

I/O Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for

read and write data) and differential (DQS_t and DQS_c). It is output with read data and

input with write data. DQS_t is edge-aligned to read data and centered with write data.

For x8, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7.

For x16, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7; DQS1_t and

DQS1_c to the data on DQ8 - DQ15.

For x32 DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7, DQS1_t and

DQS1_c to the data on DQ8 - DQ15, DQS2_t and DQS2_c to the data on DQ16 - DQ23,

DQS3_t and DQS3_c to the data on DQ24 - DQ31.

DM0

(x8)

DM0-DM1

(x16)

DM0 - DM3

(x32)

Input Input Data Mask: For LPDDR2 devices that do not support the DNV feature, DM is the

input mask signal for write data. Input data is masked when DM is sampled HIGH

coincident with that input data during a Write access. DM is sampled on both edges of

DQS_t. Although DM is for input only, the DM loading shall match the DQ and DQS_t (or

DQS_c).

DM0 is the input data mask signal for the data on DQ0-7.

For x16 and x32 devices, DM1 is the input data mask signal for the data on DQ8-15.

For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is

the input data mask signal for the data on DQ24-31.

JEDEC Standard No. 209-2F

Page 14

NOTE 1 Data includes DQ and DM.

DM0/DNV0

(x8)

DM0/DNV0-

DM1/DNV1

(x16)

DM0/DNV0 -

DM3/DNV3

(x32)

I/0 Input Data Mask/Data Not Valid: For LPDDR2 devices that support the DNV feature,

DM/DNV is bidirectional (used for write and read data). It is output with read data, input

with write data. DM/DNV is the input mask signal for write data and is an output signal

validating a read burst.

For data write accesses:

Input data is masked when DM/DNV is sampled HIGH coincident with DQ input data

during a WRITE access.

DM0 is the input data mask signal for the data on DQ0-7.

For x16 and x32 devices, DM1 is the input data mask signal for the data on DQ8-15.

For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is

the input data mask signal for the data on DQ24-31.

For data read accesses:

See 5.4.2 for detailed description of DNV functionality.

DNV0, DNV1, DNV2, and DNV3 are driven coincident with output read data. DNV0,

DNV1, DNV2, and DNV3 are driven with the same value and shall be sampled with

DQS0, DQS1, DQS2, and DQS3 respectively.

The DM/DNV loading shall match the DQ and DQS_t (or DQS_c) loading.

V

DD1

Supply Core Power Supply 1: Core power supply for LPDDR2-N and LPDDR2-SX devices.

V

DD2

Supply Core Power Supply 2: Core power supply for LPDDR2-S2B, LPDDR2-S4 and

LPDDR2-N-B devices.

V

DDCA

Supply Input Receiver Power Supply: Power supply for CA0-9, CKE, CS_n, CK_t, and CK_c

input buffers.

V

DDQ

Supply I/O Power Supply: Power supply for Data input/output buffers.

V

ACC

Supply NVM Acceleration Supply: NVM device specific embedded operation acceleration.

V

ACC

enables some NVM device specific functionality. When not used for NVM device

specific functionality, V

ACC

shall be driven to a level of V

DD1

.

V

REF(CA)

Supply Reference Voltage for CA Command and Control Input Receiver: Reference voltage

for all CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.

V

REF(DQ)

Supply Reference Voltage for DQ Input Receiver: Reference voltage for all Data input buffers.

V

SS

Supply Ground

V

SSCA

Supply Ground for Input Receivers

V

SSQ

Supply I/O Ground

ZQ I/O Reference Pin for Output Drive Strength Calibration

Name Type Description

剩余283页未读,继续阅读

huzhao87

- 粉丝: 0

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 隐私数据清洗工具Java代码实践教程

- UML与.NET设计模式详细教程

- 多技术领域综合企业官网开发源代码包及使用指南

- C++实现简易HTTP服务端及文件处理

- 深入解析iOS TextKit图文混排技术

- Android设备间Wifi文件传输功能的实现

- ExcellenceSoft热键工具:自定义Windows快捷操作

- Ubuntu上通过脚本安装Deezer Desktop非官方指南

- CAD2007安装教程与工具包下载指南

- 如何利用Box平台和API实现代码段示例

- 揭秘SSH项目源码:实用性强,助力开发高效

- ECSHOP仿68ecshop模板开发中心:适用于2.7.3版本

- VS2012自定义图标教程与技巧

- Android新库Quiet:利用扬声器实现数据传递

- Delphi实现HTTP断点续传下载技术源码解析

- 实时情绪分析助力品牌提升与趋势追踪:交互式Web应用程序

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功