DesignCompiler综合指南:从原理到实践

需积分: 48 182 浏览量

更新于2024-07-15

25

收藏 3.47MB PDF 举报

"DesignCompiler中文guide手册.pdf"

DesignCompiler是由Synopsys公司提供的一个核心电路综合工具,主要用于将高级语言描述的电路(如HDL:硬件描述语言)转换为基于特定工艺库的门级网表。这个过程是集成电路设计前端流程的关键步骤,被称为综合。

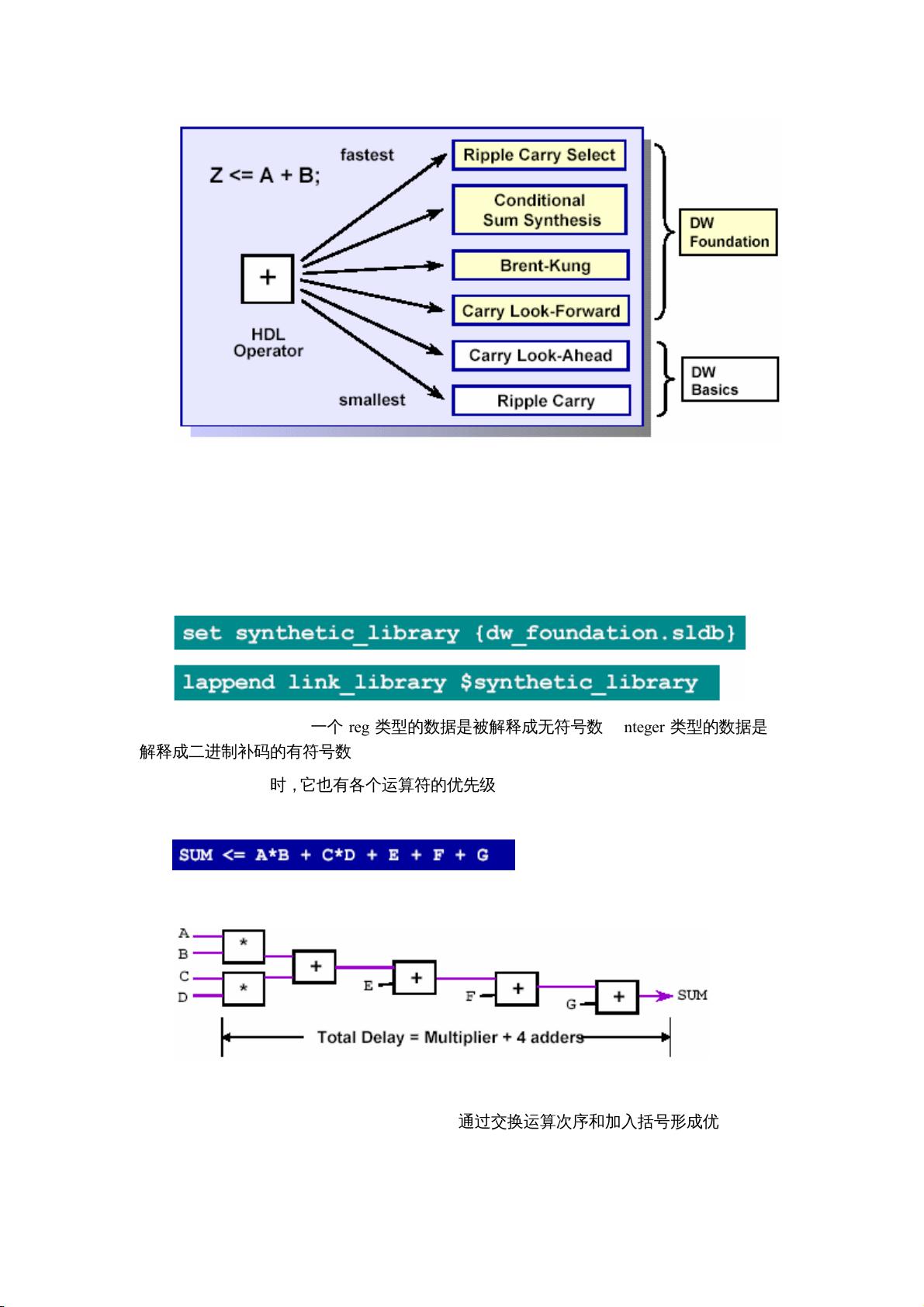

综合是一个复杂的设计流程,它涉及将行为描述或RTL级(寄存器传输级)电路转换为实际的门级实现。设计者可以使用HDL来描述电路的功能,但并不需要关心具体的硬件实现细节。综合工具,如DesignCompiler,会自动完成这个转换,并进行优化,以满足速度、面积和功耗等设计约束。

1. 综合的三个主要阶段:

- 转换(Translation):将HDL代码转换为与工艺无关的RTL级网表,这是一个逻辑表示,不依赖于具体的制造技术。

- 映射(Mapping):根据预定义的工艺库,将RTL级网表映射到实际的门级元素,如与门、或门、非门等。

- 优化(Optimization):在这个阶段,综合工具会根据设计者设定的约束条件(如最大延迟、最小面积等),对门级网表进行调整和改进,以达到最佳性能。

2. 设计的抽象层次:

- 行为级:最高层次的描述,关注的是系统的功能和行为,不涉及具体的实现细节。

- RTL级:次高层次,描述了数据流和控制流,但仍保持一定的抽象,不直接映射到硬件元素。

- 逻辑级:较低层次,设计用布尔逻辑表达,包括触发器和锁存器等基本组件的实例化。

3. 不同层次的综合:

- 逻辑级综合:设计以布尔等式形式表示,综合后可以直接得到较为接近最终电路的网表。

- RTL级综合:在RTL级,电路的数学运算和行为通过HDL特定的语法描述,这比逻辑级综合提供了更多的灵活性和优化机会,但不直接对应于硬件元素。

DesignCompiler的优势在于它能够处理这些复杂的转换和优化任务,使得设计者可以专注于设计本身,而不必深入到硬件的底层细节。通过熟练运用DesignCompiler,设计师可以更有效地实现高性能、低功耗和小面积的集成电路设计。

534 浏览量

1182 浏览量

138 浏览量

161 浏览量

327 浏览量

536 浏览量

1099 浏览量