2019年Verilog设计:数字系统作业解析

需积分: 0 189 浏览量

更新于2024-06-30

收藏 2.98MB PDF 举报

"该资源包含了2019年秋季学期的数字系统设计作业,主要涉及Verilog编程语言的使用,包括波形生成和8:3编码器的设计与测试。"

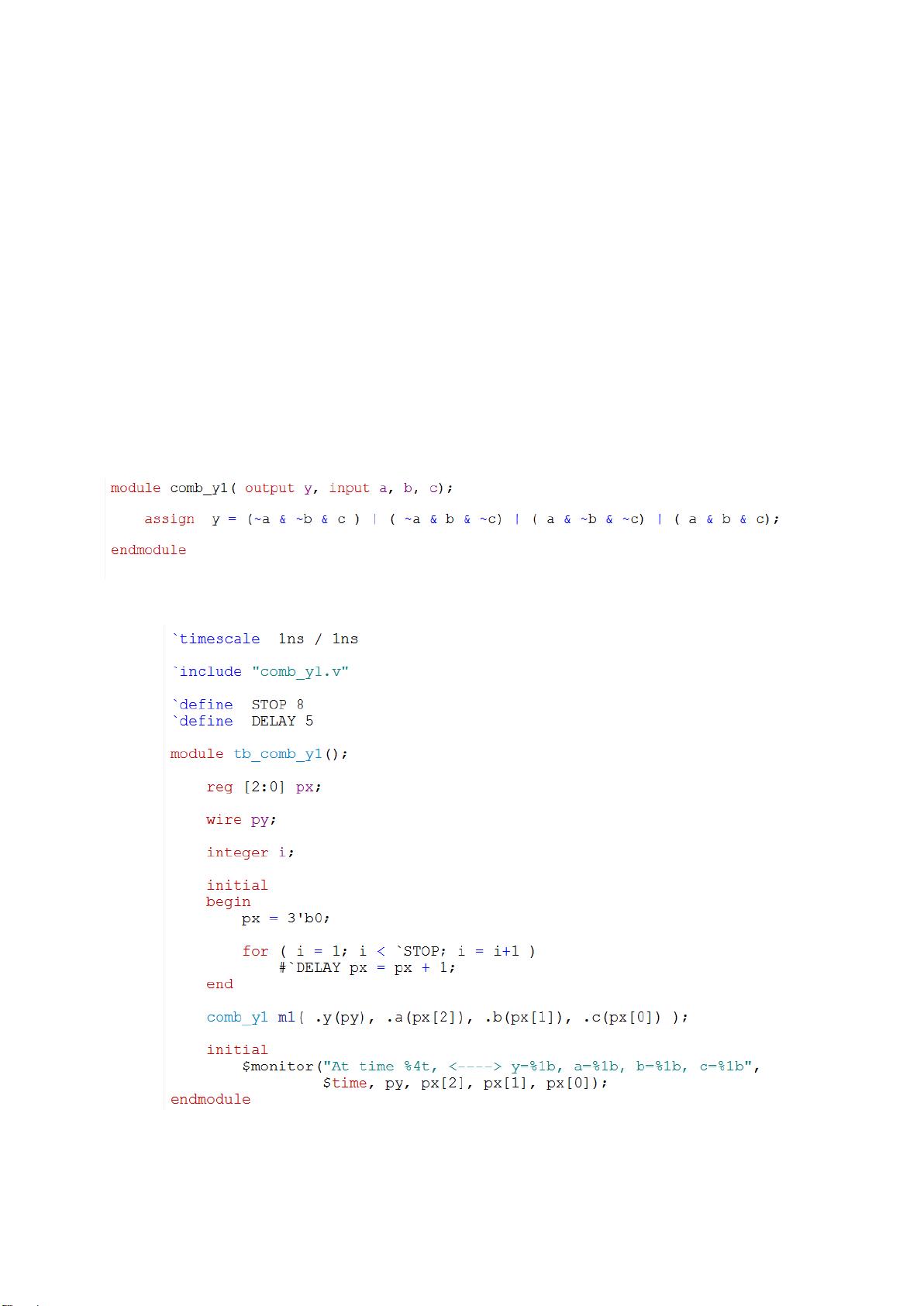

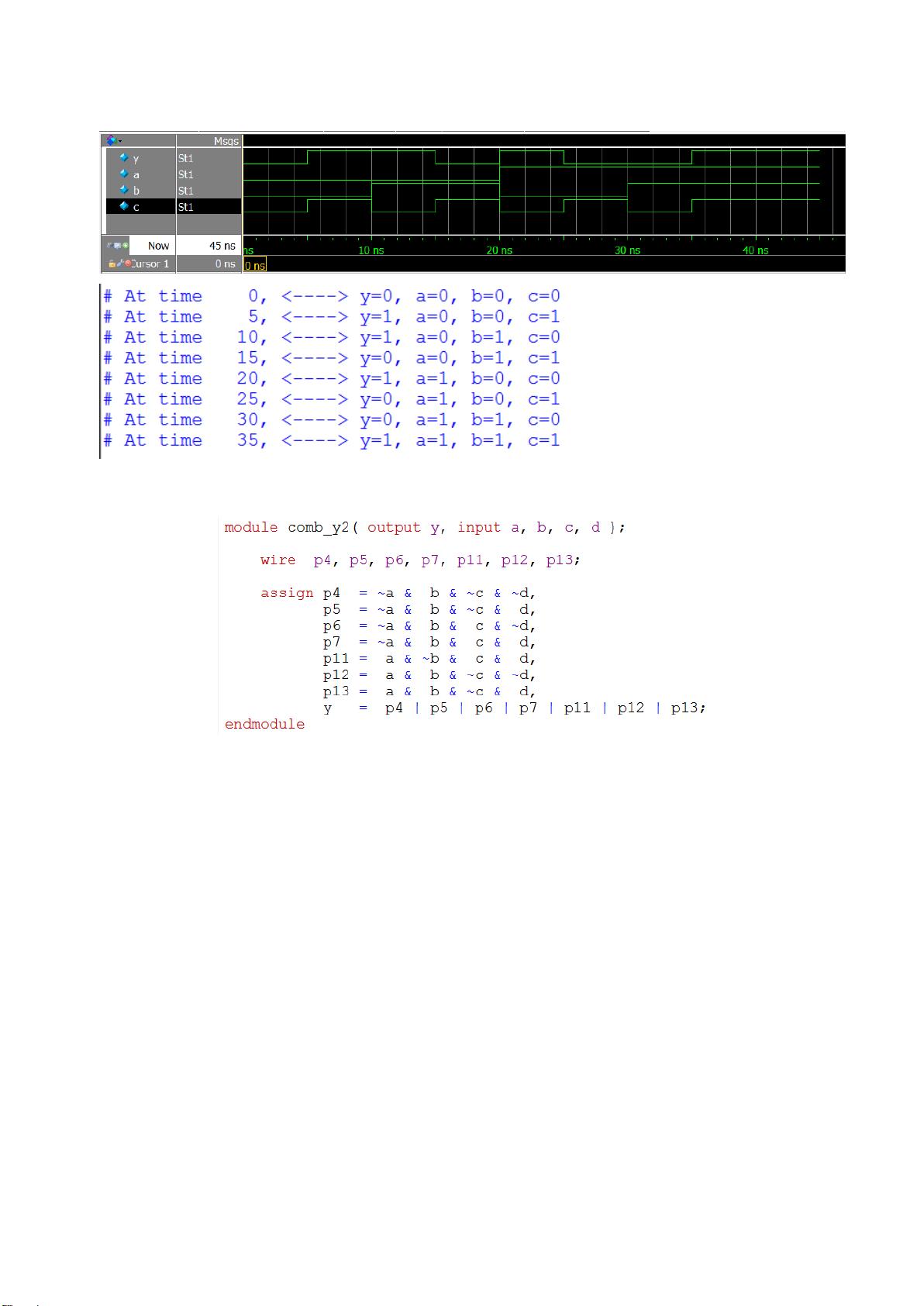

在数字系统设计中,Verilog是一种广泛使用的硬件描述语言,用于描述数字逻辑系统的功能和行为。在这份作业中,有两个主要部分:

第一部分是2.1,要求设计一个Verilog模块以产生特定的波形。波形图并未直接给出,但从描述中可以理解,波形可能包含一系列的高电平和低电平交替。模块名为`wavegen`,使用了`initial`语句来初始化波形序列,确保波形按照指定的时间单位和精度产生。`timescale`指令定义了时间单位和精度,这里是10ns时间和1ns精度。`initial`块中的代码通过改变`wave`信号的状态并在不同时间点暂停来创建波形。

第二部分是2.2,任务是设计一个8:3编码器,这是一个将8位输入转换为3位输出的电路。8:3编码器通常用于将多个输入线中的一个有效状态编码为一组较小的输出。在这个作业中,使用了`always`块和`case`结构来实现编码逻辑。当8位输入数据改变时,`case`语句会根据输入的二进制值设置3位输出`code`。真值表未直接给出,但可以通过题目描述和编码器的工作原理推断。同时,还需要设计一个测试平台`tb_encoder8x3`,用于对编码器模块进行仿真验证,这通常包括创建激励信号,连接输入和输出端口,并观察期望的输出结果。

在测试平台上,使用`timescale`指令设定仿真时间精度,并包含编码器模块的代码。`stim1`和`stim2`是用于模拟输入的寄存器,`p_data`连接到编码器的输入,而`p_code`连接到输出。通过改变`stim1`和`stim2`的值,可以仿真不同的输入情况,以检查编码器的正确性。

这份作业涵盖了数字系统设计的基础概念,包括Verilog编程、波形生成、逻辑编码以及模块的测试与验证,这些都是电子工程和计算机科学专业学生在进行毕业设计时常见的主题。

2022-08-08 上传

2022-08-04 上传

2020-07-21 上传

2019-05-26 上传

2019-12-10 上传

2020-04-26 上传

2019-12-10 上传

2019-12-10 上传

三山卡夫卡

- 粉丝: 26

- 资源: 323

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率