5.915GHz高稳定度锁相介质振荡器设计与研究

需积分: 9 115 浏览量

更新于2024-07-21

收藏 2.67MB PDF 举报

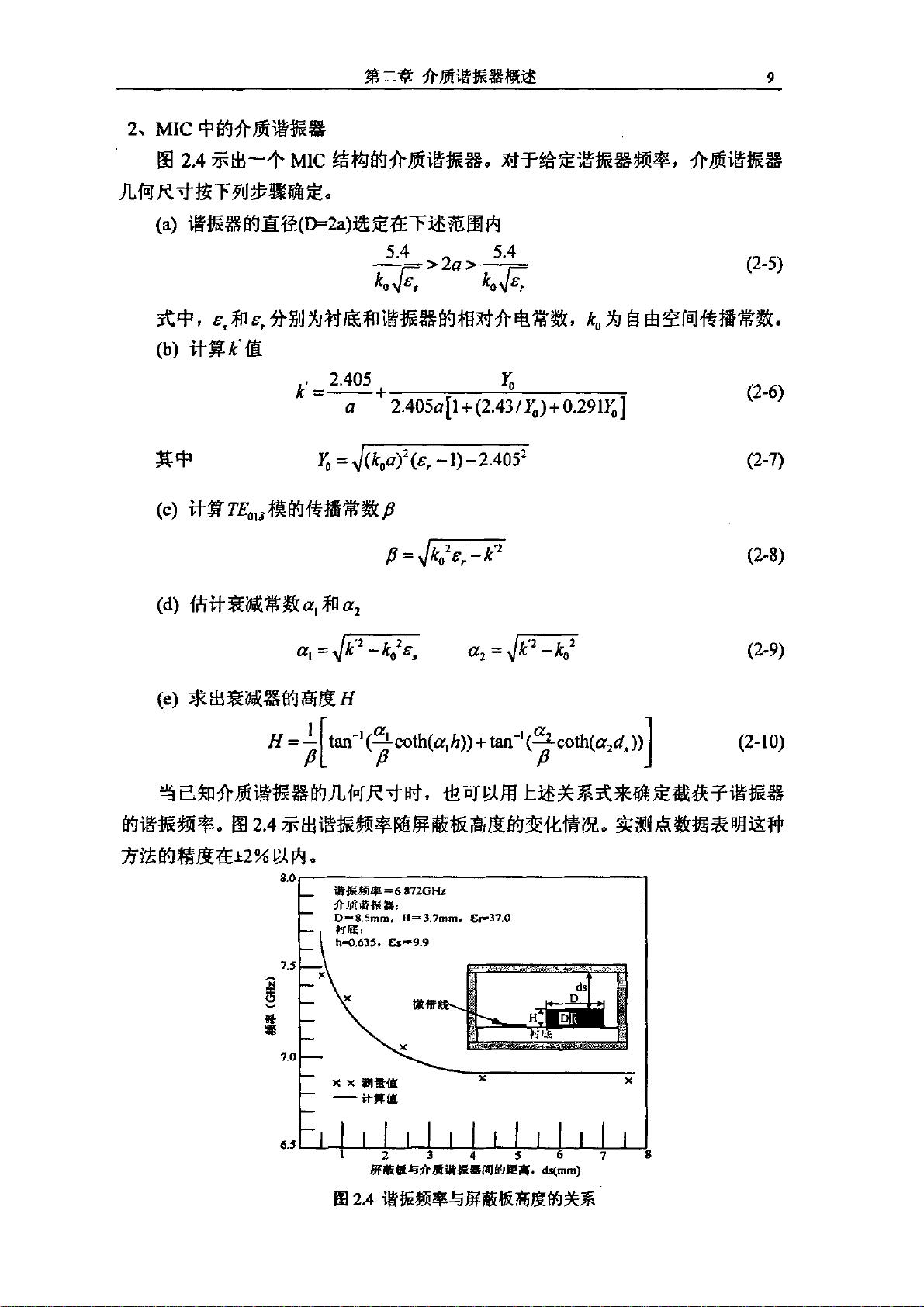

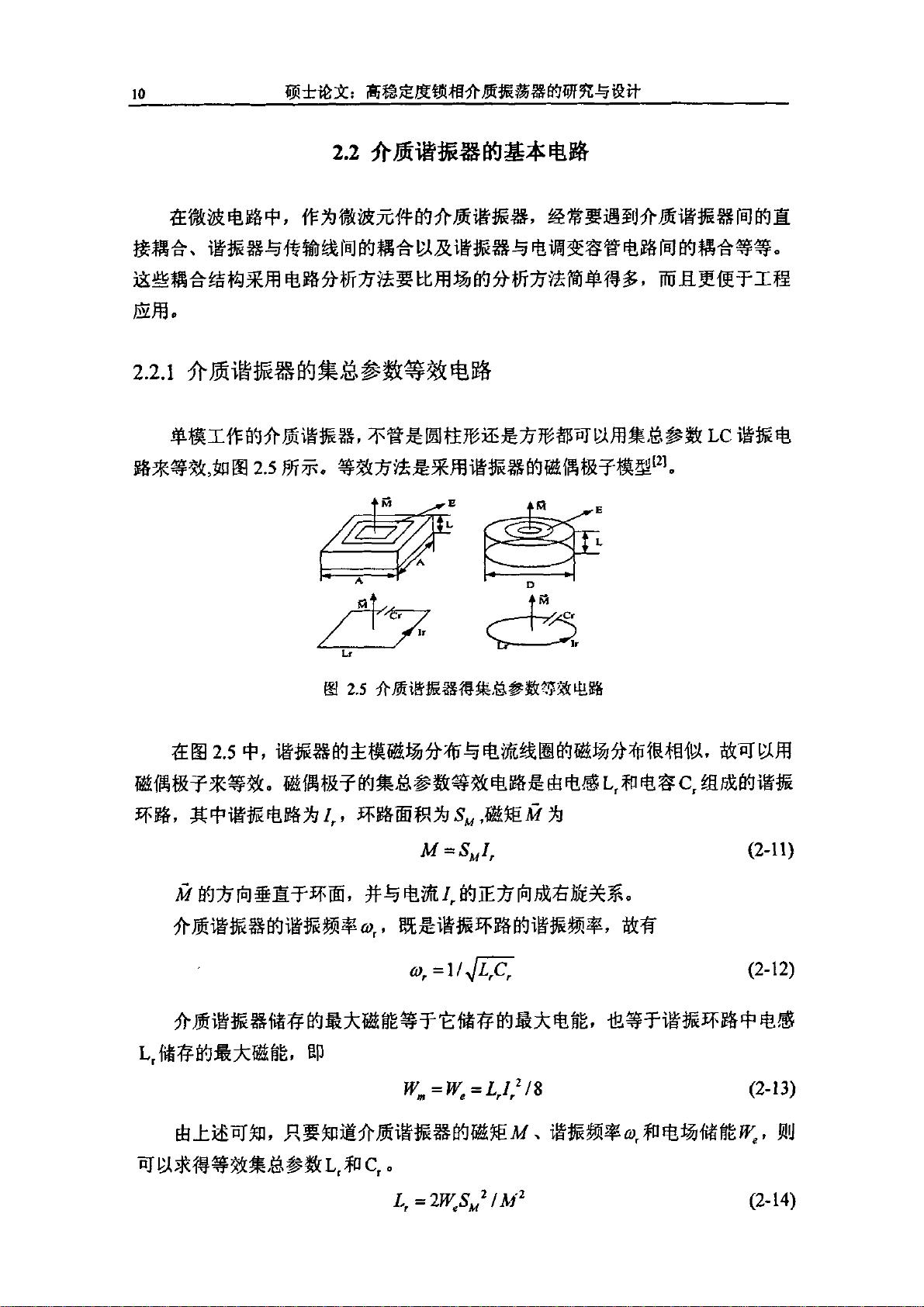

本文主要探讨了高稳定度锁相介质振荡器(PLDRO)的设计与研究,特别是在5.915GHz频率下的实现。文章涵盖了介质谐振器的基本特性和应用,反馈型介质振荡器的工作原理,锁相环(PLL)系统的基本理论,以及压控介质振荡器(DRVCO)和锁相环路的设计。

在现代无线通信领域,低相位噪声、高纯度频谱和高稳定性的本地振荡器(LO)对于移动通信、雷达、制导武器和电子对抗系统至关重要。介质谐振器压控振荡器(DRVCO)因其出色的噪声性能、频谱纯度和稳定性,被广泛应用在微波振荡源中。常见的DRVCO结构包括串联反馈型和并联反馈型,其中并联反馈型在相位噪声方面通常优于串联反馈型。

论文首先详细研究了介质谐振器的基础特性,包括其基本应用电路,并通过软件仿真介绍了三种介质谐振器建模方法,为后续的介质振荡器设计提供了理论支持。接着,作者深入探讨了几种不同电路结构的介质谐振器振荡器的工作原理,指出反馈型介质振荡器由砷化镓场效应管放大组件和包含介质谐振器的反馈回路构成,这种分离式设计有利于优化设计和研制。

在锁相环(PLL)系统理论部分,文章从时域和频域角度推导了系统相位模型和环路动态方程,结合控制系统理论研究了环路的稳定性和相位噪声性能,提供了环路带宽选择的图解分析方法,为确定锁相环的结构和带宽提供了依据。

论文的重点在于压控介质振荡器(DRVCO)设计,包括有源微波器件和电路结构的选择,以及直流偏置电路、负阻部件和完整电路的仿真设计。作者还详细介绍了锁相环路设计,特别是环路滤波器的设计,然后将锁相环路与DRVCO连接进行调试。

在实际调试过程中,作者发现测试结果与仿真结果存在显著差异,可能的原因包括:微带电路设计不理想,微带线尺寸误差过大,介质谐振器的谐振频率偏离目标值,DR的位置,金属谐振腔尺寸和调谐螺钉高度等对相位噪声的影响。

关键词:介质谐振器,介质振荡器,锁相环,高稳定度,低相位噪声

这篇论文全面深入地研究了高稳定度锁相介质振荡器的设计,对于相关领域的工程师和技术人员具有很高的参考价值。

2021-11-14 上传

272 浏览量

1042 浏览量

1959 浏览量

点击了解资源详情

118 浏览量

2010-01-26 上传

w13000

- 粉丝: 0

最新资源

- 久度免费文件代存系统 v1.0:全技术领域源码分享

- 深入解析caseyjpaul.github.io的HTML结构

- HTML5视频播放器的实现与应用

- SSD7练习9完整答案解析

- 迅捷PDF完美转PPT技术:深度识别PDF内容

- 批量截取子网页工具:Python源码分享与使用指南

- Kotlin4You: 探索设计模式与架构概念

- 古典风格茶园茶叶酿制企业网站模板

- 多功能轻量级jquery tab选项卡插件使用教程

- 实现快速增量更新的jar包解决方案

- RabbitMQ消息队列安装及应用实战教程

- 简化操作:一键脚本调用截图工具使用指南

- XSJ流量积算仪控制与数显功能介绍

- Android平台下的AES加密与解密技术应用研究

- Место-响应式单页网站的项目实践

- Android完整聊天客户端演示与实践