DesignCompiler教程:从入门到精通

"DesignCompiler经典教程提供了对Synopsys公司的ASIC综合器产品的深入理解和实践操作,适合初学者学习。教程涵盖了DesignCompiler (DC) 的基本概念、使用方法以及关键流程,旨在帮助用户掌握数字电路设计、约束施加、优化和同步电路的静态时序分析。”

在DesignCompiler(DC)这一高度优化的逻辑综合工具中,设计师可以将用硬件描述语言(如VHDL或Verilog)编写的RTL(Right-Hand Side)级别设计转换为门级网表。DC广泛应用于全球半导体行业,拥有众多半导体制造商和工艺库的支持,是Synopsys公司的旗舰产品,市场占有率高达91%。其核心功能是高效、快速地将设计转化为符合特定工艺库的优化电路,同时考虑了性能、面积和功耗等多个关键指标。

实验教程通常包括以下内容:

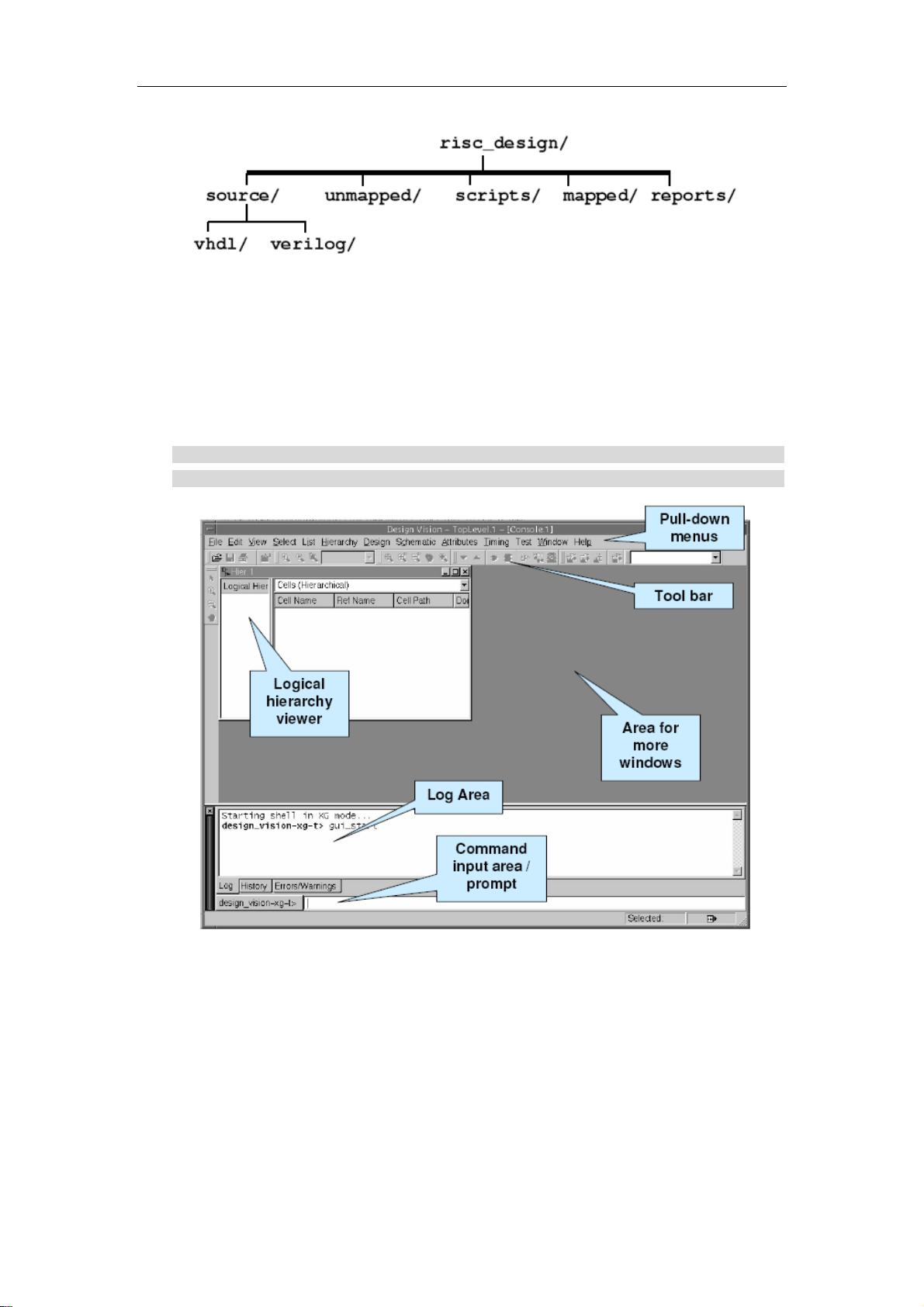

1. **Setup和Synthesis流程**:实验开始前,需要配置DesignCompiler的工作环境,可以选择命令行界面或图形用户界面(GUI,如DesignVision)。通过GUI模式,用户可以更直观地操作和理解综合过程。这个过程涉及8种设计对象,包括设计、单元、参考、端口、管脚、连线、时钟和库。

2. **设计对象理解**:

- **设计**:实现特定逻辑功能的电路,可能包含子设计。

- **单元**:设计中实例化的子设计。

- **参考**:单元的原型,即单元实例的基础。

- **端口**:设计的输入/输出接口。

- **管脚**:单元的输入/输出接口。

- **连线**:连接端口和管脚的线路。

- **时钟**:提供时钟信号的管脚或端口。

- **库**:包含与特定工艺相关的单元集合。

3. **.synopsys_dc.setup文件**:这是DesignCompiler的重要配置文件,用于设定工具的运行环境,包括指定库路径、编译选项等。

4. **约束管理**:在数字电路设计中,添加约束是至关重要的,这涉及到时钟周期、建立时间和保持时间等参数,确保电路满足时序要求。

5. **同步数字电路设计**:教程会教授如何处理时钟信号,理解同步电路的静态时序分析(STA),通过时序报告来评估和优化设计性能。

6. **综合优化**:DC通过多种技术,如逻辑等效替换、门级复用来优化逻辑结构,以达到性能、面积和速度的最佳平衡。

通过DesignCompiler实验,学习者能够逐步熟悉这些概念,掌握使用综合器进行数字电路设计的基本步骤,从而在实际工程中更加得心应手。

240 浏览量

644 浏览量

4150 浏览量

126 浏览量

223 浏览量

2007-11-06 上传

106 浏览量

abel_qiu

- 粉丝: 4

最新资源

- Windows 2000驱动开发全攻略:环境、PnP与内核模式详解

- 51单片机实现多功能时钟程序

- NS手册中文精译版:网络模拟与实践指南

- MSA2.0远程访问服务规划与设计指南

- S3C4510B平台下的uClinux入门与应用开发

- Oracle9i&10g数据库体系结构深度解析

- VC++实战指南:从基础到高级应用

- 电子商务基础与影响:从概念到未来发展

- 工作流技术详解:从概念到历史

- USB接口详解:连接、协议与拓扑结构

- 理解AT&T汇编语言格式与GCC内嵌汇编

- NRF9E5射频芯片驱动的无线耳机系统设计与优析

- OpenGL高级图形编程技术探索

- Linux ASM:入门与嵌入式优化的关键

- Ant入门教程:构建Java项目的利器

- C++编程规范与最佳实践