理解FPGA时序分析:TimeQuest与基本概念解析

需积分: 18 106 浏览量

更新于2024-07-28

收藏 1.47MB DOC 举报

"这篇文稿主要介绍了FPGA的时序分析,特别是针对TimeQuest工具的使用,摘自Quartus II Version 7.0 Handbook的相关章节。内容涵盖了时序分析的基础概念,包括基本单元如Cells、Pins、Nets、Ports、Clocks、Keepers和Nodes,以及时序分析的核心对象Edges和它们的分类。"

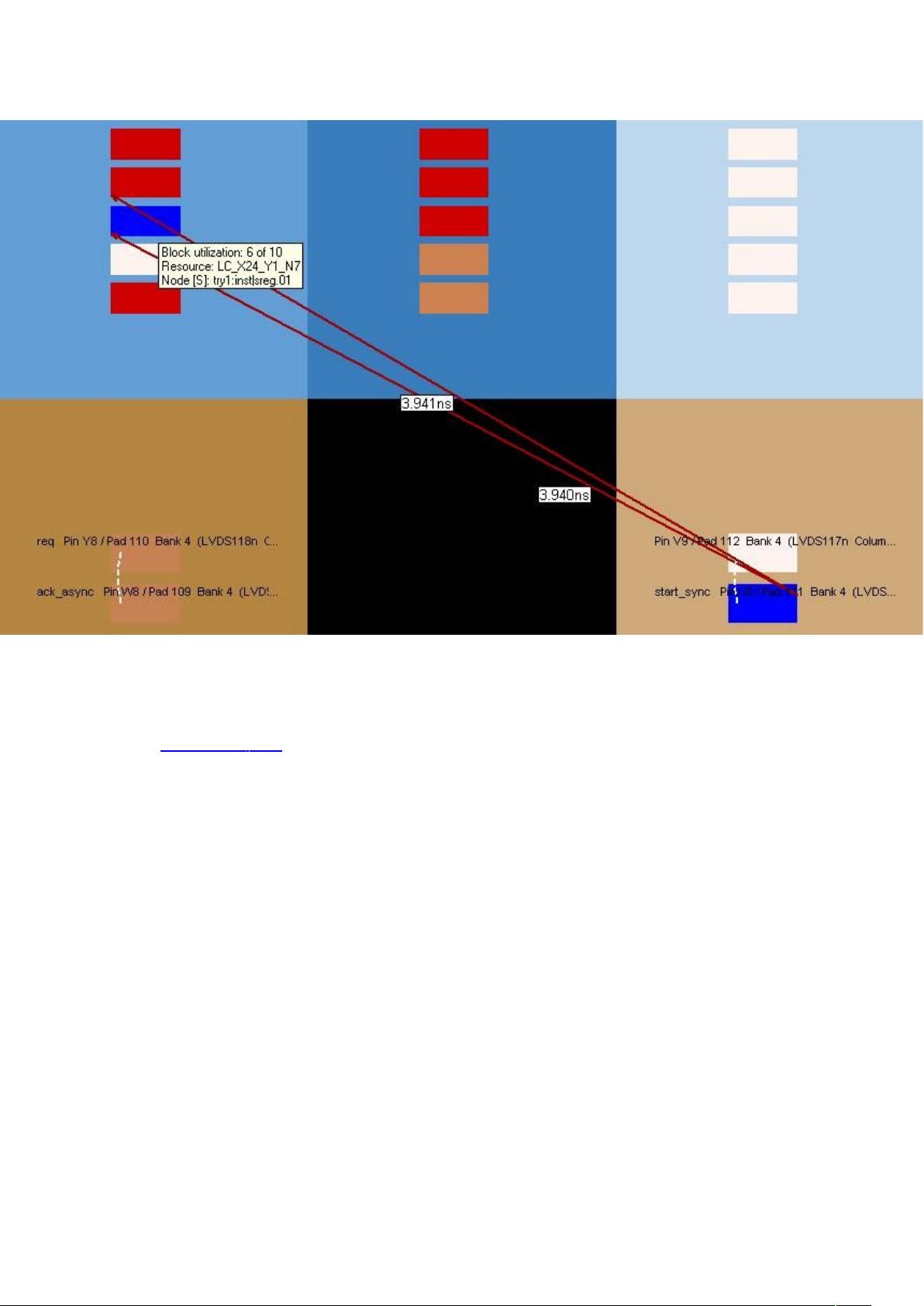

在FPGA设计中,时序分析是至关重要的一步,它关乎到设计能否在目标时钟速度下正确、稳定地工作。TimeQuest是一款强大的时序分析工具,它基于布局布线后的网表进行分析,确保设计满足预定的时序约束。

首先,文章提到的基本单元是时序分析的基础。Cells是FPGA中的基本逻辑单元,例如Altera设备中的逻辑元素(LE)。Pins是Cells的输入输出接口,但这里的Pins不包括实际器件的输入输出引脚,而是LE的内部接口。Nets则表示从一个Pin到另一个Pin的逻辑路径,虽然在相邻Cell间的连线不被视为独立的Net,但它代表了物理布线带来的延迟。

Ports指的是与器件引脚相连的顶层输入输出端口,而Clocks是指约束文件中定义的时钟信号,不仅限于时钟输入引脚。Keepers通常指的是Port和寄存器Cell,而Nodes则是一个更广泛的概念,可能包含上述各种类型的组合。

Edges是TimeQuest进行时序分析的关键元素,它们描述了信号在系统中的传输路径,包括Port-Pin、Pin-Pin和Pin-Port的连接。Edges分为三类:Clockpaths是从时钟源到寄存器的时钟输入,Data paths是从输入Port到寄存器数据输入的路径,还有其他非典型路径。

时序分析的目标是计算和验证这些路径上的延迟,确保在时钟周期内数据能正确地从一个寄存器传输到另一个。这涉及到建立时间(Setup Time)和保持时间(Hold Time)的检查,以防止数据在时钟边沿到来前未能稳定或者在时钟边沿后发生改变,导致错误。

通过理解这些基本概念,FPGA设计师可以有效地使用TimeQuest进行时序分析,优化设计性能,确保在实际硬件中实现预期的逻辑功能。在进行时序分析时,设计师还需要考虑工艺、电压和温度(PVT)条件的影响,以及可能的时序裕量(Timing Slack)和路径延迟。此外,合理的时序约束设置对于优化设计速度和提高可靠性至关重要。

523 浏览量

131 浏览量

2009-04-11 上传

2021-07-13 上传

1417 浏览量

236 浏览量

111 浏览量

shangfei1226

- 粉丝: 0

- 资源: 1

最新资源

- 新建文件夹,新建文件夹2,matlab

- -lab-07-conditionals

- InteractiveRomaniaMap

- jd-eclipse的2.0.rar

- login-assignment:登录分配

- yacc-dev.7z

- CSP-J CSP-S初赛模拟题_PDF(2020.10.01).rar

- 带有详细注释的 Redis 3.0 代码.zip

- Flask-miniproject

- 行业文档-设计装置-集罐输送平台的拨罐装置.zip

- oms-gateway

- VMware16.0.0.zip

- Medieval Online, Realistic MMOG-开源

- CSI2132_Project

- c8y-angular-polymer-boilerplate::alembic:实验累积量+ Angular +聚合物(Web组件)游乐场

- OA办公管理后台系统 BS系统 办公自动化管理 后台管理 - html.zip