FPGA实现的SPI自动发送模块:VHDL驱动的高效串行化技术

96 浏览量

更新于2024-08-30

收藏 205KB PDF 举报

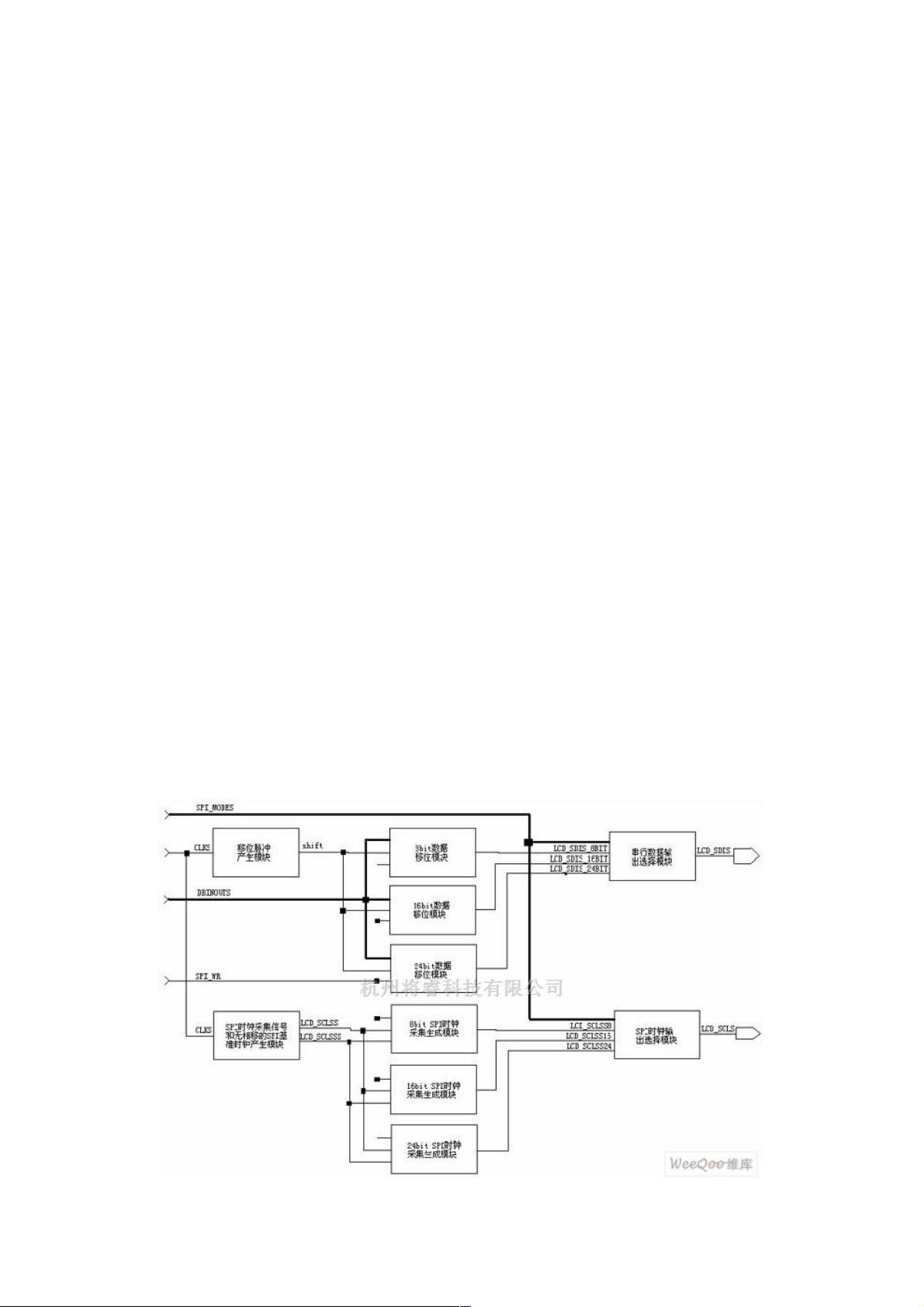

在EDA/PLD领域,FPGA设计中的SPI自动发送模块技术是一项实用且高效的技术,它允许用户利用可编程逻辑器件(FPGA)实现串行外设接口(SPI)的并行数据自动转换和发送。本文主要探讨了如何通过VHDL语言设计和实现这样一个模块,以支持不同位宽的数据传输,如8位、16位和24位。

首先,SPI接口因其灵活性和广泛的应用,包括在微控制器(MCU)和各种嵌入式系统中,通常会通过软件模拟或硬件模块进行通信。然而,当性能需求提升或特定硬件资源有限时,直接在FPGA上定制一个SPI发送模块就显得尤为重要。该模块的关键组成部分包括:

1. **串行数据输出选择模块**:根据输入的SPI_MODES信号(01代表8bit模式,10代表16bit模式,11代表24bit模式),这个模块负责根据设定的位宽选择相应的数据输出路径。

2. **移位脉冲产生模块**:生成同步的串行移位脉冲,确保数据在时钟周期内正确地按顺序传输。

3. **SPI时钟采集信号和无相移的SPI基准时钟产生模块**:用于控制传输时序,提供稳定且精确的时钟信号,确保数据传输的一致性和准确性。

4. **SPI时钟输出选择模块**:根据传输模式选择合适的时钟频率,如8bit、16bit或24bit时钟采集生成模块。

5. **位宽度相关的数据移位模块**:如8bit、16bit和24bit数据移位模块,分别对应不同位宽的数据处理。

操作流程相当直观:

- 用户通过SPI_MODES设置传输模式(如8bit、16bit或24bit)。

- 将待发送的并行数据写入DBINOUTS端口,对应于设定的位宽。

- 初始化SPI_WR信号为低电平,表示传输未开始。

- 当需要发送数据时,将SPI_WR置为高电平,触发数据的自动串行化并发送过程。

通过这种方式,FPGA设计者可以灵活地集成SPI自动发送功能到他们的系统中,提高系统的性能和定制化能力,尤其是在需要高度可配置和实时响应的应用场景中。VHDL作为硬件描述语言,使得这种自定义模块的设计和实现变得简洁易懂,同时也方便了后续的调试和优化。

2020-11-07 上传

2020-12-10 上传

2020-11-08 上传

2020-11-11 上传

2020-11-17 上传

2020-10-21 上传

2020-11-17 上传

2020-11-18 上传

2020-12-07 上传

weixin_38552083

- 粉丝: 7

- 资源: 887

最新资源

- addressable:Addressable是URI实现的替代实现,它是Ruby标准库的一部分。 它非常灵活,提供启发式解析,并且还为IRI和URI模板提供了广泛的支持

- canteenmanagement

- EnterpriseProject,java源码网,oa系统源码java

- messageboard

- API610标准在大型中高温浓硫酸液下泵设计中的应用.rar

- Sitio_Web_Blog_Cafe-Mobile_First

- fe-record-websource:前端记录资源导航的网页版原始码,使用react编写的静态页面

- Jake Peralta Theme-crx插件

- Javasourcecodequerysystem,java线程池源码,java酷狗

- subtlechat-vue:微言语聊天室是基于前初步分离,采用SpringBoot + Vue开发的网页版聊天室。这是项目的前端vue工程

- translations-app:已实现翻译的示例Web应用程序(react-i18next)

- 班主任工作计划和总结打包.rar

- lambdaUnzipper:AWS Lambda 的解压缩功能

- 异质检测

- Pervy Pastry Puffinator-crx插件

- shengyintupian,java源码阅读,企业java源码下载