ModelSim使用教程:从入门到模拟Verilog项目

需积分: 10 11 浏览量

更新于2024-07-29

收藏 2.62MB PDF 举报

项目配置文件,定义了编译库、仿真设置等信息。`.cr.mti`文件则是项目创建时自动生成的,包含了项目的相关信息。

2. 引进HDL Files

在"Add items to the Project"窗口中,你可以通过浏览找到你的Verilog源代码文件(如system.v, clkgen.v等),将它们添加到项目中。点击"Add"按钮,这些文件就会出现在Project标签页下。这一步是为了让ModelSim知道需要编译哪些设计文件。

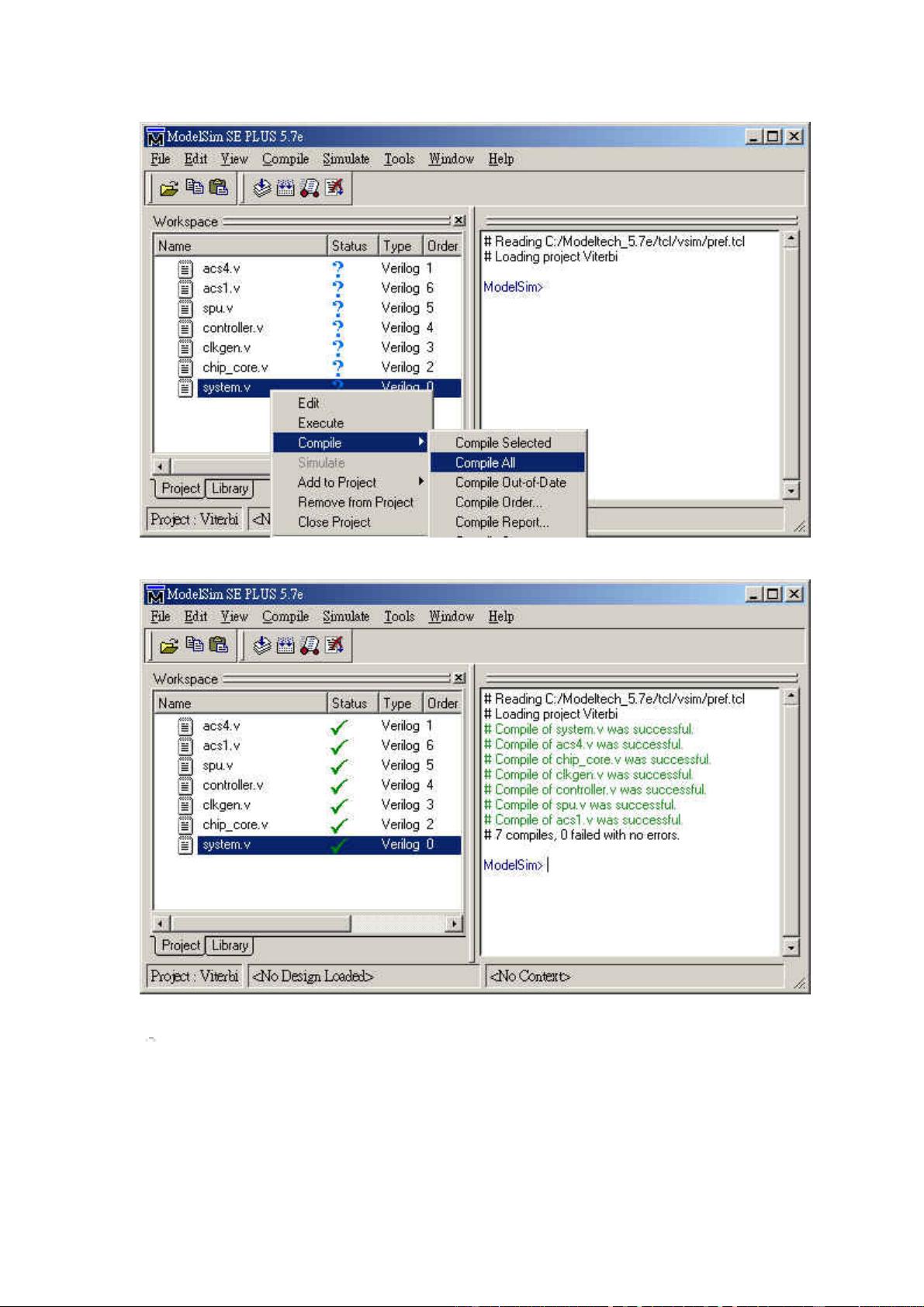

3. Compile

在添加了所有必要的HDL文件后,点击工具栏上的"Compile"或选择"Compile -> Compile All"来编译整个项目。编译过程中,ModelSim会检查语法错误、类型匹配等问题,并生成相应的仿真可执行文件。如果出现错误,ModelSim会在Output窗口中显示错误信息,需要根据这些信息进行调试和修复。

4. 模拟(Simulate / Loading and Run)

编译无误后,我们进入模拟阶段。首先,需要设置仿真时间范围,这可以通过在命令行输入`run <time>`来设定,其中<time>是仿真时间,通常以纳秒(ns)为单位。然后,你可以通过`add wave`命令添加想要观察的信号到波形窗口,以便在仿真运行时查看信号变化。最后,点击"Simulate"或者输入`run`命令开始仿真。

5. 使用ModelSim的其他功能

除了基本的操作,ModelSim还提供了丰富的调试工具,例如查看变量值(`display`命令)、设置断点、单步执行等。此外,ModelSim支持批处理模式,可以编写脚本来自动化编译和仿真过程,提高工作效率。

6. ModelSim的不同版本

ModelSim有多个版本,如PE (Professional Edition),LE (Lite Edition) 和SE (Standard Edition)。它们的主要区别在于功能的完整性和性能。PE版提供最全面的功能,包括高级调试工具和并行编译等;LE版则相对简化,适合个人学习使用;SE版则介于两者之间,满足基本的仿真需求。

7. 学习ModelSim的建议

为了更好地掌握ModelSim,建议从简单的Verilog或VHDL程序开始,逐步了解每个步骤。同时,熟悉ModelSim的命令行界面和图形用户界面,理解不同窗口(如Source、Waveform、Output等)的作用。多做实践,遇到问题时查阅官方文档或在线资源,这样能更快地提升使用技巧。

总结,ModelSim是一款强大的硬件描述语言(HDL)仿真器,广泛应用于数字系统设计验证。通过创建项目、引入源代码、编译和模拟,可以有效地验证和调试Verilog或VHDL设计。对于初学者,从简单的示例开始,逐步深入,结合不同版本的特点,可以更好地掌握这款工具。

2012-05-14 上传

2009-07-19 上传

2018-04-10 上传

2009-06-13 上传

2009-05-13 上传

2024-12-24 上传

2024-12-24 上传

rabbit883

- 粉丝: 1

- 资源: 8

最新资源

- <医学图像处理方向>_研究生_上海交通大学生物医学工程_课程期末大作业_合集

- DatagridViewTest.rar

- 角动画

- D1笔记代码(1).rar

- AMD-2.2.1-py3-none-any.whl.zip

- Gallina 4 Wordpress-开源

- sqlcipher-ktn-pod:将SQLCipher lib从Cocoapods包装到Kotlin Native

- net-snmp_shell_subagent

- WAB-FloatingTheme2:具有浮动纹理元素的 Web AppBuilder for ArcGIS(开发人员版)的自定义主题

- AE001V2

- 用GDI显示GIF动画图片VC源代码

- 吴恩达深度学习课程第一课第二周datasets和lr_utils

- AMQPStorm_Pool-1.0.1-py2.py3-none-any.whl.zip

- SGU DownloadScheduler-开源

- AMQPStorm-2.2.0-py2.py3-none-any.whl.zip

- EVC创建进程