Cadence IC5141 使用教程:原理图与Spectre仿真

需积分: 50 124 浏览量

更新于2024-07-26

1

收藏 2.84MB PDF 举报

"复件 ic5141使用教程.pdf"

本文档主要介绍了IC5141,这是一种全定制集成电路设计平台,特别适用于电子科学与技术领域的应用。文档由沈阳理工大学信息学院编纂,旨在教授如何使用Cadence公司的设计工具进行原理图输入和Spectre仿真。教程覆盖了从环境配置到具体设计步骤的详细过程。

首先,环境配置是使用IC5141平台的基础。在Linux系统中,用户需要编辑`.bashrc`文件,确保其中包含了指向Cadence软件安装路径、许可证文件、工作网表模式配置以及路径环境变量的设置。这些配置确保了工具的正常运行,并且指定了用于在线帮助的浏览器。

接着,为了开始设计工作,需要创建一个工作目录。教程中建议创建名为`student`的目录作为设计工作空间。在实际操作中,由于GPDK(通用工艺设计套件)通常位于不可写的固定目录,但在这里可以直接忽略这个步骤,专注于理解基础文件的生成。

Cadence的IC5141工具集包括了几个关键组件:

1. **Design Framework II**:这是一个集成的设计环境,提供了整个设计流程的框架。

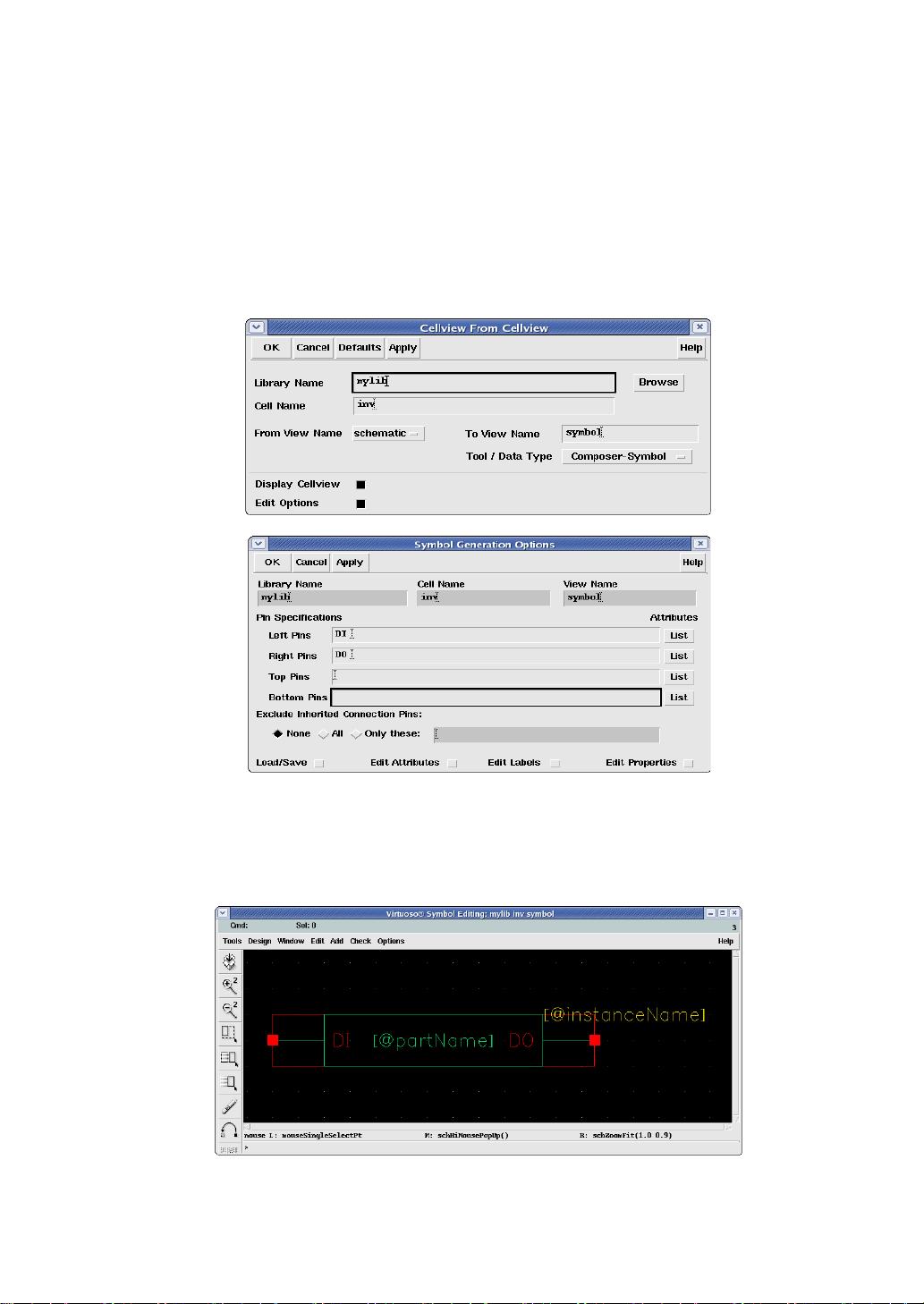

2. **Virtuoso Schematic Editor**:这是用于绘制和编辑电路原理图的工具,允许用户创建电路拓扑,并进行元件参数配置。

3. **Spectre**:这是一个强大的仿真工具,用于模拟电路行为,验证设计的正确性。

4. **Virtuoso Layout Editor**:用于版图设计,将电路原理图转化为物理布局。

5. **Diva**:这是一款物理验证工具,用于检查版图是否符合制造工艺规则。

在原理图编辑阶段,用户将使用Virtuoso Schematic Editor来绘制和编辑电路,选择适当的元件库,连接各部分,定义电路的输入和输出。一旦原理图完成,可以进行网表生成,这通常是通过编译原理图来实现的。

随后,Spectre仿真工具被用于验证设计的功能和性能。用户可以设定不同的仿真条件,如直流工作点分析、瞬态分析、频率响应分析等,以检查电路在不同工作状态下的表现。仿真结果通常以波形图的形式显示,便于分析电路行为。

版图编辑过程中,Virtuoso Layout Editor允许用户根据原理图创建物理布局。这个过程需要考虑工艺规则、电气规则以及设计的复杂性,以优化面积、功耗和性能。

在设计完成后,物理验证工具如Diva会检查版图的合规性,确保其满足工艺规则,没有潜在的制造问题。

IC5141使用教程涵盖了从电路设计到验证的全过程,对于理解和掌握集成电路设计流程具有重要的指导价值。通过这个教程,学习者能够熟练运用Cadence工具集进行全定制IC设计,并对电路行为进行深入分析。

2023-05-21 上传

2021-12-27 上传

111 浏览量

111 浏览量

2021-11-29 上传

2022-03-04 上传

闫少鹏

- 粉丝: 0

最新资源

- 《ASP.NET 4.5 高级编程第8版》深度解读与教程

- 探究MSCOMM控件在单文档中的兼容性问题

- 数值计算方法在复合材料影响分析中的应用

- Elm插件支持Snowpack项目:热模块重载功能

- C++实现跨平台静态网页服务器

- C#开发的ProgaWeatherHW气象信息处理软件

- Memory Analyzer工具:深入分析内存溢出问题

- C#实现文件批量递归修改后缀名工具

- Matlab模拟退火实现经济调度问题解决方案

- Qetch工具:无比例画布绘制时间序列数据查询

- 数据分析技术与应用:Dataanalys-master深入解析

- HyperV高级管理与优化使用手册

- MTK6513/6575智能机主板下载平台

- GooUploader:基于SpringMVC和Servlet的批量上传解决方案

- 掌握log4j.jar包的使用与授权指南

- 基础电脑维修知识全解析