VHDL语言:并行与顺序语句命令解析

PDF格式 | 114KB |

更新于2024-09-04

| 41 浏览量 | 举报

"VHDL语言中信号的不同形式设置,主要涉及并行同时语句命令和顺序语句命令。这两种语句在VHDL中扮演着核心角色,它们的运用直接影响到硬件描述的效率和清晰度。并行同时语句如直接设置语句、条件式信号设置和选择式信号设置,它们一次性执行多个命令,模拟硬件并行行为。而顺序语句如过程、判断比较、等待和描述选择,它们按照特定顺序依次执行,类似于传统编程语言的流程控制。

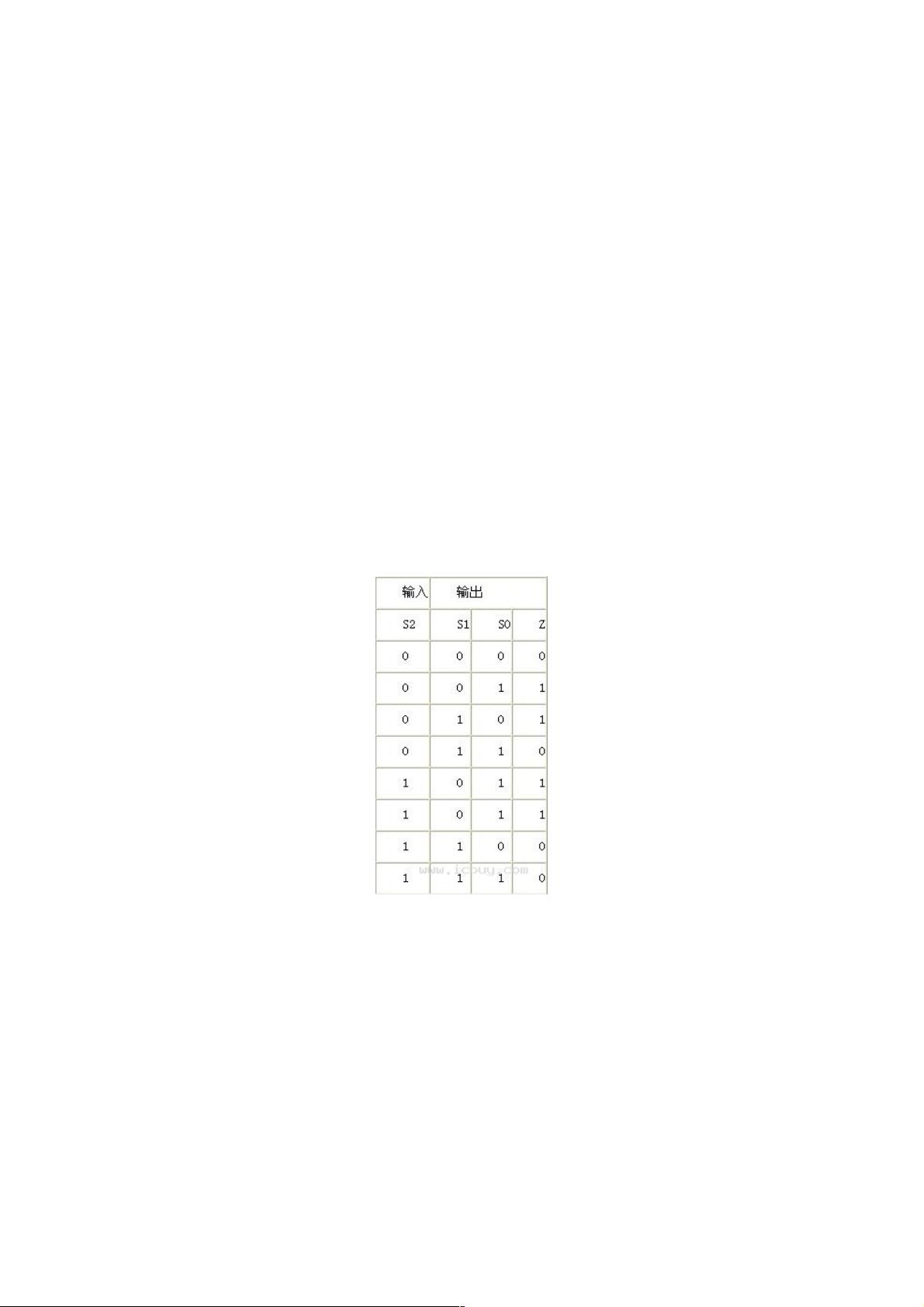

在实际编程中,例如设计一个偶同位产生器,理解并灵活运用这些语句至关重要。偶同位产生器的功能是根据输入的三位数据生成一位偶同位,使得总和的1的个数为偶数。在VHDL中,可以通过直接设置语句或者过程语句实现这种逻辑关系。例如:

```vhdl

entity parity_generator is

port(

data_in: in std_logic_vector(2 downto 0);

parity_out: out std_logic

);

end parity_generator;

architecture behavioral of parity_generator is

begin

parity_out <= '0' when (data_in'length downto 1) & data_in'length mod 2 = 0 else '1';

end behavioral;

```

在这个例子中,使用了并行同时语句`<=`来设置输出`parity_out`的值,根据输入数据的奇偶性决定其值。

然而,同样的功能也可以用过程语句来实现,这样可以更清楚地展示逻辑步骤:

```vhdl

architecture sequential of parity_generator is

begin

process(data_in)

begin

if (data_in'length downto 1) mod 2 = 0 then

parity_out <= '0';

else

parity_out <= '1';

end if;

end process;

end sequential;

```

在这个版本中,`process`语句模拟了从输入到输出的顺序逻辑过程,每个步骤按照代码的顺序依次执行。

无论是选择并行还是顺序语句,关键在于理解和适应VHDL语言的特性,根据设计需求选择最适合的实现方式。合理利用这两种语句形式,可以编写出高效、清晰的VHDL代码,从而提高硬件设计的可读性和可维护性。在实际项目中,还需要考虑综合工具的优化能力和具体平台的限制,合理安排设计结构。

相关推荐

weixin_38739919

- 粉丝: 4

- 资源: 903

最新资源

- RTKLIB.zip

- 电脑软件文件管理QTTabBar 资源管理器增强.rar

- 徽标商标许可:徽标商标许可

- 基于知识图谱的推荐算法-KGCN实现.zip

- AndroidUVCCamera:Android外接UVC相机库,致力于使用最简单的API、最清晰的代码逻辑实现预览和拍照功能

- Carmeter.rar

- jenkins-practice

- LAB_14_C6000_STARTER_audio_CACHE_C6000DSP_

- Jazz Tab-crx插件

- cleland.find-journals

- MybatisGenerator.zip

- OC Extension UTF8(日志UTF8内容转换成中文).zip

- 基于微信小程序的课表小程序.zip

- Challenges-front-end:在前端存储库中的参考存储库

- wics-web-workshop:WiCS 主办的 Web 应用程序研讨会的代码和说明!

- SimpsonsPass Password Generator-crx插件