优化RS(31,15)码生成多项式:FPGA实现的高效编码器设计

35 浏览量

更新于2024-08-31

2

收藏 681KB PDF 举报

RS编码器的优化设计及FPGA实现

本文主要探讨的是Reed-Solomon (RS) 编码器的设计及其在Field-Programmable Gate Array (FPGA) 上的实现。RS码是一种强大的纠错码,由Reed和Solomon在1960年提出,特别适用于纠正随机和突发错误,它属于多进制BCH码范畴,也是代数几何码的一种典型代表。在军事通信系统中,RS(31,15)码因其纠错能力被广泛应用。

优化设计的关键在于生成多项式的选择和改进。通过优化,编码器能够提高运算效率,减少编码和解码过程中的运算周期。这里的优化策略可能包括选择合适的生成多项式,使得编码和解码算法更加高效,或者采用了查表法来加速计算密集型操作。

RS编码原理的核心在于其能够纠正t个错误的性质。RS(n,k)码的特性包括:

1. **码长**:n等于2的某个幂次减一,即n = 2^m - 1,对应的比特数为m(2m-1)。

2. **信息码元数**:k = n - 2t,表明有k个信息位,每位用m比特表示。

3. **监督码元数**:n - k = 2t,即n-k个用于监督的冗余位,每个用m比特表示。

4. **最小距离**:d = 2t + 1,确保了至少能检测到t个错误,即d = n - k - 1。

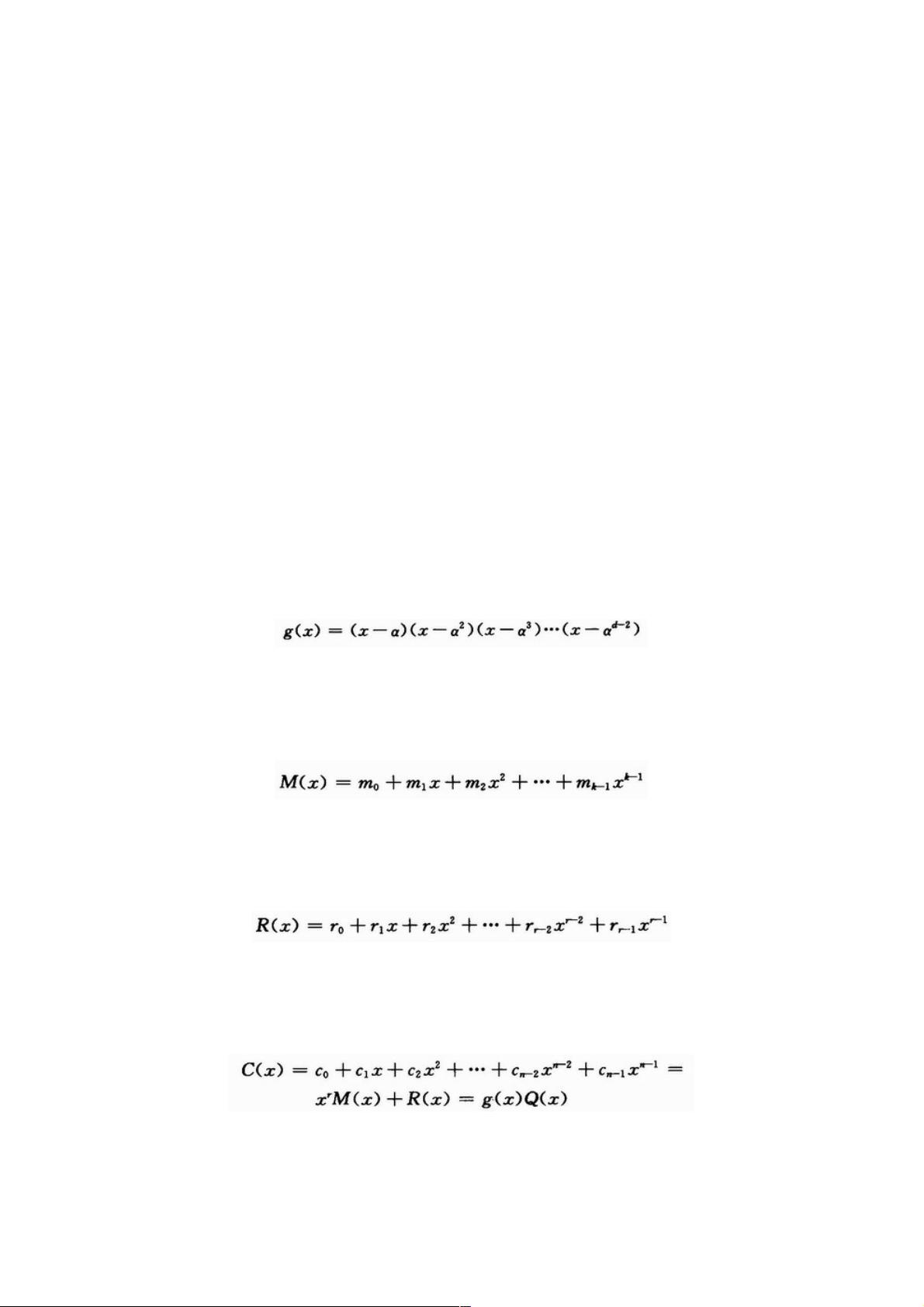

生成多项式的构造遵循特定规则:信息元多项式、监督多项式和码多项式之间存在关系。生成多项式Q(x)是g(x)除以C(x)得到的商式,这个过程反映了RS码的构造原理。

在FPGA实现上,作者使用了VHDL语言进行编程,VHDL是硬件描述语言,常用于描述数字电路的行为。通过这种平台,RS编码器可以在硬件层面实现高效运算,利用FPGA并行处理的优势,大幅提升了编码和解码的速度,且实现了低延迟和高吞吐量。

本文的重点在于RS编码器的优化设计策略,以及如何通过VHDL在FPGA上实现这些优化,从而实现实时高效的纠错功能,这对于提高通信系统的可靠性和抗干扰性至关重要。同时,它展示了将理论算法转化为实际应用的技术路径,对于从事硬件设计和通信系统开发的专业人士具有很高的参考价值。

104 浏览量

2020-10-25 上传

2021-07-13 上传

192 浏览量

192 浏览量

点击了解资源详情

660 浏览量

weixin_38678394

- 粉丝: 2

- 资源: 859

最新资源

- navindoor-code:室内定位算法设计框架。 模拟接入点信号和惯性信号。-matlab开发

- holbertonschool-web_back_end

- vue3-音乐

- Android6Data1.zip

- quadquizaminos:一种带有诸如测验问题的tretrominoes游戏,以获取战利品盒来帮助游戏。 这是Grox.io对四块的扩展

- 行业-2021年轻代厨房小家电洞察报告.rar

- recipes::file_folder:纤维示例

- .Net 4.6.2安装失败指导

- ServerGraphQL

- 等级保护2.0-测评指导书.zip

- SimpleDynamo:Amazon DynamoDB 的原型

- P2P

- 城市建筑网站模板

- sfkios.com:资产SFKIOS

- Aquatic-Surface-Vehicles-Simulator_Dev:开发OPAQS项目

- 行业-港股 哔哩哔哩招股说明书.rar