时钟技术在数字集成电路中的作用与挑战

下载需积分: 9 | PDF格式 | 573KB |

更新于2024-07-16

| 8 浏览量 | 举报

"该资源是2004年12月22日清华大学微电子所《数字大规模集成电路》课程的第9章(2)部分,主题聚焦于时钟技术,由周润德教授讲解。主要讨论了同步设计方法及其优缺点,并简要提及异步系统与自定时系统的概念。"

在数字集成电路设计中,时钟技术扮演着至关重要的角色。本课程首先介绍了同步设计方法。同步设计基于共同的时钟信号,确保系统中各个部件的操作在同一时刻进行,从而提供了一种结构化的方式来安排数字系统中的事件。这种设计方法的优势在于,它使得所有操作的延迟变得均匀,相当于最慢操作的延迟,保证了逻辑门延迟和连线延迟的协调。时钟起到了关键作用,不仅确保物理时序约束得以满足,还通过逻辑排序来决定事件的发生及其顺序。在时钟切换的瞬间,系统状态发生变化,新的操作开始。

然而,同步设计也存在一些缺点。其中最显著的是时钟偏移(Skew),即不同位置的时钟信号到达时间不一致,导致并非所有事件真正同步。此外,同步系统受到最慢元件延时的影响,特别是在流水线系统中,整体数据吞吐率受限于最慢元件的最坏情况延迟。例如,如果流水线有多个逻辑块,每个块的延迟不尽相同,那么系统速度将受限于最慢逻辑块的延迟。

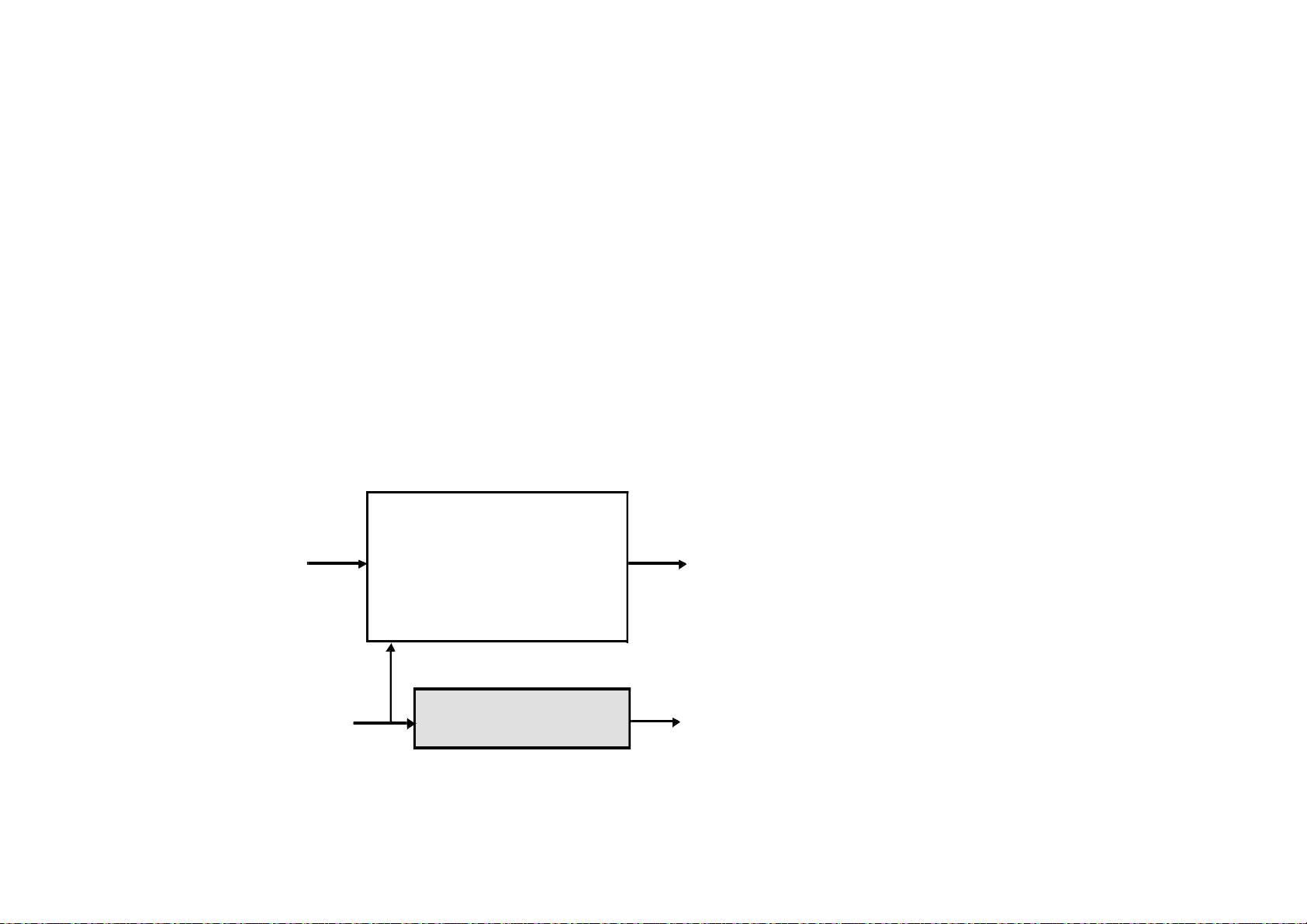

为了克服这些问题,异步系统被提出,它完全摒弃了全局时钟,通过信号间的相对时序关系来控制操作。异步设计虽然可以避免时钟相关问题,但设计复杂度高,需要对时序进行详尽分析,以防止竞争条件的发生。一种较为可靠的异步设计方法是采用自定时系统,它依赖于信号的完成和握手协议来确保操作的正确性和顺序。

以自定时系统的例子来说,如逻辑功能中的"Done"、"Go"和"Enable"信号,它们互相协作,只有当"Go"信号发出且"Enable"信号为1时,逻辑函数才开始执行,直至"Done"信号表明操作完成。这种方式确保了操作的正确排序,无需全局时钟也能实现可靠通信。

时钟技术在数字集成电路设计中具有核心地位,同步设计简化了系统设计,但受到时钟偏移和最慢元件限制;异步设计则提供了一种避免时钟问题的途径,但设计难度较大。自定时系统作为一种折衷方案,平衡了性能和复杂性,为数字系统设计提供了更多选择。

相关推荐

壹零捌

- 粉丝: 226

最新资源

- 自动生成CAD模型文件的测试流程

- 掌握JavaScript中的while循环语句

- 宜科高分辨率编码器产品手册解析

- 探索3CDaemon:FTP与TFTP的高效传输解决方案

- 高效文件对比系统:快速定位文件差异

- JavaScript密码生成器的设计与实现

- 比特彗星1.45稳定版发布:低资源占用的BT下载工具

- OpenGL光源与材质实现教程

- Tablesorter 2.0:增强表格用户体验的分页与内容筛选插件

- 设计开发者的色值图谱指南

- UYA-Grupo_8研讨会:在DCU上的培训

- 新唐NUC100芯片下载程序源代码发布

- 厂家惠新版QQ空间访客提取器v1.5发布:轻松获取访客数据

- 《Windows核心编程(第五版)》配套源码解析

- RAIDReconstructor:阵列重组与数据恢复专家

- Amargos项目网站构建与开发指南