CPU系统时钟电路详解:从NS3K故障到时钟源原理

"这篇文档是关于CPU系统时钟电路的基础知识介绍,主要聚焦于NS3K系统的时钟设计和故障现象。文档包含了NS3K系统时钟电路的详细描述、故障定位方法和故障分析,同时也深入讲解了CPU的系统时钟,包括主时钟源发生器电路的几种类型如石英晶体振荡器、皮尔斯电路和有源晶体振荡器,以及PLL的基本工作原理。此外,文档强调了晶体时钟电路在嵌入式系统中的核心作用,并通过具体的NS3K案例来阐述硬件设计的关键点。"

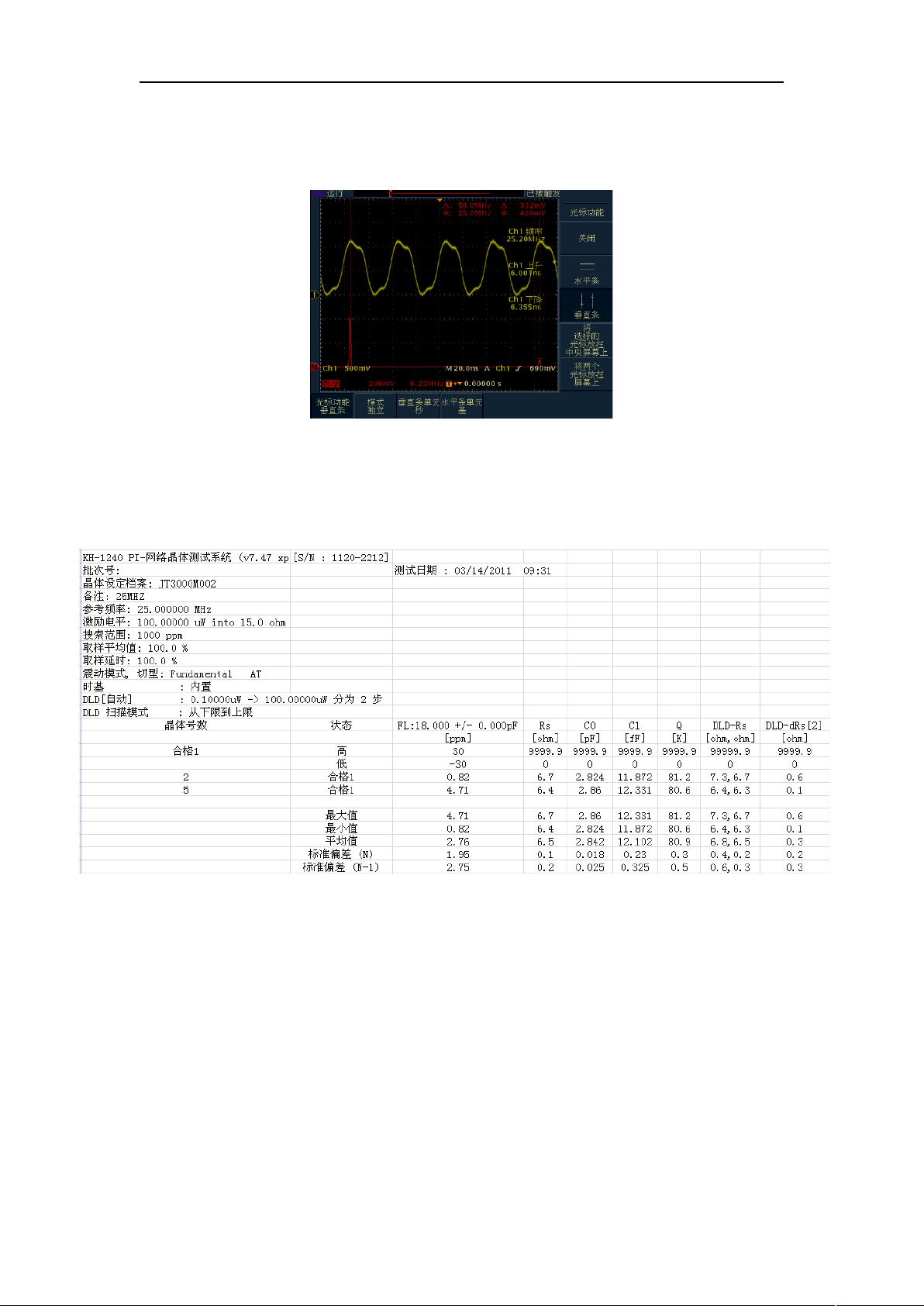

在CPU系统中,时钟电路起着至关重要的作用,它是整个系统的脉搏,确保了系统的稳定运行。NS3K系统时钟电路的设计遵循了特定的要求,例如CPU APM80186需要的SYSXTAL Input必须满足一定的电压转换速率(Slew Rate)和周期到周期抖动(Cycle-to-Cycle Jitter)限制。压摆率是衡量电压变化速度的一个参数,而周期到周期抖动则关乎时钟信号的精度。

文档中详细列举了CPU对输入时钟的具体要求,例如压摆率至少为1V/ns,周期到周期抖动不能超过150ps,占空比保持在40%到60%之间。这些参数对于保证CPU正常工作和提高系统性能至关重要。当时钟电路出现故障时,可能会影响到CPU的运算速度和系统的稳定性。

文档还探讨了不同的时钟源发生器电路,例如石英晶体振荡器,它通过机械谐振产生稳定的频率;皮尔斯电路,是一种常见的晶体振荡器配置,利用反相器提供负阻抗来驱动晶体;以及有源晶体振荡器,它内置振荡电路,提供更稳定且易于调节的时钟信号。

PLL(锁相环)的基本原理也在文档中被提及,它是一种能锁定输出信号频率与输入信号频率之间的相位关系的电路,常用于频率合成和频率倍增,能够确保系统时钟的精确性和可调性。

通过对NS3K系统时钟电路的故障分析和定位,读者可以学习如何诊断和解决时钟相关问题,这对于硬件开发者和维护人员来说是非常实用的知识。整体而言,这份文档提供了一个深入了解CPU系统时钟电路及其重要性的窗口,对学习和实践硬件设计具有指导意义。

2020-07-14 上传

2020-07-15 上传

2010-03-12 上传

2010-01-11 上传

2020-07-16 上传

2009-06-03 上传

2010-05-09 上传

2009-01-19 上传

2021-10-01 上传

juden_yang

- 粉丝: 1

- 资源: 6

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率