TLV320ADC3101: 低功耗立体声ADC与嵌入式miniDSP

需积分: 5 122 浏览量

更新于2024-06-28

4

收藏 2.93MB PDF 举报

"TI-TLV320ADC3101.pdf 是一款由TI(德州仪器)推出的低功耗立体声模拟到数字转换器(ADC),适用于无线手机和便携式音频系统,具有内置的迷你DSP(数字信号处理器)功能。"

**TLV320ADC3101关键特性:**

1. **立体声音频ADC** - 提供高质量的立体声音频转换。

2. **无线手机应用** - 专为无线通信设备设计,适应其低功耗需求。

3. **便携式低功耗音频系统** - 优化了能源效率,适合便携设备。

4. **92-dB信噪比** - 高信噪比确保了音频信号的清晰度和纯净度。

5. **支持多种采样率** - 从8kHz到96kHz,适应不同应用场景。

6. **前端语音或音频处理器** - 适用于数字音频处理。

7. **指令可编程嵌入式迷你DSP** - 可根据需求定制处理算法。

8. **灵活的数字滤波** - 支持低延迟IIR滤波器(用于语音)和线性相位FIR滤波器(用于音频)。

9. **可编程增益放大器** - 提供高达40dB的模拟增益或自动增益控制(AGC)。

**应用领域:**

1. **无线手机** - 用于手机中的音频处理和录音。

2. **噪声消除系统** - 利用内置的DSP进行噪声过滤和消除。

3. **便携式低功耗音频系统** - 如蓝牙音箱、MP3播放器等。

4. **数字音频前端处理** - 在各种音频设备中提供预处理功能。

**描述与功能模块:**

- **低延迟IIR滤波器** - 实时处理语音信号,减少响应时间,提高通话质量。

- **线性相位FIR滤波器** - 用于音频处理,确保在不同频率上保持一致的时间延迟,提高音质。

- **可编程系数、指令和内置处理** - 用户可以通过编程改变滤波器参数,实现不同的信号处理效果。

- **RAM可编程块** - 允许用户存储自定义的滤波器系数和处理程序,增加了灵活性。

**资源与支持:**

该产品附带了技术文档、工具软件、支持社区和参考设计,方便开发人员进行设计集成和优化。

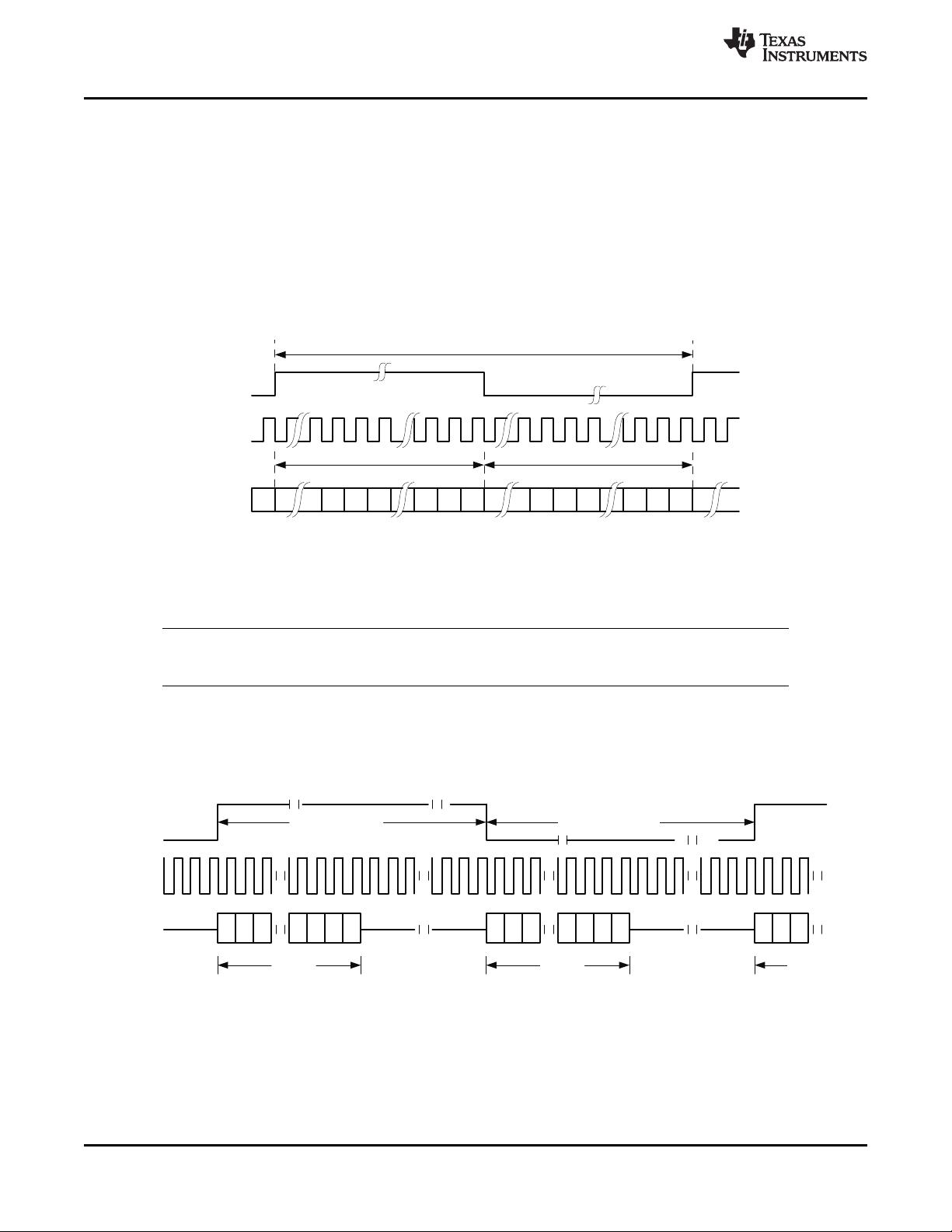

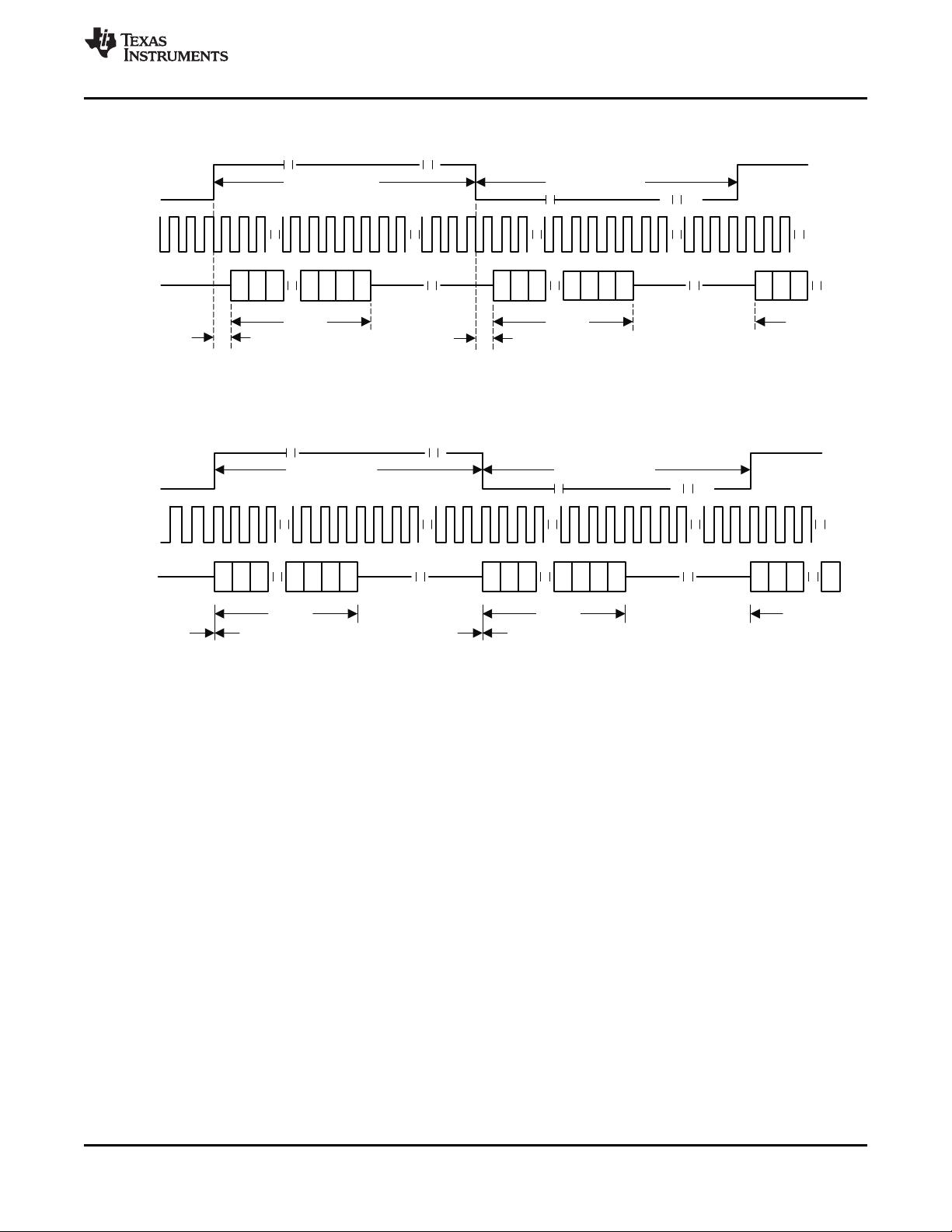

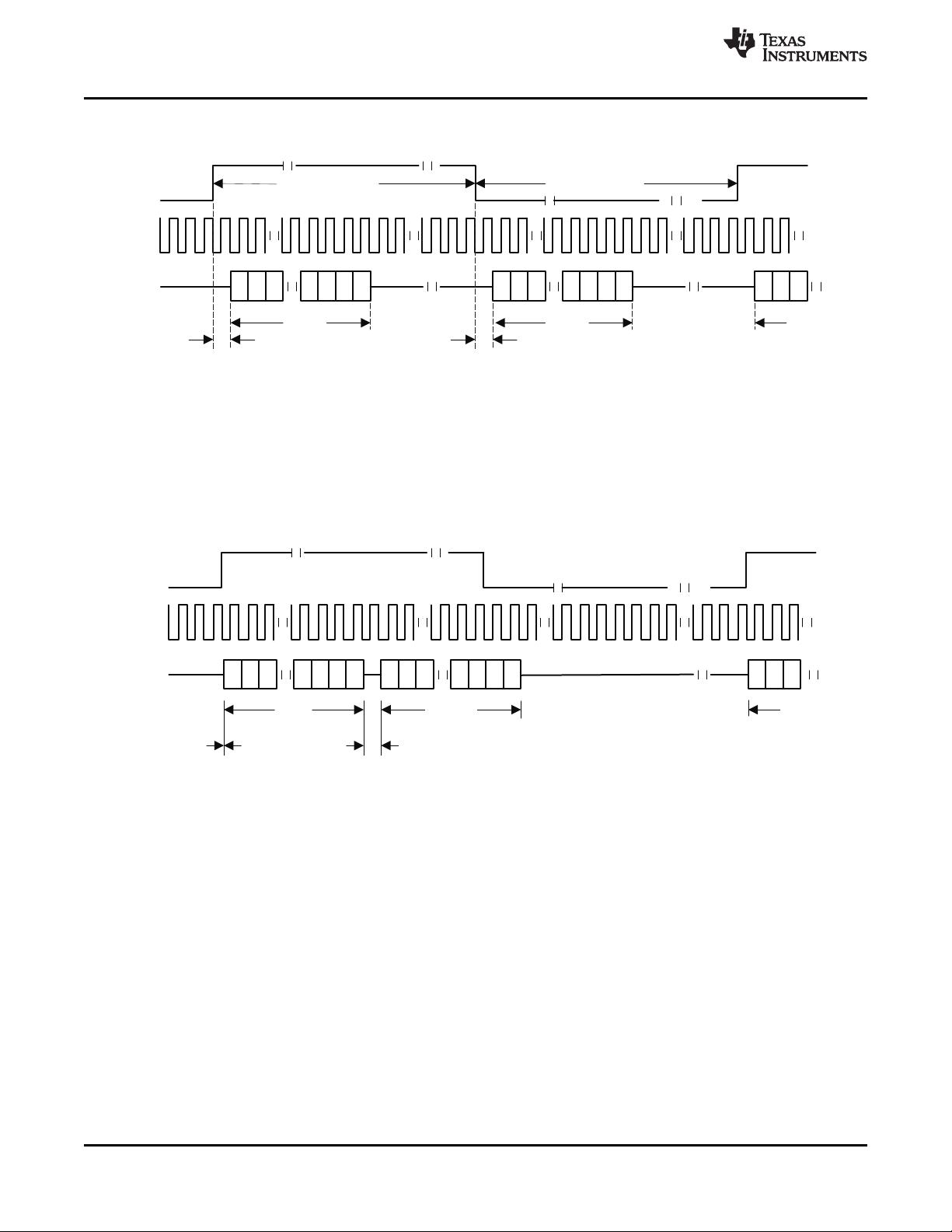

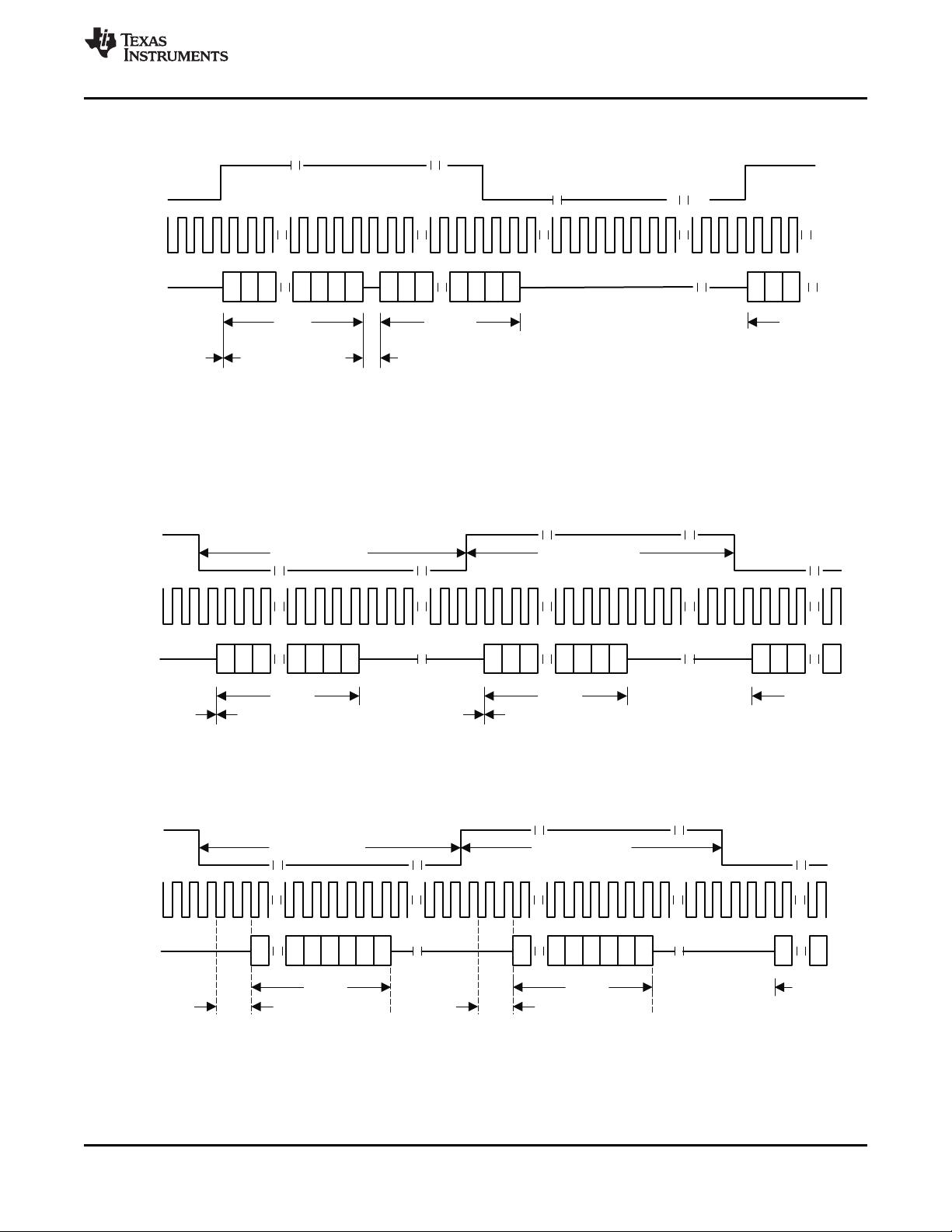

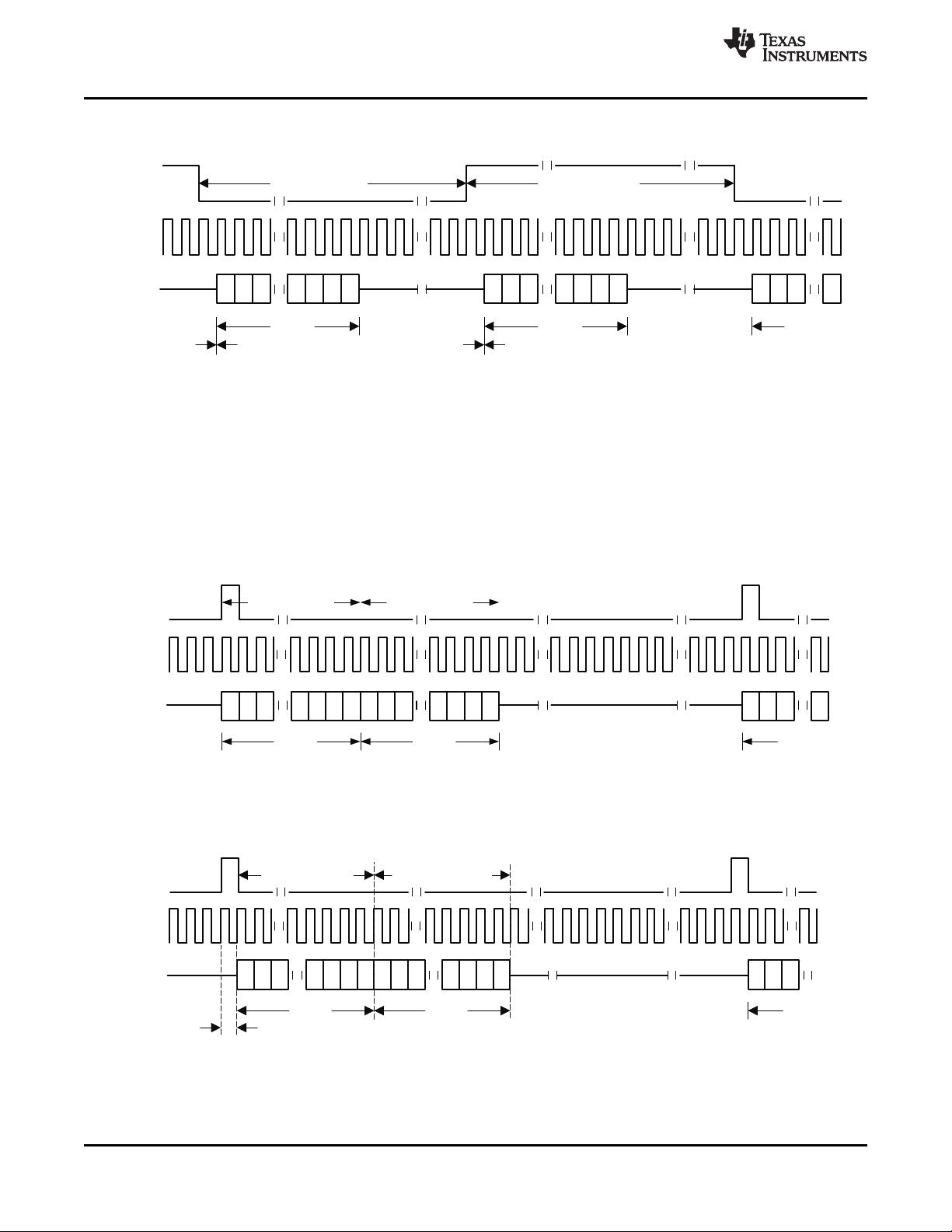

TLV320ADC3101是一款高度集成的音频解决方案,结合了高精度的ADC和强大的迷你DSP,适用于需要高效能音频处理且对功耗有严格要求的无线和便携设备。通过其丰富的接口(如I2S、LJ、RJ、DSP和TDM),可以轻松与其他处理器和系统组件集成,实现复杂音频系统的构建。

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

2022-12-03 上传

不觉明了

- 粉丝: 4090

- 资源: 5759

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案