EDA实验:FPGA上的多功能数字钟设计

需积分: 0 131 浏览量

更新于2024-06-30

收藏 577KB DOCX 举报

"EDA(II)实验报告 - 多功能数字钟设计"

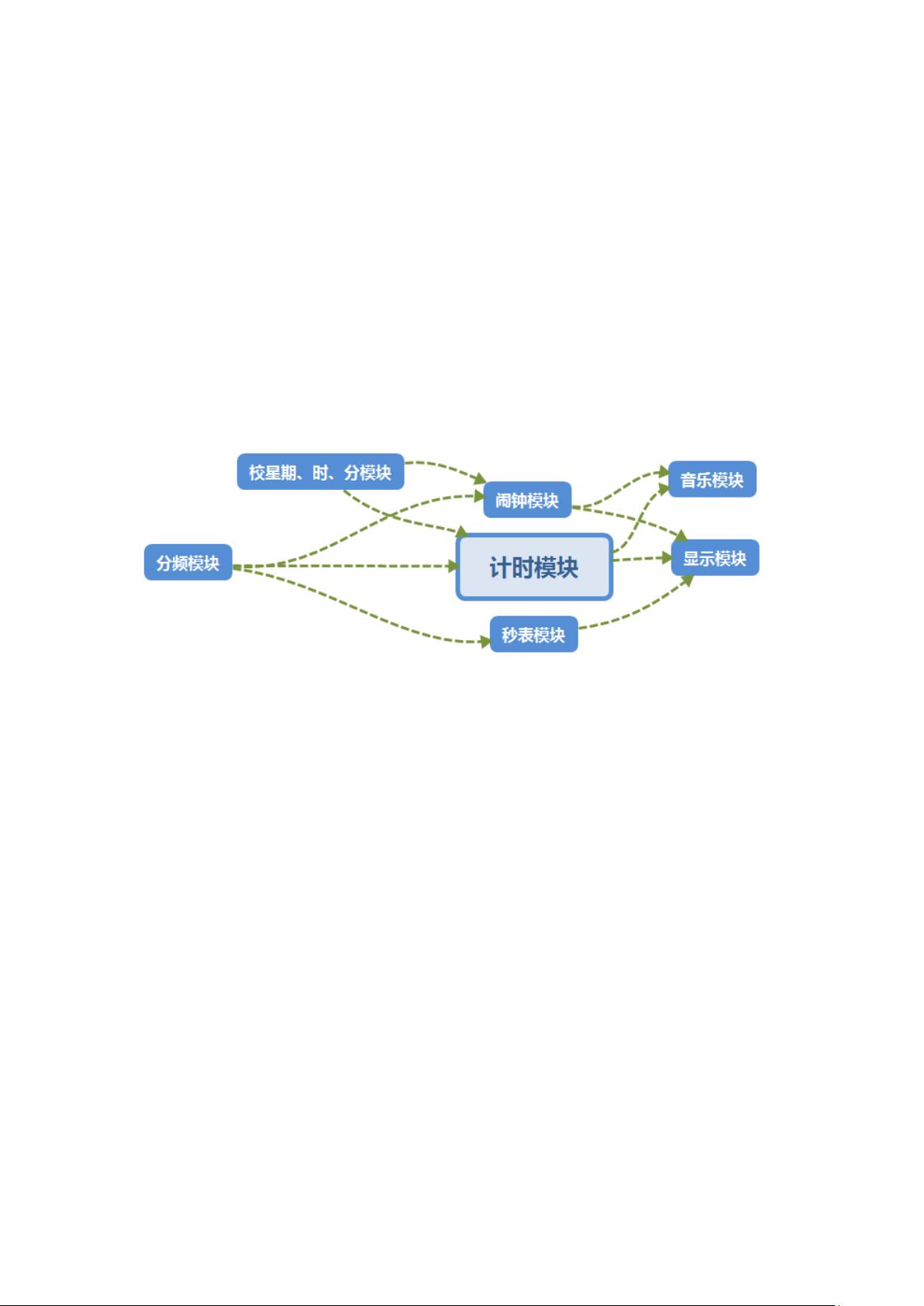

在数字钟的设计中,通常会涉及多个核心模块,这些模块共同协作以实现精确的计时和丰富的功能。根据给定的描述,我们可以详细解析一下这个基于FPGA的数字钟设计的关键知识点:

1. FPGA(Field-Programmable Gate Array): FPGA是一种可编程逻辑器件,允许用户根据需求配置内部的逻辑单元。在本项目中,设计者选择FPGA作为硬件平台,因为它提供了高度的灵活性和并行处理能力,适合实现复杂的数字逻辑功能。

2. VHDL语言: VHDL(VHSIC Hardware Description Language)是一种用于硬件描述的语言,用于编写逻辑设计代码,以便在FPGA上实现。在这个实验中,设计者使用VHDL来编写各个模块的逻辑,确保数字钟的各种功能得以实现。

3. 分频模块: 数字钟的计时精度依赖于稳定的时钟源。分频器模块负责将外部提供的高频率时钟信号降低到合适的频率,如32768Hz,这是常见的石英晶体振荡器频率,可以被轻易地除以2的幂次得到一秒的间隔。

4. 校星期、时、分模块: 这些模块负责接收来自分频器的信号,并进行计数,以计算出当前的星期、小时和分钟。考虑到24小时制,设计中可能包含逻辑来处理小时的跨越(从23到0)。

5. 清零保持模块: 这个模块允许用户清零或保持当前时间,提供了一个灵活的操作选项。

6. 计时模块: 此模块负责持续计时,更新星期、时、分、秒的显示,并可能包含闰年和月份天数的处理逻辑。

7. 闹钟模块: 闹钟功能需要设定特定的时刻触发报警,这涉及到比较当前时间与预设闹钟时间的逻辑。

8. 秒表模块: 秒表功能是独立的计时器,可以记录一定时间段的长短,通常用于体育比赛等场合。

9. 音乐模块: 当达到特定条件,如整点报时或闹钟触发时,音乐模块会产生音频信号,可能通过蜂鸣器或其他音频输出设备播放。

10. 显示模块: 由七个数码管组成的显示器,分别显示星期、时十位、时个位、分十位、分个位、秒十位、秒个位。每个数码管需要驱动电路来控制它们的亮灭状态,以显示相应的时间信息。

11. 自顶向下设计方法: 设计过程中采用的自顶向下设计方法意味着先设计顶层的系统架构,然后逐步细化到每个子模块,每个模块独立验证其功能,最后集成所有模块。

12. 仿真与验证: 在VHDL代码编写完成后,设计者通过软件工具如QuartusⅡ进行仿真,检查代码逻辑是否正确。在仿真验证无误后,将设计下载到实际的FPGA实验板上进行硬件测试。

13. 引脚分配与下载: 最后,为每个模块分配合适的FPGA引脚,确保所有信号能正确传输。完成分配后,通过JTAG接口将设计烧录到FPGA中。

通过这样的设计和实现,一个功能丰富的数字钟被创建出来,不仅满足基本的计时需求,还具备了诸如校时、闹钟、秒表等附加功能,展示了EDA技术在实现复杂数字系统中的强大能力。

2022-08-03 上传

2021-03-19 上传

152 浏览量

2025-03-06 上传

萌新小白爱学习

- 粉丝: 25

最新资源

- Ruby语言集成Mandrill API的gem开发

- 开源嵌入式qt软键盘SYSZUXpinyin可移植源代码

- Kinect2.0实现高清面部特征精确对齐技术

- React与GitHub Jobs API整合的就业搜索应用

- MATLAB傅里叶变换函数应用实例分析

- 探索鼠标悬停特效的实现与应用

- 工行捷德U盾64位驱动程序安装指南

- Apache与Tomcat整合集群配置教程

- 成为JavaScript英雄:掌握be-the-hero-master技巧

- 深入实践Java编程珠玑:第13章源代码解析

- Proficy Maintenance Gateway软件:实时维护策略助力业务变革

- HTML5图片上传与编辑控件的实现

- RTDS环境下电网STATCOM模型的应用与分析

- 掌握Matlab下偏微分方程的有限元方法解析

- Aop原理与示例程序解读

- projete大语言项目登陆页面设计与实现