"这篇教程是针对新手的‘适合新手入门的超简单ISE设计流程’,主要介绍了如何使用Xilinx的ISE工具进行FPGA设计。内容涵盖了从传统的数字系统设计流程到现代数字系统设计流程的转变,特别强调了使用VHDL语言在ISE中的设计步骤,包括工程建立、设计实现、仿真、布局布线以及设计下载等关键环节。"

在FPGA设计领域,Xilinx的Integrated Software Environment (ISE) 是一个广泛使用的工具套件,尤其适合初学者学习和实践。这篇教程的目标是帮助新手快速掌握如何使用ISE进行FPGA设计。首先,它对比了传统的数字系统设计流程和现代流程,传统流程主要依赖人工化简逻辑,而现代流程则利用计算机自动化完成,如功能级仿真、逻辑综合、时序仿真等步骤。

教程接着深入到基于VHDL语言的ISE设计流程。VHDL是一种硬件描述语言,允许开发者用接近于自然语言的方式来描述数字系统的功能。在ISE中,设计流程通常包括以下几个步骤:

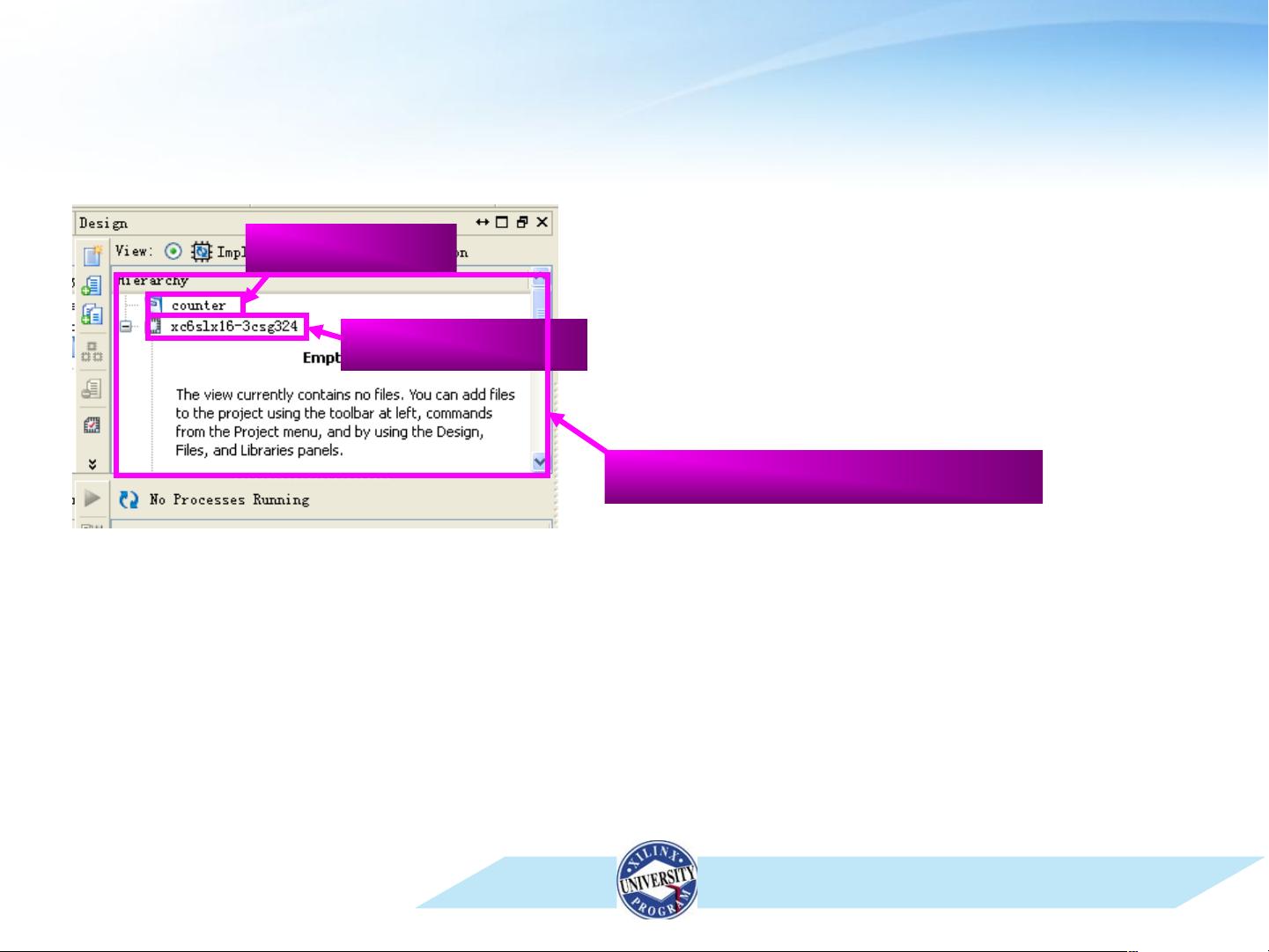

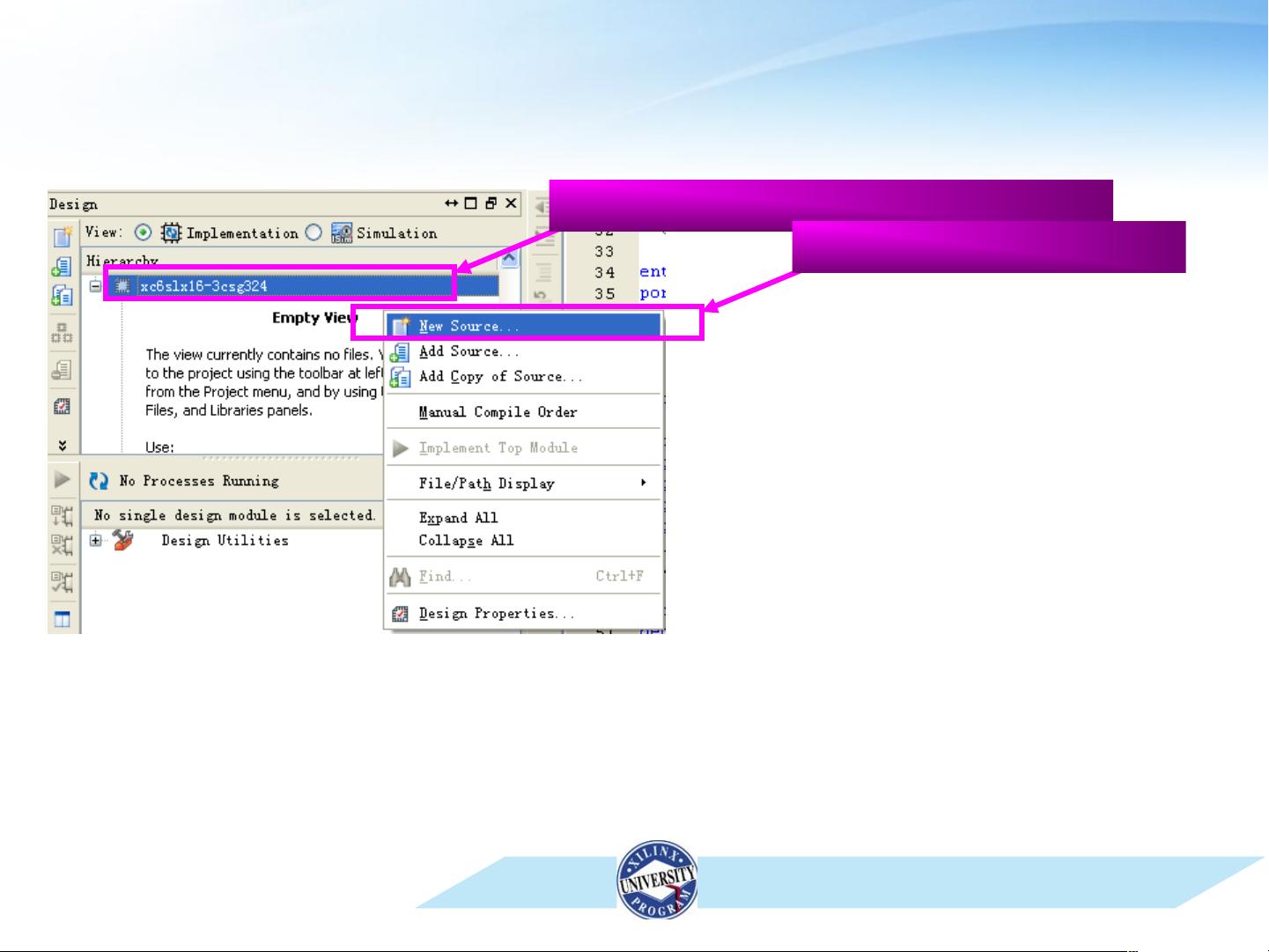

1. **工程建立**:创建一个新的工程,并设置所需的器件和设计目标。

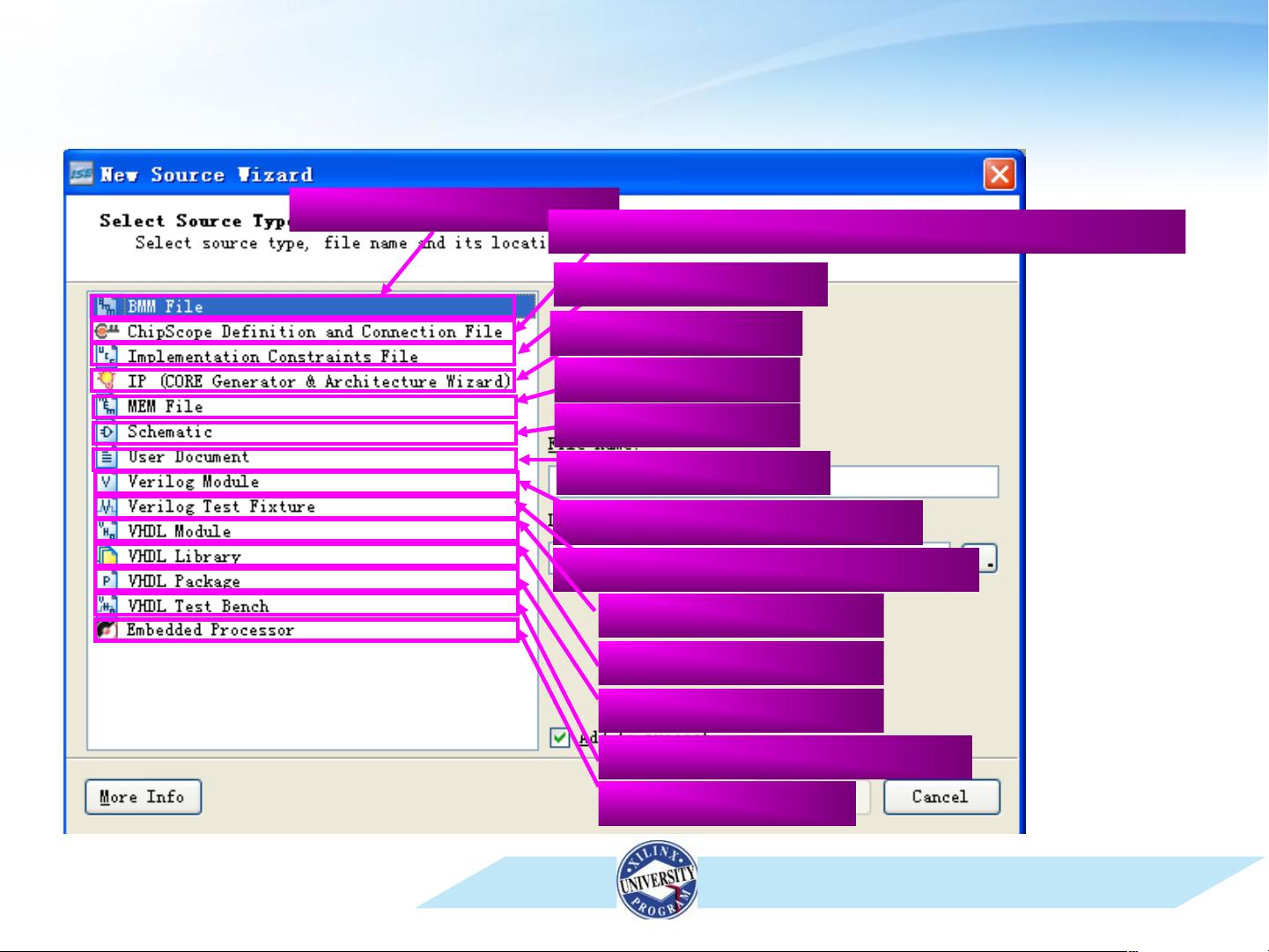

2. **设计输入**:编写VHDL代码来定义你的数字系统,例如文中提到的3位计数器和分频器。

3. **功能级仿真**:在代码编写完成后,先进行功能仿真以确保设计逻辑正确。

4. **逻辑综合**:将VHDL代码转换成门级网表,这一过程称为逻辑综合。

5. **时序仿真**:对综合后的设计进行时序仿真,检查其在实际时钟速度下的行为是否符合预期。

6. **设计实现**:包括添加用户约束、映射(Map)、布局布线(PAR)等步骤,使设计适应选定的FPGA器件。

7. **设计下载**:将编译好的设计下载到FPGA芯片中进行硬件验证。

8. **PROM文件生成和下载**:对于不直接在FPGA上运行的设计,可以生成编程文件并下载到PROM中,以便在其他系统中使用。

在教程中,还提到了启动ISE13.3软件的方法,以及如何通过点击软件图标开始设计流程。通过这个逐步指导,新手可以逐步了解并掌握FPGA设计的基础知识和ISE工具的使用技巧。

总结来说,这篇教程为初学者提供了一个清晰的路径,从理解基本的数字系统设计概念到动手实践使用ISE进行FPGA设计,为后续更深入的学习和项目开发打下了坚实的基础。