"高速电路PCB的电源地噪声设计"

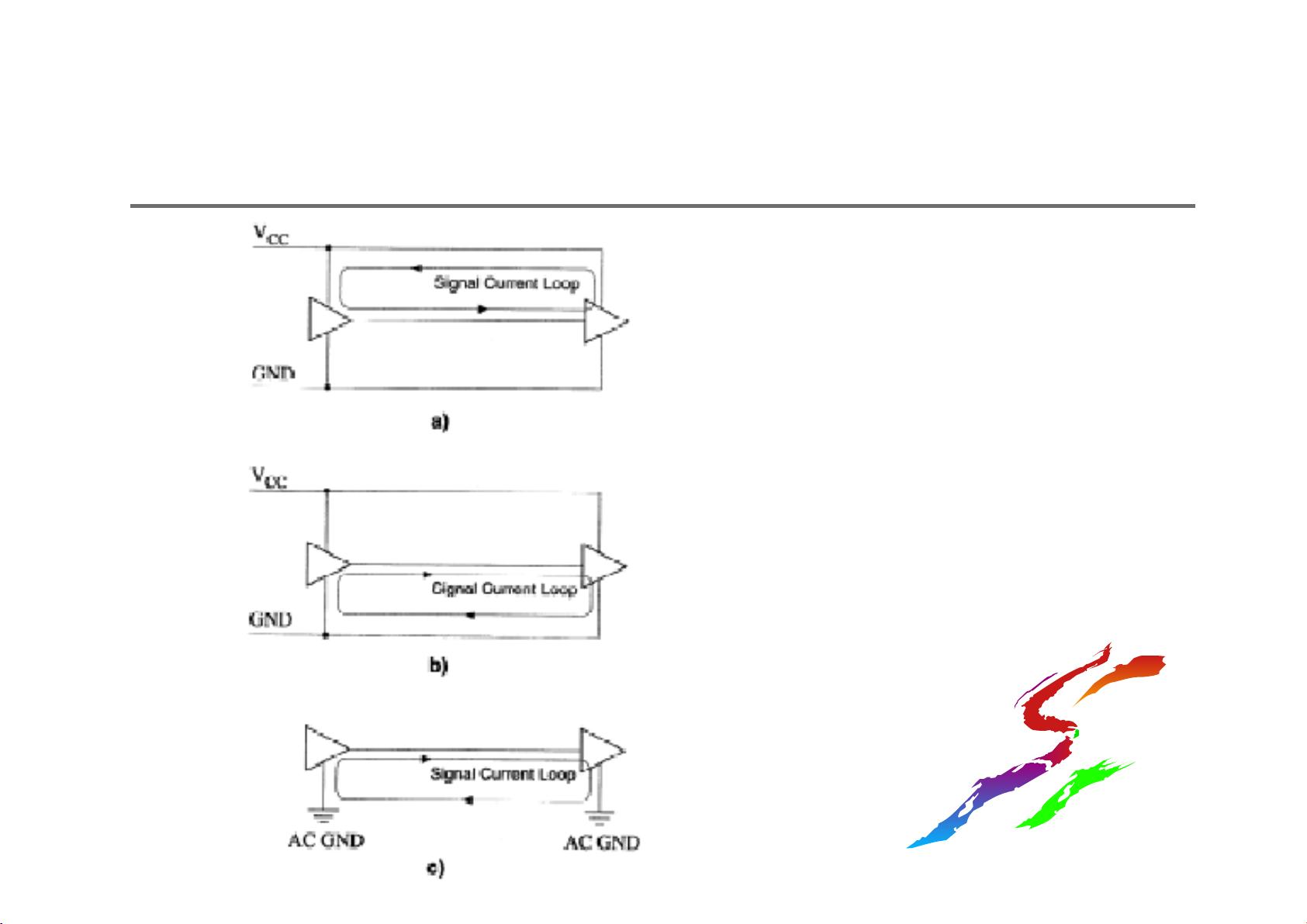

高速电路PCB设计中的电源地噪声是一个关键问题,它直接影响到电路的性能和稳定性。在高速电路中,电源和地平面不仅为各部分电路提供低噪声电源和电位参考点,还作为信号传输的低阻抗回路,有助于降低串扰。然而,电源地噪声的产生是由于实际电源的阻抗并非理想状态的0,这导致电源系统不能完全吸收所有噪声。

电源地噪声的根本原因是电源阻抗不为0。理想情况下,电源的阻抗为0,可以确保源端和负载端电压一致,负载端的噪声被电源吸收。但现实中,电源有非零阻抗,这使得噪声得以传播。此外,高速电路中的电源地平面虽然通常具有较低的阻抗,但它们也会形成谐振腔,在特定频率上表现出高阻抗。当信号工作频率或其高次谐波与这些谐振频率匹配时,电源地平面反而可能成为噪声辐射的源头。

计算平面谐振腔的谐振频率公式涉及到正方形金属平面的边长"a",对于常见的单板尺寸,谐振频率可能在200M至400M,甚至更高。这种现象提示我们在设计高速电路时必须考虑到电源地平面的谐振特性,避免工作在谐振点附近。

电源噪声的来源包括但不限于:

1. 纹波:这是由于开关电源工作产生的,纹波与电源的效率有关,高效率往往伴随较大的纹波噪声。

2. 高频干扰噪声:开关电源在工作时产生的高频干扰。

3. 数字电路高速总线的瞬态变换噪声:当高速信号在总线上切换时,会引起电源地噪声。

4. 过冲、振铃和串扰:这些是信号质量问题,可能导致电源地噪声。

5. 器件辐射发射噪声:某些器件在工作时会辐射噪声,影响电源的纯净度。

6. 电源地反弹:快速变化的负载电流会导致地电位的变化,产生噪声。

7. 大功率模拟电路如功放或大电流继电器的使用,也可能引入显著的电源噪声。

为了降低电源噪声,设计师需要采取以下措施:

1. 使用低阻抗电源平面,优化电源分配网络。

2. 设计适当的电源滤波器,如LC滤波器,以减少开关电源的高频噪声。

3. 分割电源地平面,避免不同类型的信号共享同一电源地,减少耦合。

4. 使用电源去耦电容,提供局部储能,减少电源噪声的影响。

5. 考虑到谐振频率,设计时避开谐振点,确保信号工作在低阻抗区域。

理解和控制高速电路PCB的电源地噪声是确保电路稳定性和可靠性的核心要素,设计师需要深入理解电源系统的物理机制,并运用各种设计技巧来抑制噪声。通过精细的布局布线策略和适当的电源管理,可以显著提升高速电路的性能。