一种新型SOC跨时钟域同步电路设计

14 浏览量

更新于2024-08-31

收藏 463KB PDF 举报

"多时钟系统下跨时钟域同步电路的设计"

随着集成电路技术的飞速发展,System-on-Chip(SOC)的复杂性不断提高,多时钟系统成为了常态。这导致了跨时钟域同步问题的挑战,如亚稳态、漏信号和误触发等。传统的优化方法虽然提供了解决思路,但在电路简洁性和成本效益方面存在不足。本文针对这些问题,提出了一种新的跨时钟域同步电路设计策略。

1. 跨时钟域同步的重要性

跨时钟域同步是SOC设计中的关键环节,因为不同时钟域间的信号传递如果不加以同步,可能会引发亚稳态,导致逻辑错误。亚稳态是由于触发器无法在规定时间内稳定在确定状态,从而产生的不稳定输出。如果不妥善处理,亚稳态可能会影响到整个系统的可靠性。

2. 常见的跨时钟域同步方法

常用的同步方法包括电平同步器、边沿检测同步器和脉冲同步器。电平同步器依赖于信号电平变化来触发,但可能会出现亚稳态问题;边沿检测同步器利用时钟边沿进行同步,但对输入脉冲宽度有要求;脉冲同步器则更注重信号脉冲的完整性,但同样有其局限性。这些方法在应对特定情况时,可能无法达到理想效果。

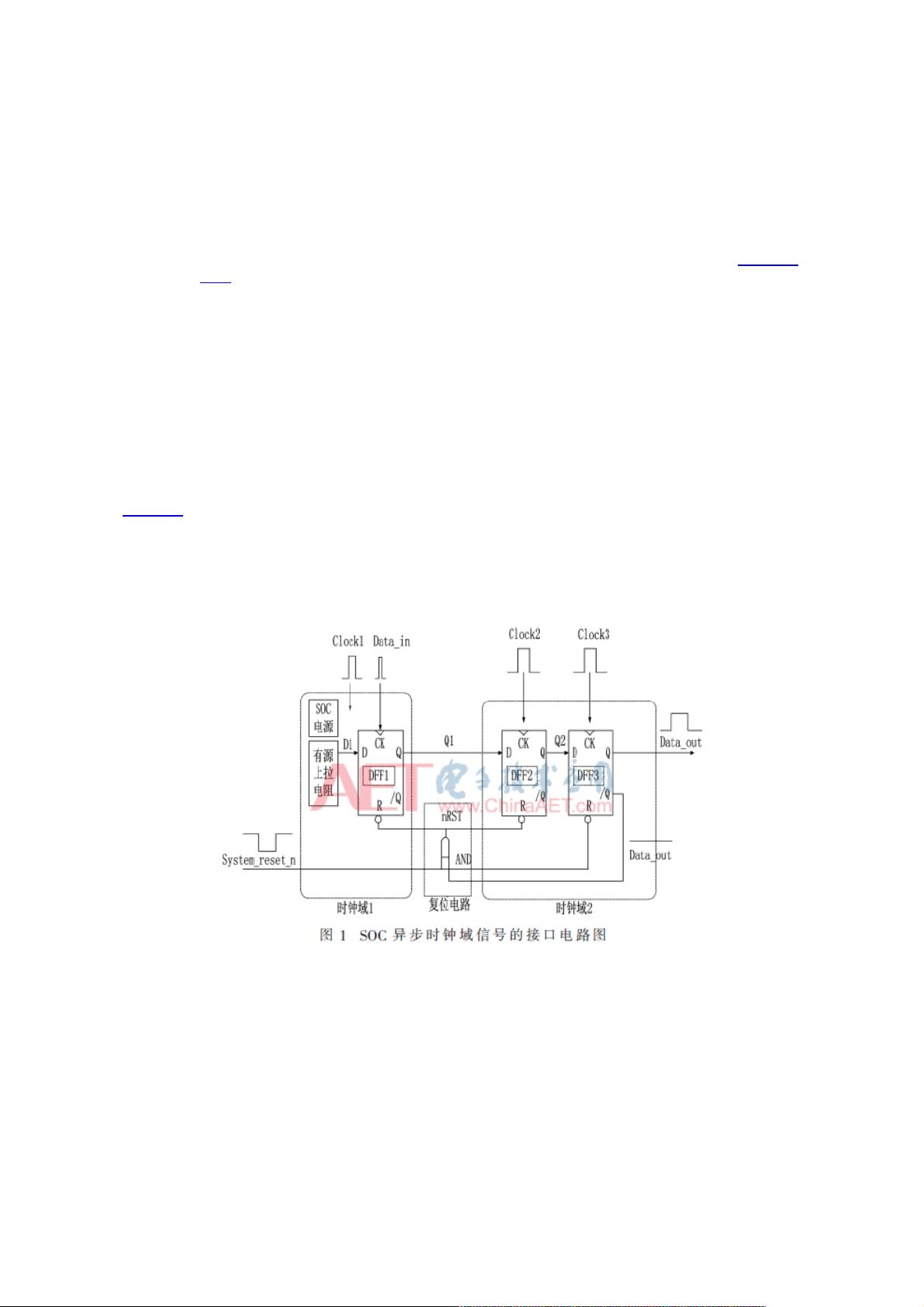

3. 新的跨时钟域同步电路设计

本文提出的新型同步电路设计,主要由两个时钟域和一个复位电路构成。时钟域1包含一个带有异步复位功能的同步触发器,它能在时钟上升沿锁存数据。时钟域2由两个类似的触发器组成,同样具有异步复位和同步时钟功能。这种设计通过级联结构,增强了信号的稳定性,有效地减少了亚稳态的影响。

4. 电路的优化与验证

新设计的优势在于电路结构简单,提高了可靠性。经过仿真实验和实测验证,该电路能够适应最小输入脉宽,防止漏信号,避免误触发和多触发,从而有效地解决了亚稳态问题。此外,简化电路降低了成本,使其适用于小规模IC设计。

5. 结论

面对多时钟系统下的同步挑战,设计出既能适应复杂环境,又能保证高可靠性的跨时钟域同步电路至关重要。本文提出的新型设计方法,通过创新电路架构,成功地解决了传统方法的局限性,为未来多时钟系统的设计提供了新的思路和解决方案。

跨时钟域同步电路的设计是现代SOC设计的核心技术之一。通过深入理解并优化这一领域,可以提升整个系统的性能和稳定性,推动集成电路技术的进一步发展。

182 浏览量

126 浏览量

180 浏览量

318 浏览量

125 浏览量

243 浏览量

295 浏览量

247 浏览量

2021-07-26 上传

weixin_38577922

- 粉丝: 10

最新资源

- A7Demo.appstudio:探索JavaScript应用开发

- 百度地图范围内的标注点技术实现

- Foobar2000绿色汉化版:全面提升音频播放体验

- Rhythm Core .NET库:字符串与集合扩展方法详解

- 深入了解Tomcat源码及其依赖包结构

- 物流节约里程法的文档整理与实践分享

- NUnit3.vsix:快速安装NUnit三件套到VS2017及以上版本

- JQuery核心函数使用速查手册详解

- 多种风格的Select下拉框美化插件及其js代码下载

- Mac用户必备:SmartSVN版本控制工具介绍

- ELTE IK Web编程与Web开发课程内容详解

- QuartusII环境下的Verilog锁相环实现

- 横版过关游戏完整VC源码及资源包

- MVC后台管理框架2021版:源码与代码生成器详解

- 宗成庆主讲的自然语言理解课程PPT解析

- Memcached与Tomcat会话共享与Kryo序列化配置指南