使用ModelSimSE进行ALTERA FPGA的功能与时序仿真教程

需积分: 9 163 浏览量

更新于2024-07-28

收藏 872KB PDF 举报

"modelsimse学习手册 - FPGA功能仿真与时序仿真的方法"

在FPGA设计过程中,ModelSimSE是一款非常重要的仿真工具,它能够帮助开发者在实际硬件部署之前验证和调试逻辑设计。本手册主要关注如何使用ModelSimSE进行ALTERA FPGA的设计仿真。

首先,确保你已经安装了以下必要的软件:

1. Quartus II:这是ALTERA提供的综合、适配、编程和调试工具,用于FPGA设计。文中提到的是Quartus II 6.1版本,但请注意,随着ALTERA被Intel收购,现在的版本可能已经更新为Quartus Prime。

2. ModelSimSE:这是一款强大的混合信号系统级仿真器,支持ALTERA的仿真库。你需要确保ALTERA的仿真库已经正确安装,并与ModelSimSE集成。

在开始仿真之前,你需要创建一个简单的工程作为例子。按照以下步骤操作:

1. 创建新工程,命名为“lpm_shift”,选择目标器件,如Cyclone II EP2C5Q208C。

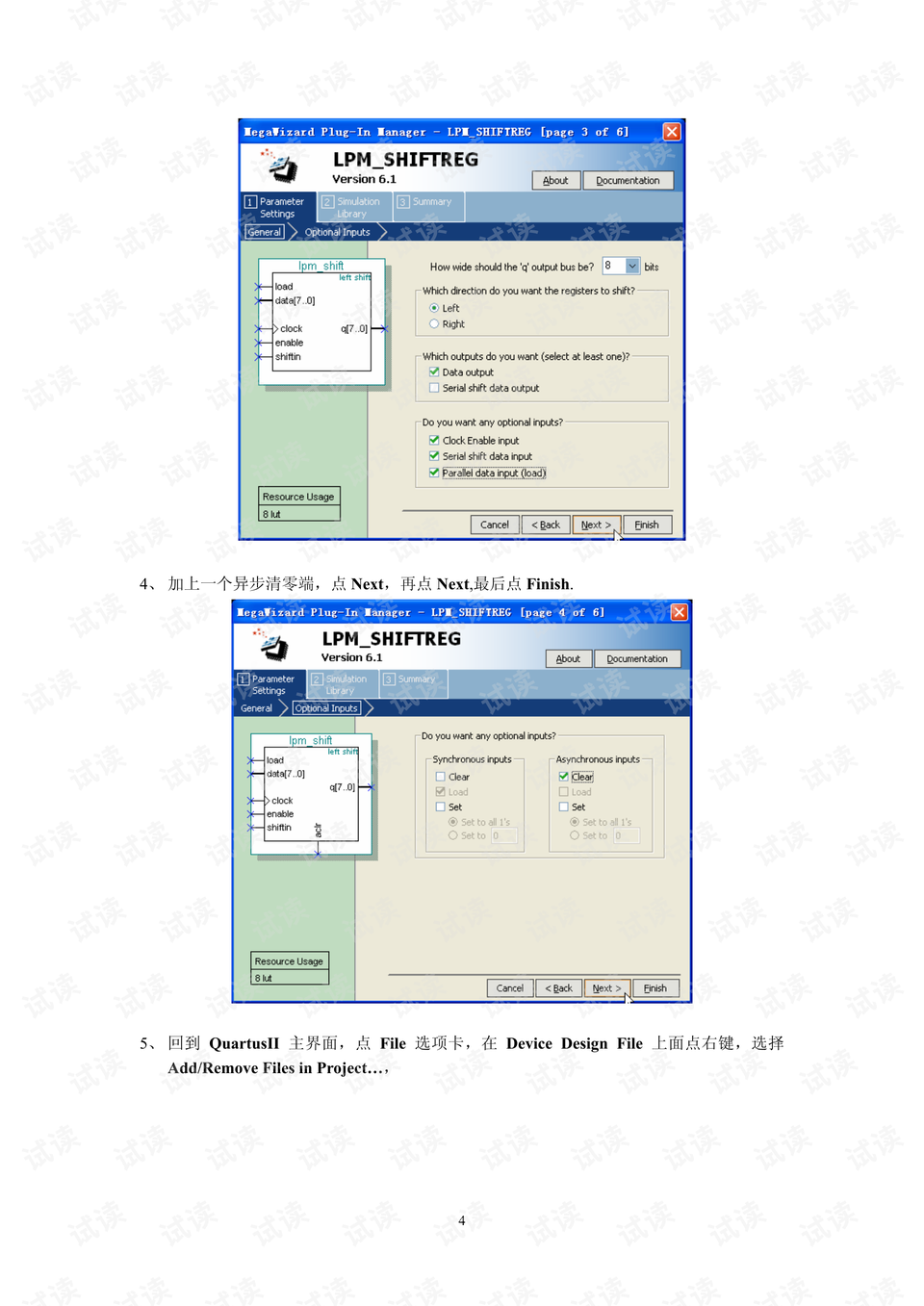

2. 使用MegaWizard Plug-In Manager生成一个LPM_SHIFTREG模块,选择Verilog语言,配置输出文件。

3. 该示例使用了ALTERA的LPM库,设置完成后生成模块代码。

4. 添加异步清零功能,并将生成的“lpm_shift.v”文件添加到工程中。

5. 编写测试平台(TestBench)以验证模块功能。测试平台通常是一个独立的Verilog文件,模拟输入信号并检查输出,确保设计按预期工作。

ModelSimSE支持多种仿真流程,这里介绍一种有效的方法:

1. 在Quartus II中完成设计后,通过File > Add/Remove Files in Project将所有相关文件添加到工程。

2. 创建一个新的Verilog测试平台文件(top_tb),定义测试用例,包括初始化信号、激励生成以及期望的响应检查。

3. 在ModelSimSE中打开工程,编译所有源文件,确保没有语法错误。

4. 运行仿真,观察波形窗口中的信号变化,分析设计行为。

5. 如果需要,可以设置断点,单步执行,或者改变激励,进行深入的调试。

在进行功能仿真时,主要关注设计是否满足逻辑功能。而时序仿真则涉及到信号的时序特性,例如延迟、时钟周期等,以确保设计在实际时钟速度下能正常工作。在ModelSimSE中,可以通过设置不同的时钟源和观察信号的定时来完成时序分析。

通过这个手册,你将了解如何利用ModelSimSE与Quartus II协同工作,进行ALTERA FPGA的设计验证,从而提高设计质量和效率。对于初学者和有经验的工程师来说,熟悉这些步骤都是确保FPGA项目成功的关键。

lijingcsu

- 粉丝: 0

最新资源

- C#实现DataGridView过滤功能的源码分享

- Python开发者必备:VisDrone数据集工具包

- 解决ESXi5.x安装无网络适配器问题的第三方工具使用指南

- GPRS模块串口通讯实现与配置指南

- WinCvs客户端安装使用指南及服务端资源

- PCF8591T AD实验源代码与使用指南

- SwiftForms:Swift实现的表单创建神器

- 精选9+1个网站前台模板下载

- React与BaiduMapNodejs打造上海小区房价信息平台

- 全面解析手机软件测试的实战技巧与方案

- 探索汇编语言:实验三之英文填字游戏解析

- Eclipse VSS插件版本1.6.2发布

- 建站之星去版权补丁介绍与下载

- AAInfographics: Swift语言打造的AAChartKit图表绘制库

- STM32高频电子线路实验完整项目资料下载

- 51单片机实现多功能计算器的原理与代码解析