Modelsim仿真入门教程:从新建工程到运行仿真

需积分: 10 12 浏览量

更新于2024-09-01

收藏 1.12MB DOCX 举报

"Modelsim是一款强大的FPGA仿真工具,适合初学者进行Verilog设计的验证。这份技术文档提供了Modelsim的入门步骤,包括新建工程、编译、仿真以及观察波形,同时也强调了一些Verilog编程的注意事项。"

在使用Modelsim进行FPGA仿真测试时,以下是一些关键知识点:

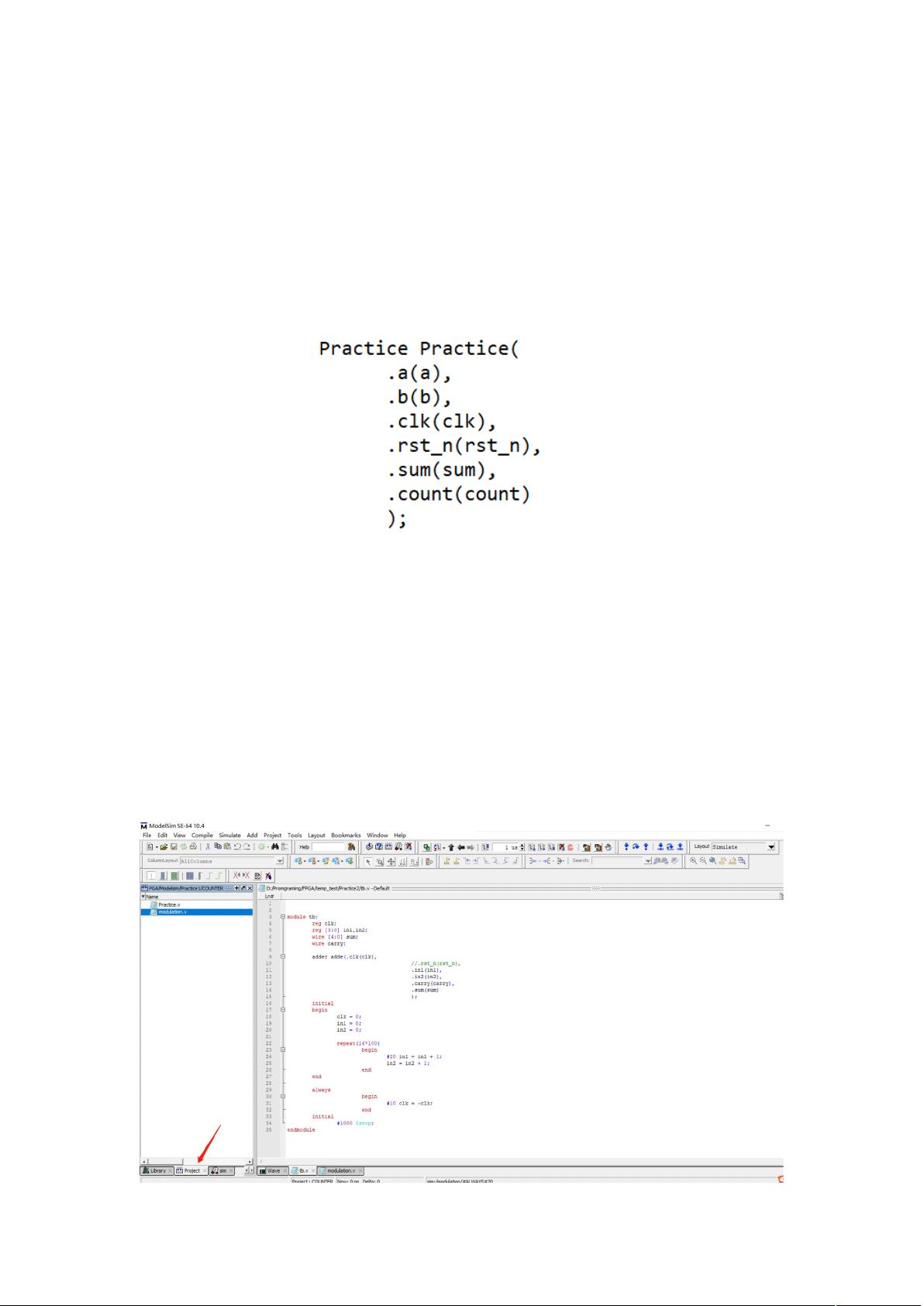

1. **新建工程**:首先需要创建一个新的工程,将testbench文件和待测试的模块文件添加到工程中。testbench文件类似于测试平台,它包含了对主模块的激励和预期响应,通常会包含一个initial模块来初始化变量。

2. **编译**:在Modelsim的project中,选择compile all命令来编译所有添加的文件。这一步骤是确保代码没有语法错误和设计逻辑的正确性。

3. **仿真**:在Library中选择testbench文件,然后右击选择simulate,开始仿真过程。如果文件有改动,记得先reload以加载最新版本。

4. **观察波形**:使用addwave命令在波形窗口添加想要观察的信号,设置仿真时间后点击run按钮,可以查看信号的变化情况。

5. **Verilog编程规范**:

- 在`always`块中生成时钟信号时,不要在条件语句中加入rst_n这样的控制信号,因为`always`块不依赖敏感列表。

- 所有输入信号必须赋初值,而输出信号不应赋初值,以防在未初始化时产生不确定行为。

- `initial`块和`always`块是并行执行的,这意味着它们可以同时开始运行。

- 控制流语句如`if`, `repeat`, `for`, `while`应该在过程块(如`always`或`initial`)中使用,就像C语言中的函数一样。

- 时钟信号的延迟表达式如`#10 forever #20 clk=~clk`会在30ns后开始翻转。

- 每次声明新的变量,都要赋予初始值,通常是0,以避免未定义的行为。

- 使用`always`块采样信号时,要遵循采样定理,确保正确捕捉信号变化;而`assign`语句用于连续赋值,不受此限制。

通过以上步骤和注意事项,用户可以有效地使用Modelsim进行Verilog设计的仿真验证,确保设计的功能正确性。在实际操作中,理解并遵循这些规则,可以避免许多常见的问题,提高仿真效率。

2019-07-31 上传

2022-07-13 上传

2023-02-27 上传

2022-05-25 上传

2021-12-03 上传

2022-10-13 上传

2022-07-09 上传

2021-09-27 上传

sk594lzh

- 粉丝: 0

- 资源: 1

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍