GN25L95: 2.5Gbps光纤模块,集成诊断监控与高速应用

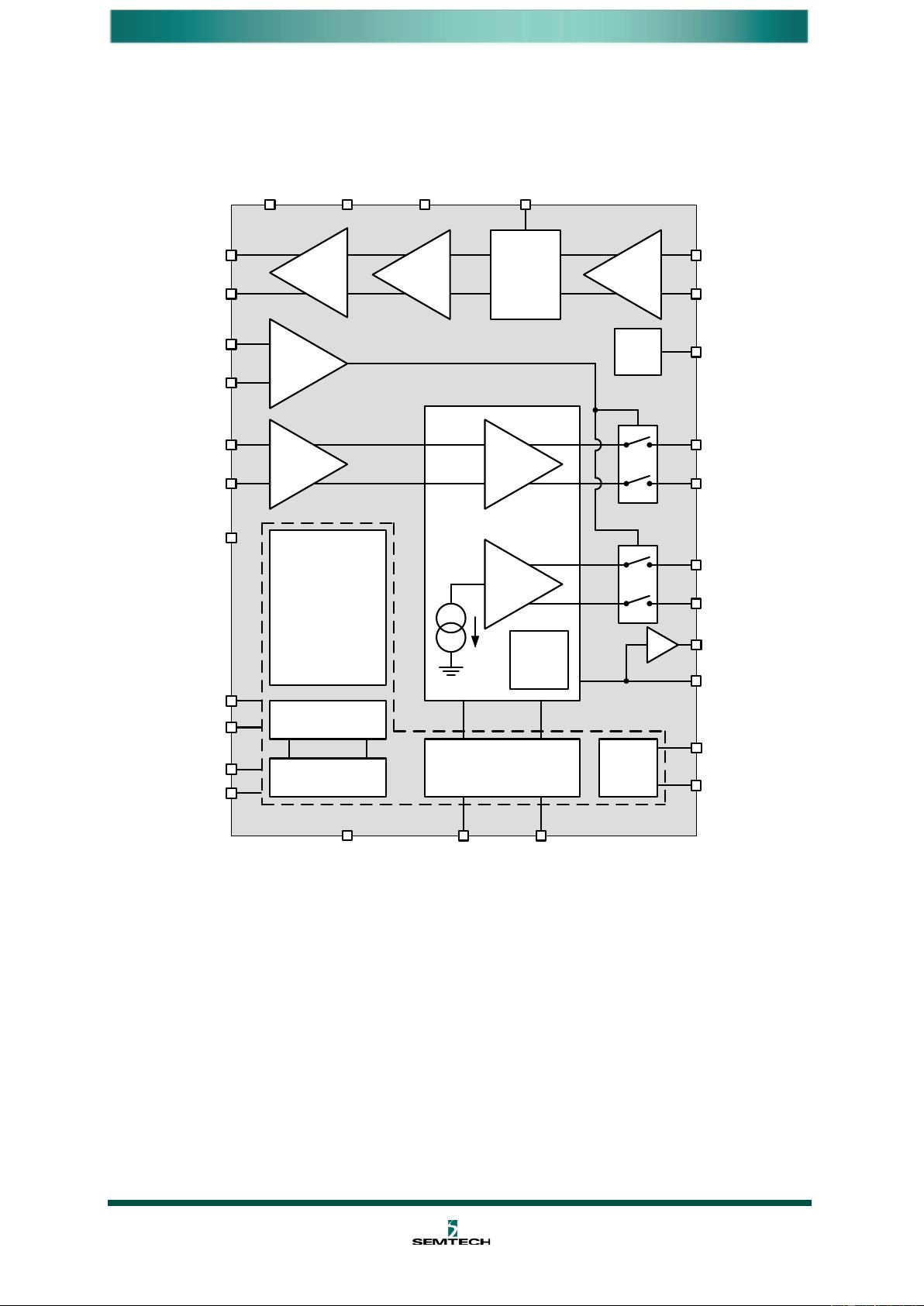

GN25L95是一款由Semtech公司提供的高性能光收发模块,专为10Gbps EPON、GPON FTTH ONT(Optical Network Unit)/ONT(Optical Network Terminal)以及BOSA-on-Board ONU(Bundled ONU with SFP Attachment)应用设计。这款模块的核心功能包括:

1. 高驱动能力:GN25L95支持高达100mA的偏置电流和90mA的调制电流输出,确保了在传输过程中的强大信号驱动能力。

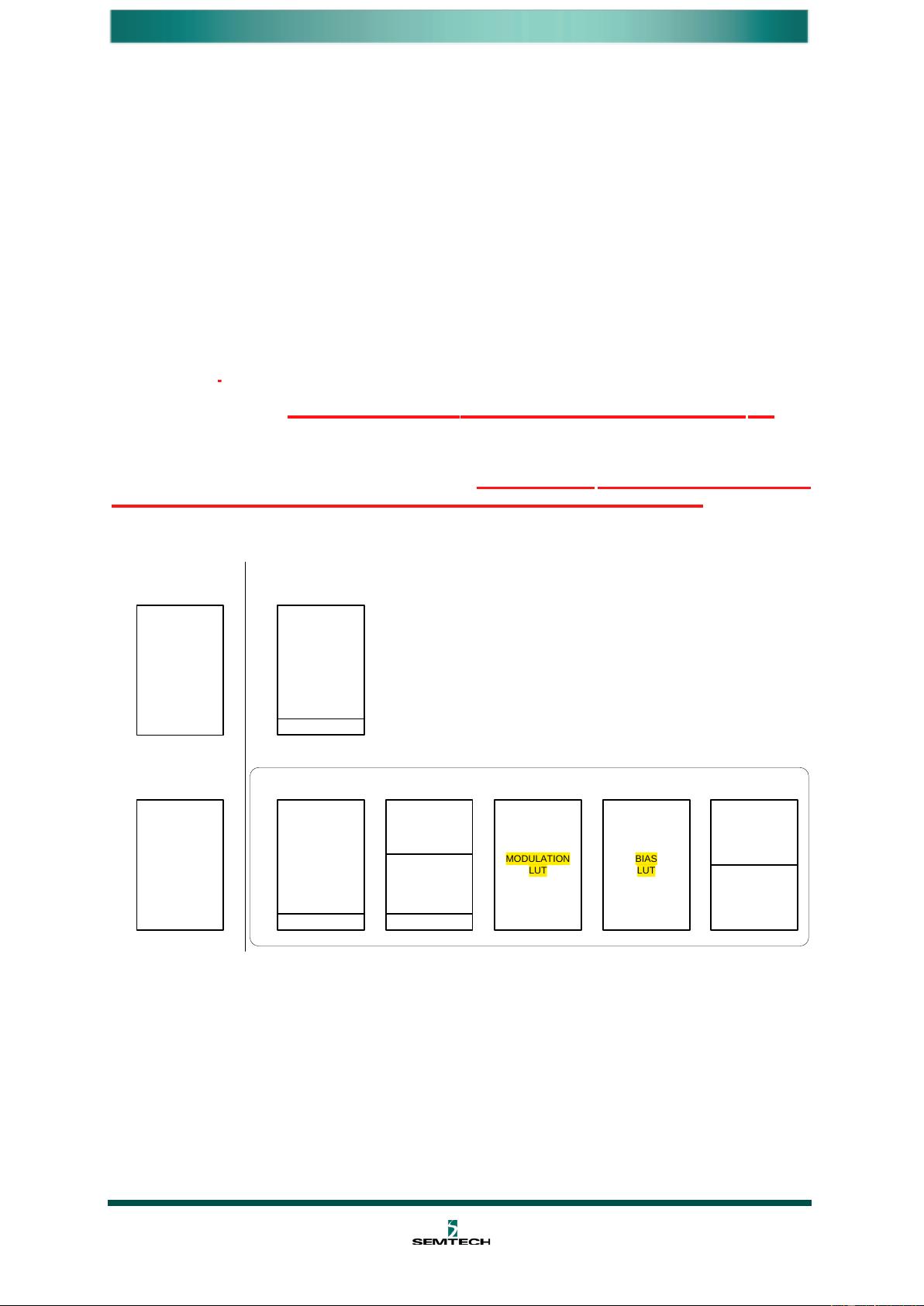

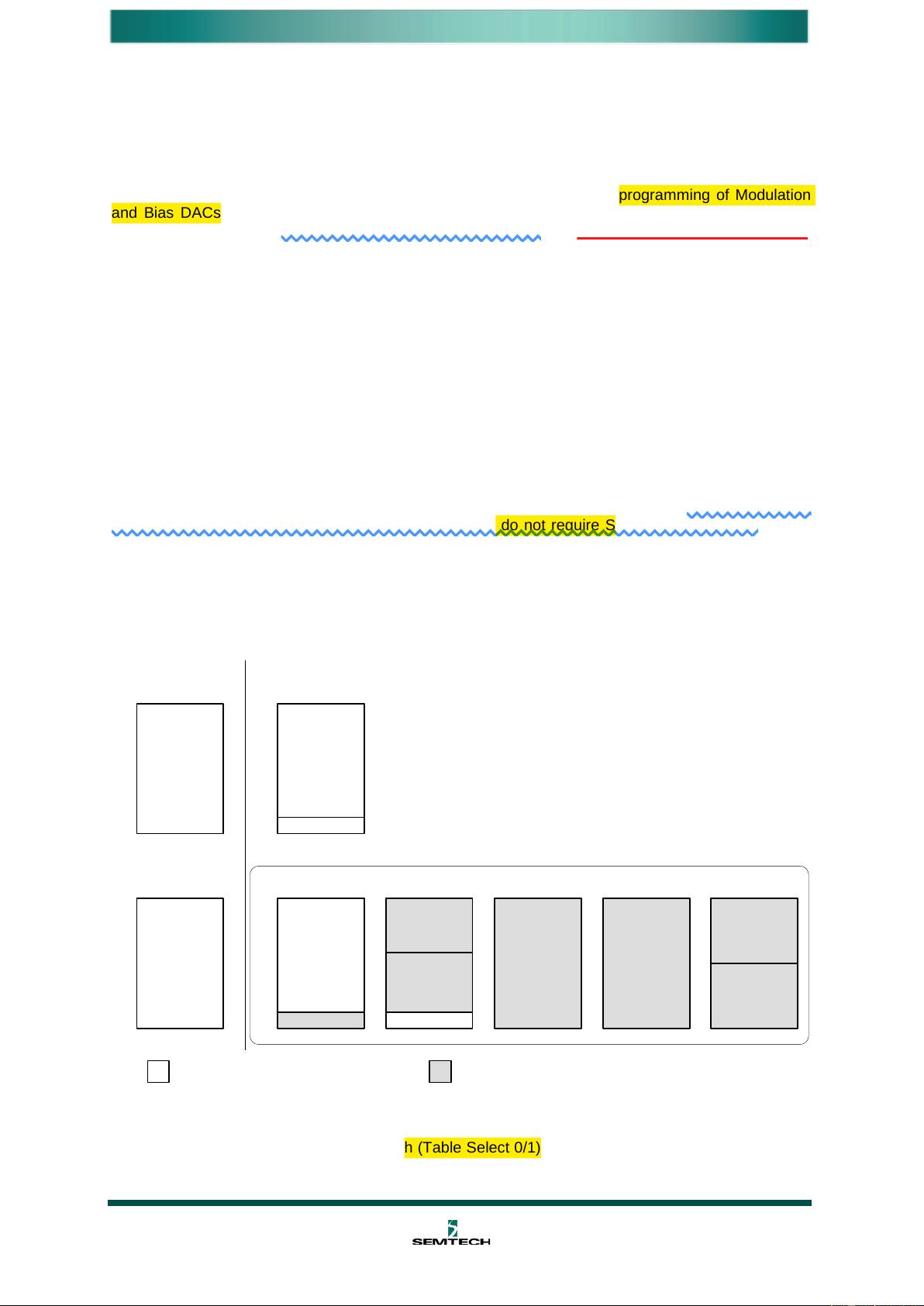

2. 数字诊断监测(DDMI, Digital Diagnostic Monitoring Interface):集成在芯片上的这项功能提供了实时的光模块状态监控,有助于快速识别并解决问题,提高系统的可靠性和维护效率。

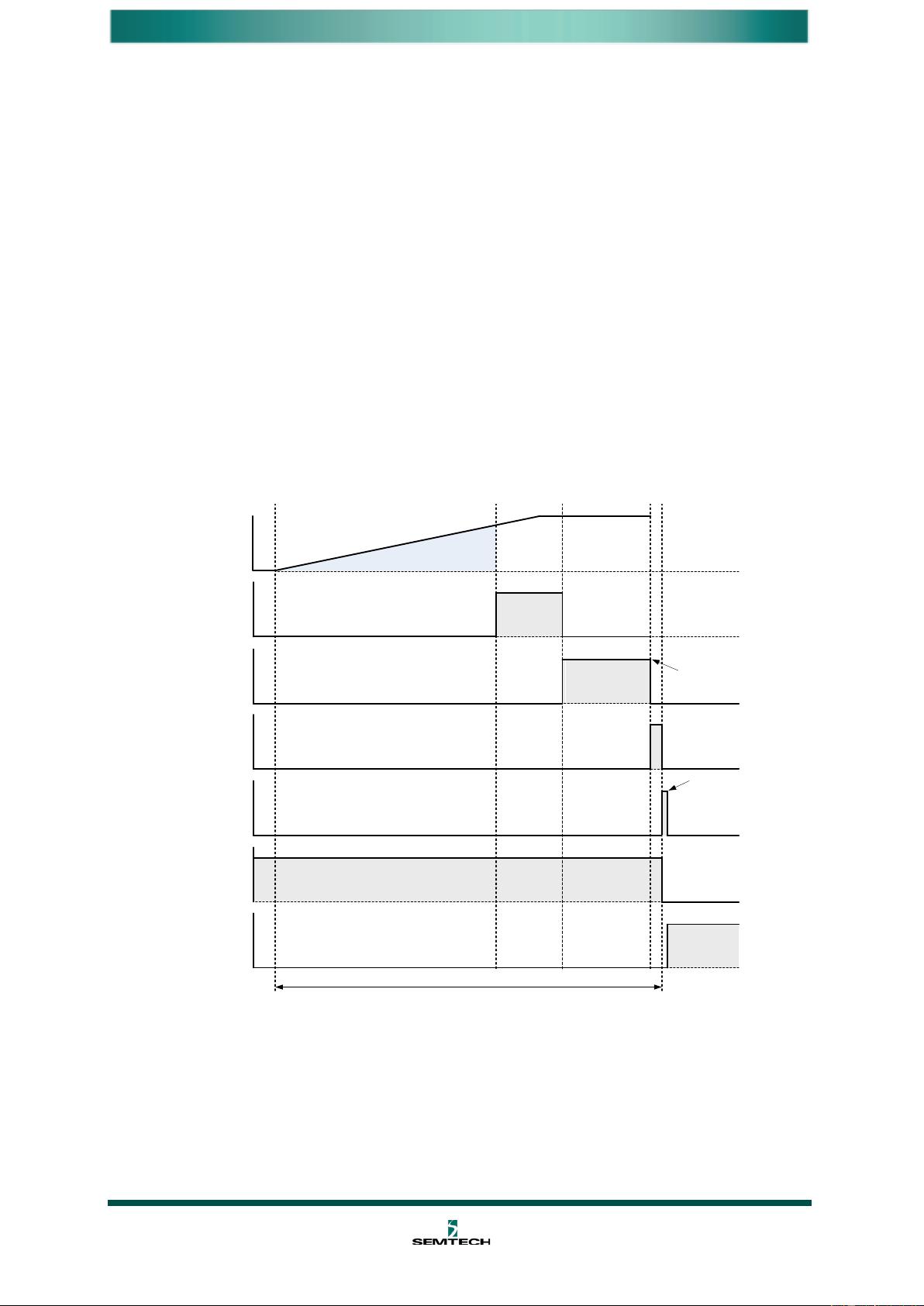

3. 自动功率控制:自动平均功率控制和自动衰减比控制功能,能动态调整发送功率,保持最佳性能,同时减少功耗。

4. 快速的突发模式设置时间:优化的电路设计使得GN25L95在突发模式下的响应迅速,减少了信号延迟,提高了通信效率。

5. 当前DAC输出:用于APD( avalanche photodiode,雪崩光电二极管)偏置控制,进一步提升了信号处理精度。

6. 安全特性:具备TX_SD和rogue ONU(非法ONU)报警功能,能够检测和防止潜在的安全威胁,保护网络稳定。

7. 功耗管理:支持电源降级和睡眠模式,有助于节能和延长模块寿命。

8. 接口兼容性:支持标准的SFF-8472接口规范,便于与各种标准光模块和设备无缝连接。

GN25L95作为一款光模块的核心组件,其设计目标是提供一个完整的解决方案,满足下一代光纤通信网络对高速、高效和智能化的需求。通过集成的数字诊断功能,可以简化系统调试,提升整体系统的性能和可靠性。无论是对于光接入网的标准化部署还是定制化应用,GN25L95都是一款值得信赖的选择。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

qq_41525477

- 粉丝: 0

最新资源

- Web远程教学系统需求分析指南

- 禅道6.2版本发布,优化测试流程,提高安全性

- Netty传输层API中文文档及资源包免费下载

- 超凡搜索:引领搜索领域的创新神器

- JavaWeb租房系统实现与代码参考指南

- 老冀文章编辑工具v1.8:文章编辑的自动化解决方案

- MovieLens 1m数据集深度解析:数据库设计与电影属性

- TypeScript实现tca-flip-coins模拟硬币翻转算法

- Directshow实现多路视频采集与传输技术

- 百度editor实现无限制附件上传功能

- C语言二级上机模拟题与VC6.0完整版

- A*算法解决八数码问题:AI领域的经典案例

- Android版SeetaFace JNI程序实现人脸检测与对齐

- 热交换器效率提升技术手册

- WinCE平台CPU占用率精确测试工具介绍

- JavaScript实现的压缩包子算法解读