TMS6455 DSP开发:启动流程与代码迁移策略

需积分: 50 121 浏览量

更新于2024-09-07

2

收藏 1.51MB PDF 举报

本文档详细介绍了TI公司TMS320C6455 DSP芯片的基础开发流程,重点围绕DSP的启动过程和烧写步骤展开。首先,开发流程从创建工程开始,针对TMS320C6455 DSP的两种启动模式进行解释:

1. **NoBoot模式**:适用于调试阶段,CCS工具直接将代码加载到L2 RAM中,DSP从该地址开始执行,便于实时调试。

2. **EMFIA8bit启动模式**:当DSP上电复位后,Bootloader (RBL) 会跳转至EMIFACE3(外部内存接口)的起始地址0xB0000000,执行后续程序。这个模式下,Bootloader位于DSP内部ROM,确保了程序的可靠启动。

文章还讨论了不同存储器区域的分配:

- L2:0x0080_0000至0x009F_FFFF,最大容量2MB,主要用于存放速度关键的代码和数据。

- L1P和L1D:分别为程序存储区和数据存储区,容量较小,分别32KB。

- DDR2:0xE000_0000至0xFFFF_FFFF,最大512MB,主要用来存储较大的应用程序和数据。

当前的开发方案是将整个应用程序映射到DDR2空间,由App_Bootloader负责初始化DDR2并迁移代码。然而,为了优化性能,提出了一个改进计划:

- 将速度敏感的代码和数据段映射到L1或L2,以提高访问速度。

- 其他非关键部分映射到DDR2,App_Bootloader负责根据需要在启动时动态加载。

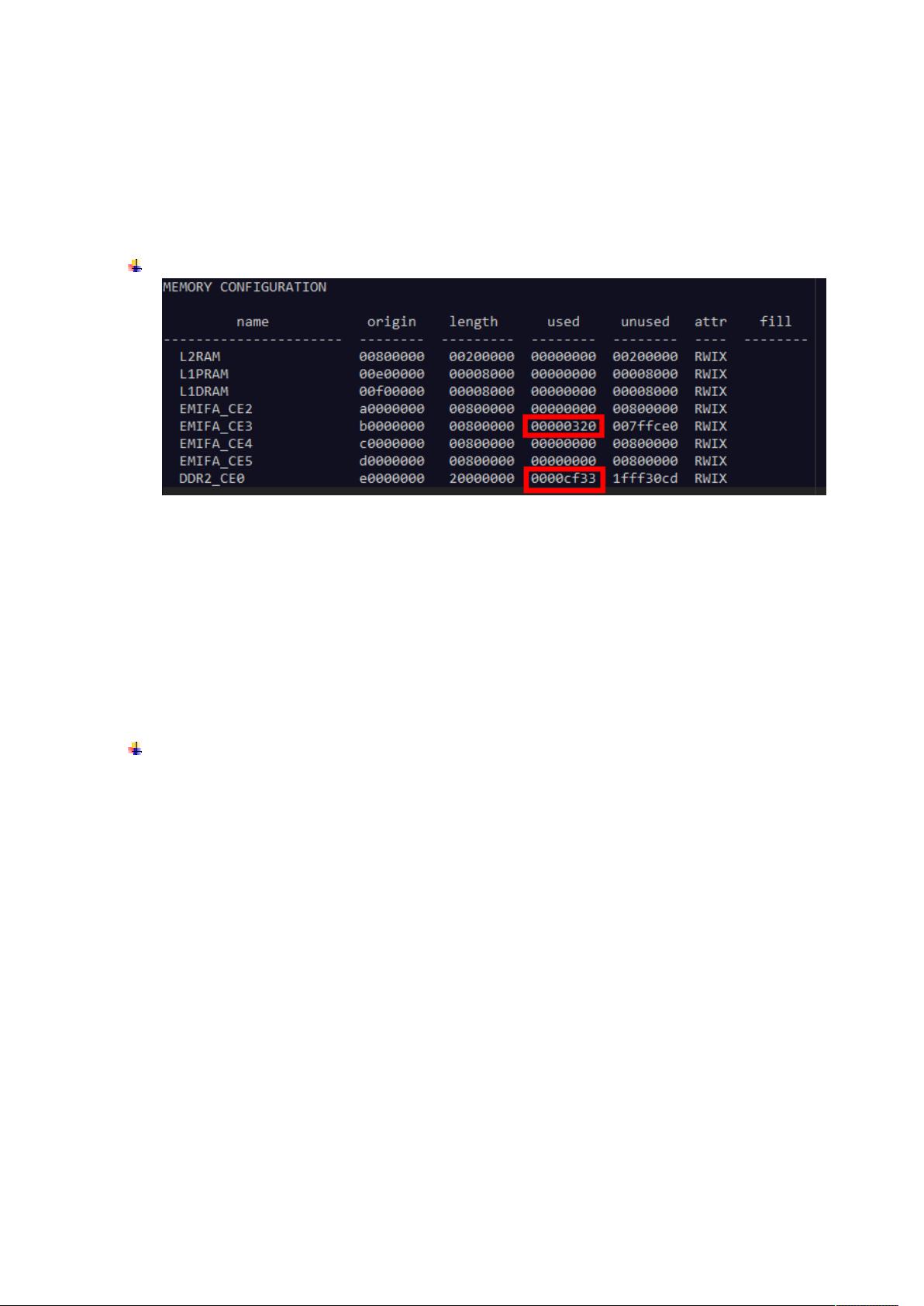

在实际操作中,涉及到创建包含App_Bootloader的可执行工程,并配置CMD文件,确保仅.app_boot段位于EMIFA_CE3区域,其他段在DDR2中执行。同时,需要生成.out文件和.map文件,.map文件用于记录代码和数据在内存中的布局,以便理解和调试。

本文档为TMS320C6455 DSP的开发人员提供了一套完整的启动流程和存储管理策略,旨在提高程序的效率和调试能力。理解这些步骤和优化方案对于编写高效且可维护的DSP应用至关重要。

2024-07-20 上传

2024-07-19 上传

2024-07-19 上传

点击了解资源详情

2020-10-23 上传

2012-08-13 上传

2011-10-24 上传

2010-03-02 上传