Verilog实验2:组合电路设计与Testbench验证

需积分: 0 190 浏览量

更新于2024-08-04

收藏 345KB DOCX 举报

"Verilog实验二1:设计和测试简单组合电路"

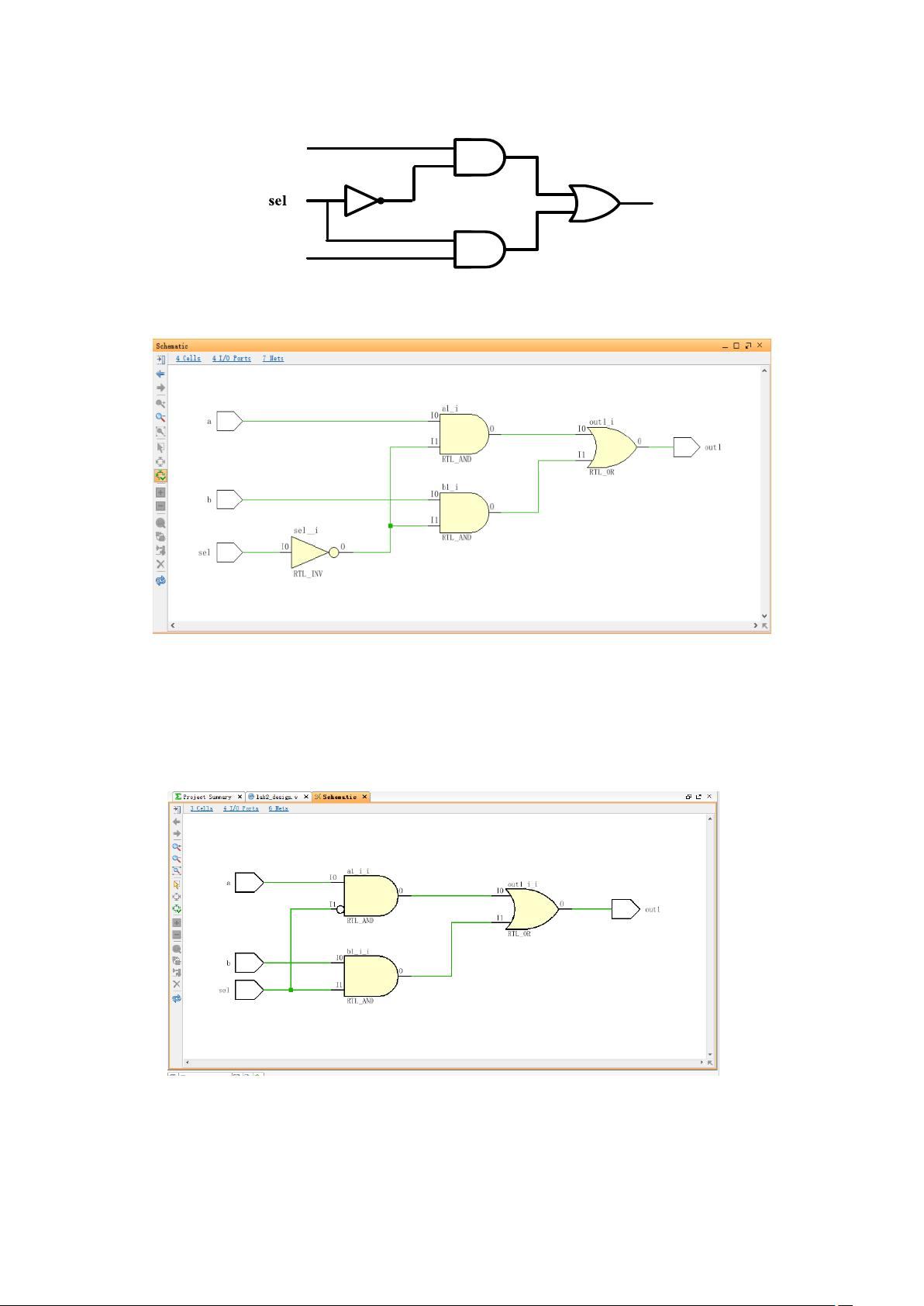

在本次"Verilog实验二1"中,学生将运用所学的Verilog语言和Vivado工具设计和测试选择器、译码器等组合逻辑电路。实验旨在深化对Verilog语言的理解,以及掌握如何通过仿真测试验证设计的正确性。

**相关知识**

1. **测试平台(Testbench)**:测试平台在硬件描述语言设计中扮演着关键角色,用于模拟实际电路环境,验证设计的功能。Testbench通常由三部分组成:产生仿真激励、应用这些激励到被测试模块并收集输出响应,最后将输出响应与期望值比较以确保设计正确。

2. **Verilog仿真**:Verilog是一种硬件描述语言,用于描述数字系统的结构和行为。在仿真中,我们使用Testbench来创建输入信号,观察输出响应,并判断设计是否符合预期。

3. **Testbench结构**:典型的Testbench包括`timescale`声明以设定时间单位和精度,一个没有输入和输出端口的测试模块,局部`reg`和`wire`变量声明,以及使用`initial`和`always`语句产生的激励波形。Testbench还需要实例化被测试模块并监控输出。

**实验步骤**

1. **理解任务**:首先,学生需要明确任务,即设计选择器和译码器等组合电路,并准备进行测试。

2. **设计电路**:使用Verilog语言,按照组合逻辑电路的逻辑功能编写代码,例如2选1选择器。

3. **创建Testbench**:编写与设计模块相对应的Testbench模块,包括输入和输出变量的声明,以及生成各种可能的输入激励。

4. **仿真运行**:在Vivado环境中,编译并运行Testbench,观察仿真结果。

5. **分析波形**:利用Vivado的波形显示工具,检查输出波形是否与预期一致。

6. **问题解决**:如果发现设计错误或不符合预期,需要调试代码,修改设计并重新仿真。

7. **记录与反馈**:记录实验过程中的问题、解决方案以及个人心得,提供改进建议。

在实验过程中,学生将逐步熟练掌握Verilog语法,了解如何编写Testbench,以及如何利用Vivado进行仿真测试。这不仅加深了对Verilog语言的理解,还锻炼了逻辑思维和问题解决能力。

1341 浏览量

4803 浏览量

109 浏览量

1774 浏览量

2010-04-13 上传

136 浏览量

104 浏览量

344 浏览量

KerstinTongxi

- 粉丝: 25

- 资源: 277