FPGA实现的8位数码管扫描显示电路设计与解析

版权申诉

"该资源是关于基于FPGA的8位数码管扫描显示电路设计的教程,旨在帮助读者理解和实现FPGA开发中的8位数码管显示技术。内容包括实验目的、实验原理、实验内容以及相关VHDL代码示例。"

在FPGA开发中,8位数码管扫描显示电路设计是一项基础而重要的技能。这项技术常用于数字系统的用户界面,以直观地展示数值或字符信息。实验目的是为了让学生掌握数码管扫描显示的工作原理,熟悉元件例化语句的使用,以及深化对VHDL中的CASE语句和多层次设计方法的理解。

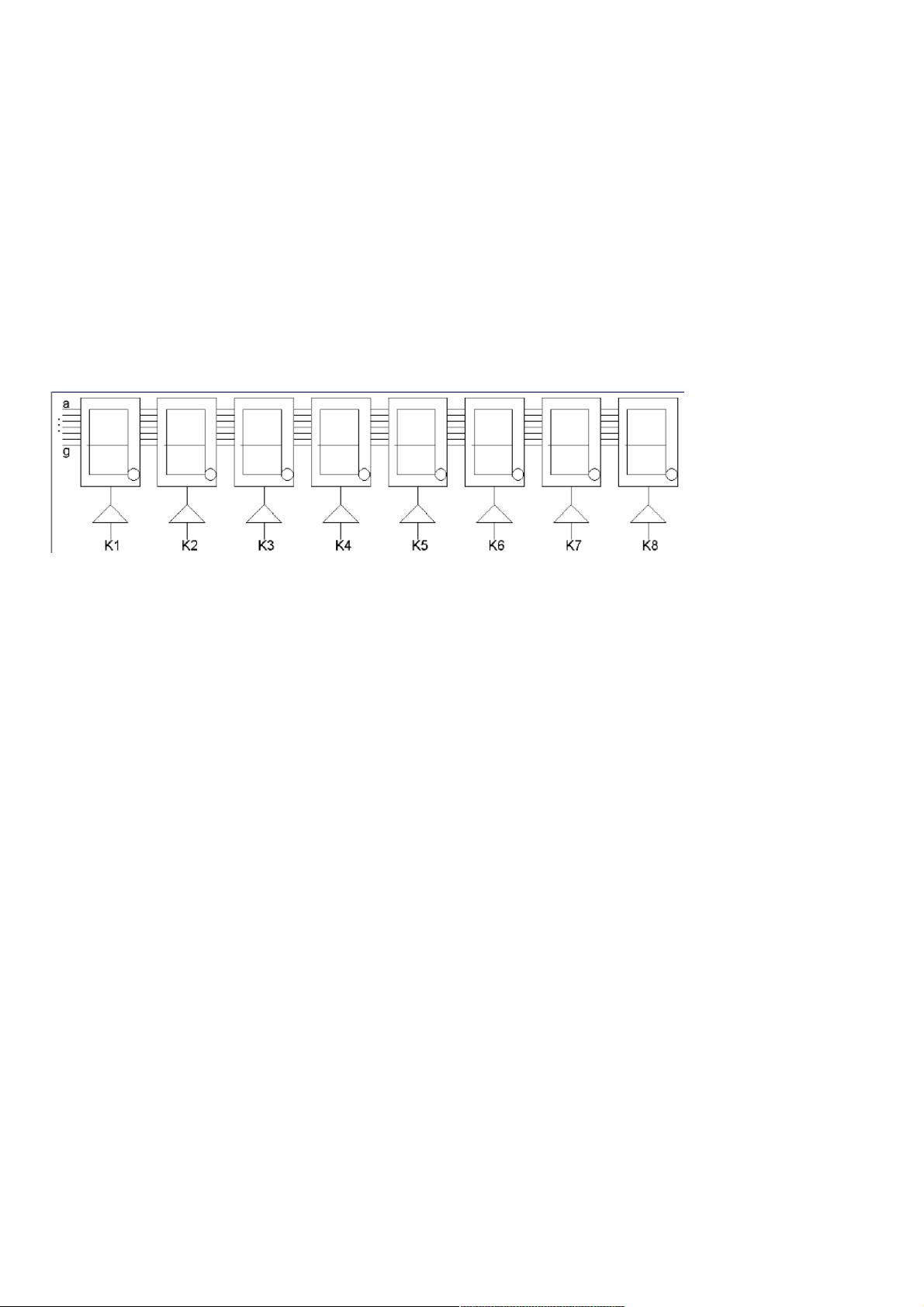

实验原理基于数码管的共阴极或共阳极设计,其中8个数码管的段h至a(h代表小数点)串联在一起,而每个数码管的选通由独立的选通信号k1到k8控制。当某一选通信号为高电平时,对应的数码管会显示来自段信号的数据,其余数码管则关闭。通过周期性改变这些选通信号,可以实现逐个数码管的扫描显示,从而在8个数码管上依次显示一组数字或字符。

实验内容包括设计VHDL程序来生成扫描计数信号(cnt8)、7段译码输出以及数码管的选通扫描。在提供的VHDL代码示例中,CLK是扫描时钟,SG是7段控制信号,BT是位选控制信号。程序中的cnt8是一个3位计数器,用于驱动扫描过程;P2进程生成扫描计数,P3进程负责7段译码,P1进程执行数码管的选通。例如,当cnt8为"001"时,K2选通,数码管显示"3"。

通过这样的设计,随着cnt8的递增,可以在8个数码管上连续显示"13579bdf"。在实际操作中,开发者需要进行仿真验证设计的功能是否正确,然后将设计下载到FPGA硬件中进行实际运行测试。

基于FPGA的8位数码管扫描显示电路设计涉及到的关键知识点包括:

1. 数码管的工作原理与驱动方式

2. FPGA的逻辑设计基础

3. VHDL编程语言,特别是元件例化、CASE语句和计数器的设计

4. 扫描显示技术,包括选通信号和数据同步

5. 逻辑综合与仿真验证

6. FPGA硬件下载与实际应用

理解并掌握这些知识对于FPGA开发者来说至关重要,因为它们构成了数字系统可视化界面设计的基础。通过此类实验,开发者能够提升自己的逻辑设计能力和实践经验,为进一步复杂的FPGA项目奠定基础。

1038 浏览量

362 浏览量

140 浏览量

351 浏览量

2021-07-13 上传

2022-02-16 上传

122 浏览量

2022-04-22 上传

_webkit

- 粉丝: 31

- 资源: 1万+

最新资源

- 高质量c++ c编程指南

- WPF技术白皮书 下一代互联网主流开发技术

- 整合Flex和Java--配置篇.pdf

- unix 编程艺术指导

- 词法分析器的设计与实现

- TD7.6管理员指南

- ACE Programming Guide

- 手机游戏门户网站建设方案

- 搜索引擎技术手工索引

- 衡水信息港投资计划书 网站建设方案

- 地方门户网站策划书(转载)

- [计算机科学经典著作].SAMS.-.Tricks.Of.The.Windows.Game.Programming.Gurus.-.Fundamentals.Of.2D.And.3D.Game.Programming.[eMule.ppcn.net].pdf

- Embedded_Linux_on_ARM.pdf

- SQL语言艺术(英文版)

- Windows File Systems _FAT16, FAT32, NTFS_.pdf

- C Programming Language 2nd Edition(K & R).pdf