Xilinx FPGA UG901:Vivado Synthesis方法与支持的硬件描述语言

需积分: 5 196 浏览量

更新于2024-06-20

收藏 3.1MB PDF 举报

Xilinx FPGA UG901是一份详细的技术文档,专注于AMD Vivado设计套件中的FPGA综合(synthesis)功能。这份文档版本为v2023.1,发布日期为2023年6月9日。综合是将RTL(寄存器传输级)设计语言如SystemVerilog、Verilog和VHDL转换成门级逻辑的过程,这是FPGA设计的关键步骤之一。Vivado的综合流程是定时驱动的,并且特别优化了对内存的处理,确保高性能表现。

Vivado支持多种标准的设计语言,包括IEEE的SystemVerilog统一硬件设计规范(IEEE Std 1800-2012)、IEEE Verilog硬件描述语言(IEEE Std 1364-2005)以及VHDL语言标准(IEEE Std 1076-2002,还包括2008年的更新)。此外,Vivado允许混合使用不同语言,但值得注意的是,它不支持UCF约束,推荐用户将其迁移到Xilinx设计约束(XDC)中,这符合业界标准的Synopsys设计约束(SDC)。

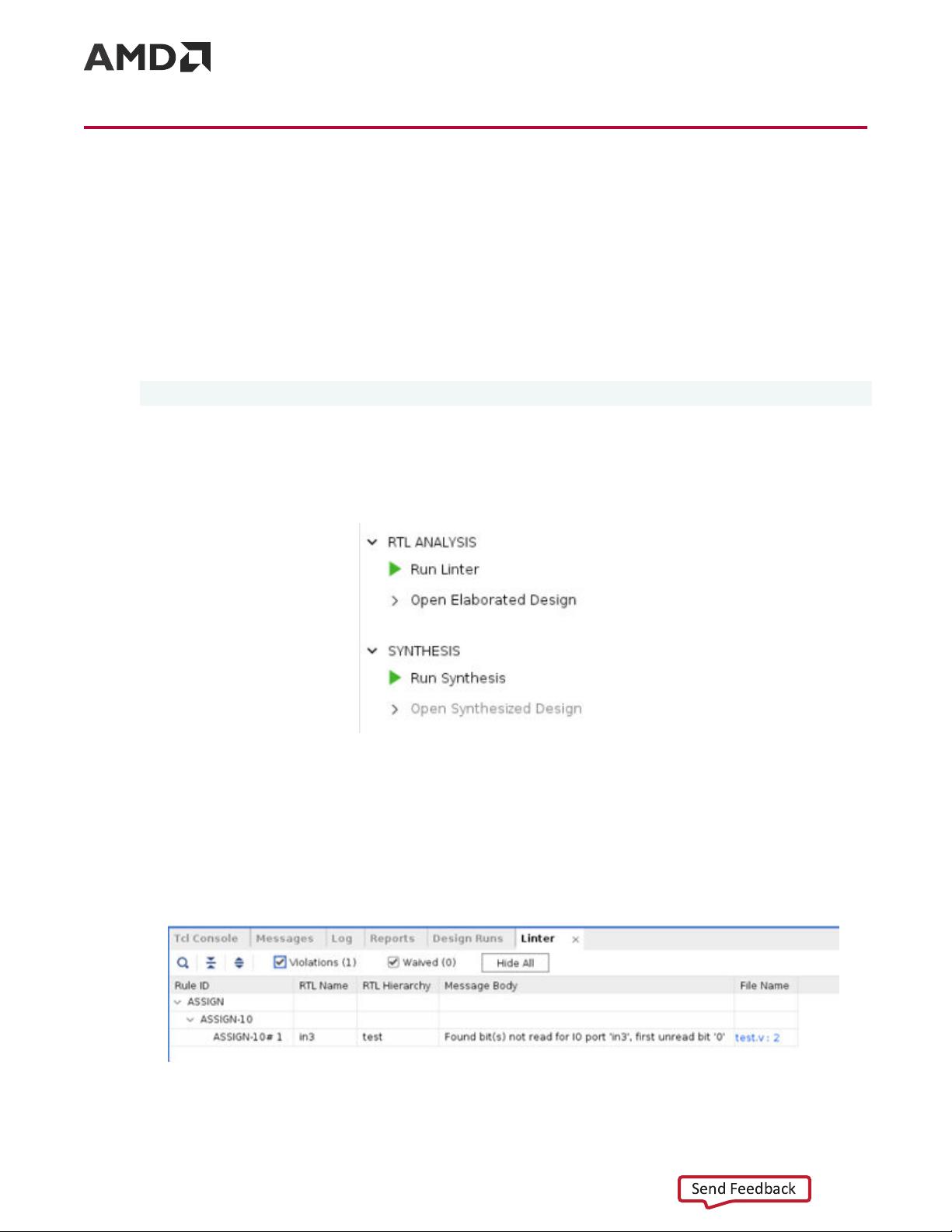

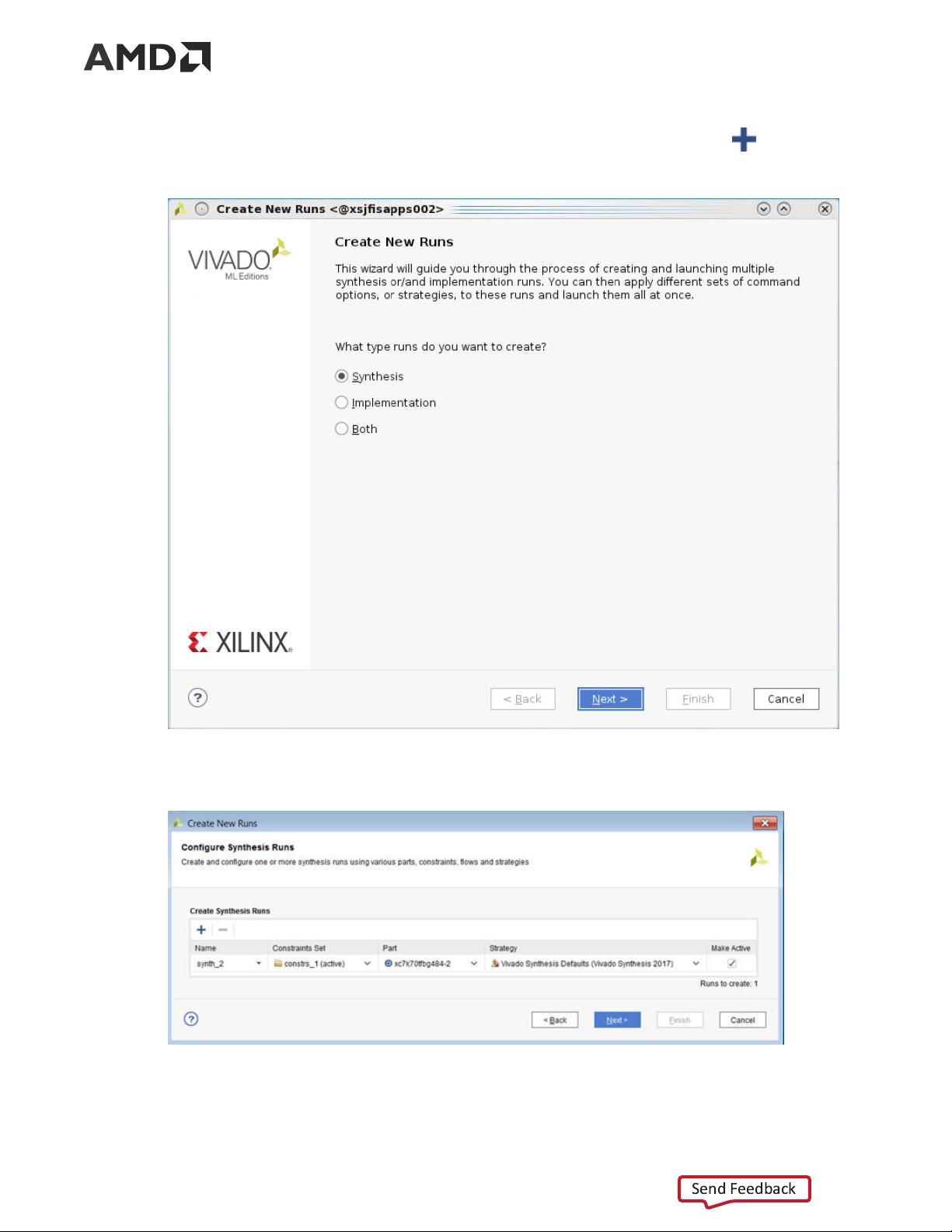

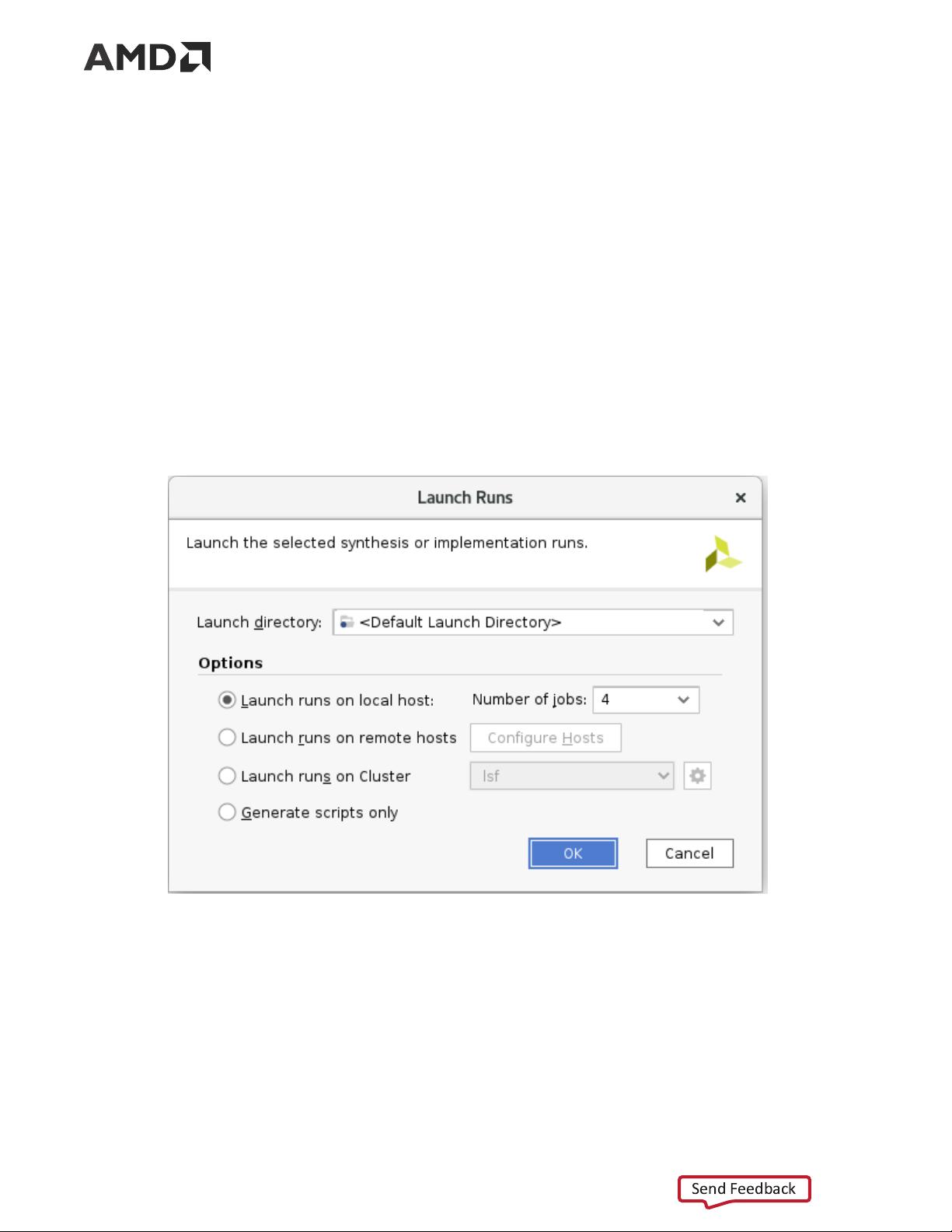

文档详细讲解了综合方法论,如何设置从底层向上、脱离上下文的工作流,以及增量综合的过程。对于第三方合成工具的集成也有所提及,如何在Vivado环境中运行这些工具,并提供监控综合运行的方法。用户可以分析综合结果,以评估设计的效率和性能。同时,文档还介绍了如何利用综合后的设计环境进行进一步的探索和调试。

文档的目的是为了帮助设计者充分利用Vivado工具进行高效、精确的FPGA设计,确保语言的包容性和行业最佳实践。随着AMD致力于消除产品和文档中的非包容性语言,这份指南也在不断更新以适应这些变化,与业界标准保持一致。因此,无论你是初级还是经验丰富的FPGA开发者,这份文档都是理解和优化设计过程的重要参考资料。

2023-11-05 上传

2023-10-28 上传

2023-10-21 上传

2023-07-27 上传

2023-08-22 上传

2023-08-31 上传

2024-01-13 上传

2023-09-08 上传

2023-06-26 上传

cckkppll

- 粉丝: 5833

- 资源: 91

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库