VHDL实现16位加减可控计数器及仿真分析

需积分: 10 54 浏览量

更新于2024-09-10

4

收藏 213KB DOCX 举报

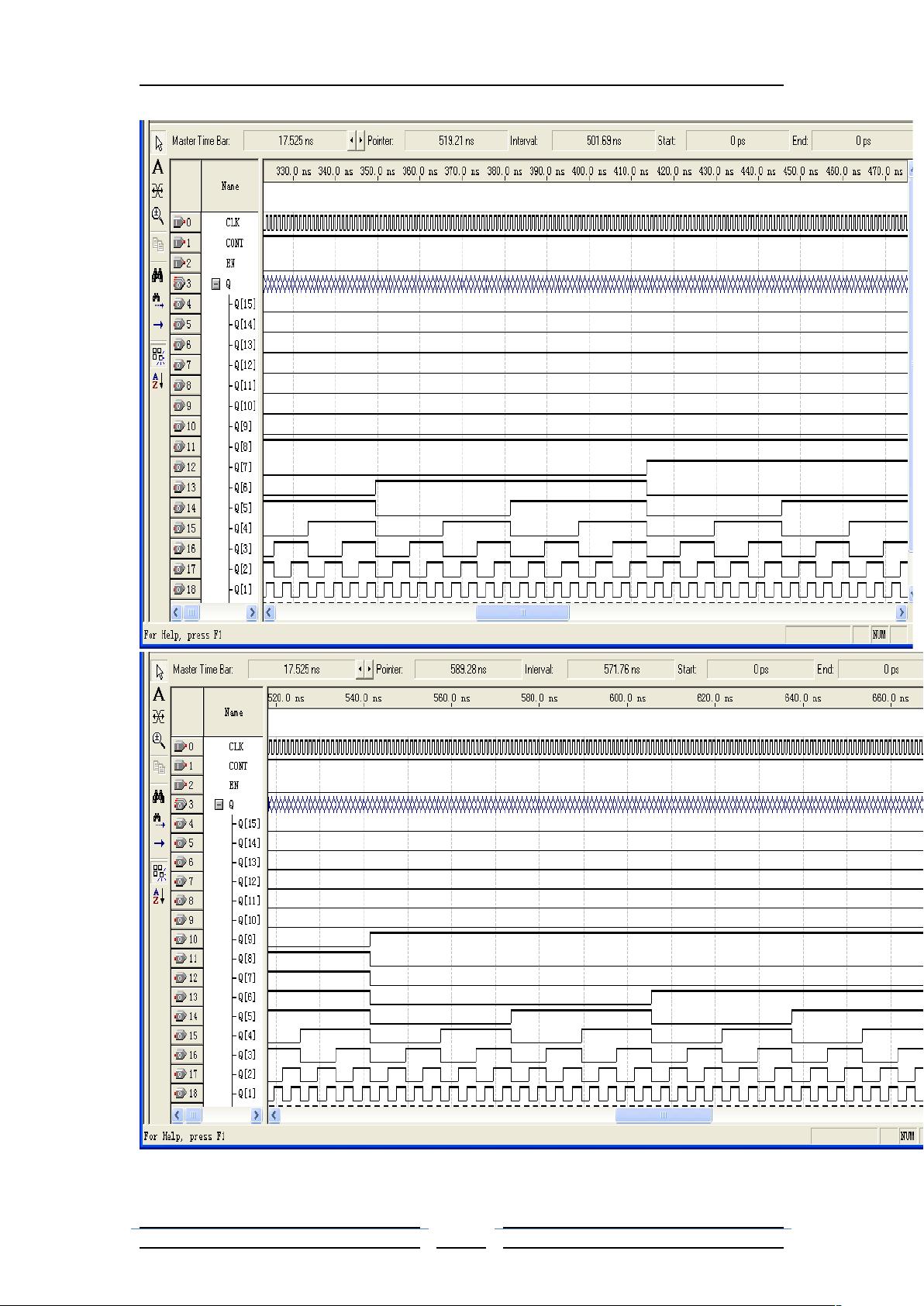

"EDA大作业涉及的是电子设计自动化(EDA)中的一个项目,具体是一个具有异步清零和计数使能功能的16位二进制加减可控计数器的设计与实现。作业要求包括设计流程、VHDL程序编写、波形仿真验证以及撰写设计实验报告。在解答中,提供了实体定义、结构体实现,以及加法和减法情况下的仿真结果概述。最后,作者分享了实验的心得体会,强调了这次实验对于VHDL编程技能和数字电路知识的提升作用,同时也指出了自己在编程思维方面的不足,表示需要进一步提高。"

在这个EDA大作业中,学生需要设计一个16位的计数器,该计数器具备以下特性:

1. 异步清零:计数器可以在任何时候通过一个独立的清零信号(RST)被复位到零状态,不受时钟(CLK)的影响。

2. 计数使能:只有当使能信号(EN)为高电平时,计数操作才进行。如果使能信号为低电平,计数器将保持当前值不变。

3. 可控加减:计数器根据输入的CONT信号决定是加1还是减1。

VHDL代码展示了一个实体(EX_6)和其对应的结构体(BHV1),用于实现这个计数器。实体声明了输入时钟(CLK)、清零(RST)、使能(EN)、计数方向(CONT)和输出进位(CO)及计数值(Q)。结构体中定义了一个内部信号Q1,用于存储计数值,并在时钟边沿触发器中处理计数操作。在处理过程中,首先判断清零信号,然后检查使能信号,根据使能和计数方向决定是否加1或减1。

仿真结果部分展示了加法和减法两种情况下的计数器行为,这通常是通过EDA工具生成的波形图来体现,但具体的波形细节没有在此给出。这部分的目的是验证设计是否按预期工作。

实验心得部分表达了作者对VHDL编程、波形仿真以及数字电路理解的增强,同时也认识到自己在编程思维方面存在的不足,表示将继续努力提高。

这个EDA大作业涵盖了数字逻辑设计的基本概念,包括状态机设计、VHDL编程和硬件验证,对于提升学生的综合设计能力具有重要作用。

369 浏览量

582 浏览量

460 浏览量

620 浏览量

132 浏览量

1131 浏览量

langhuayiduo

- 粉丝: 1

- 资源: 1

最新资源

- Zigbee入门学习

- at&t 部分语法大 其中的一个小块

- ARM嵌入式系统实验教程(二)附加实验教程

- NETBEANS RCP.PDF

- 基于超混沌的FM_DCSK系统的性能分析.pdf

- GPRS模块Q39的介绍

- 《effective software testing》 addison wesley 著

- unix/linux系统管理

- 基于ORACLE数据融合的一卡通系统的实现

- java西安公司考试考试资源

- FPGA设计的经验谈

- RestFul_Rails_Dev_v_0.1

- 软件工程师笔试题目(应聘)

- 宫东风考研英语讲座.宫东风考研英语讲座

- ARM嵌入式WINCE实践教程

- SCCP信令原理介绍