TAS5548

www.ti.com.cn

ZHCSAJ3A –NOVEMBER 2012 –REVISED APRIL 2015

Feature Description (continued)

7.3.4 LRCKO and SCLKO

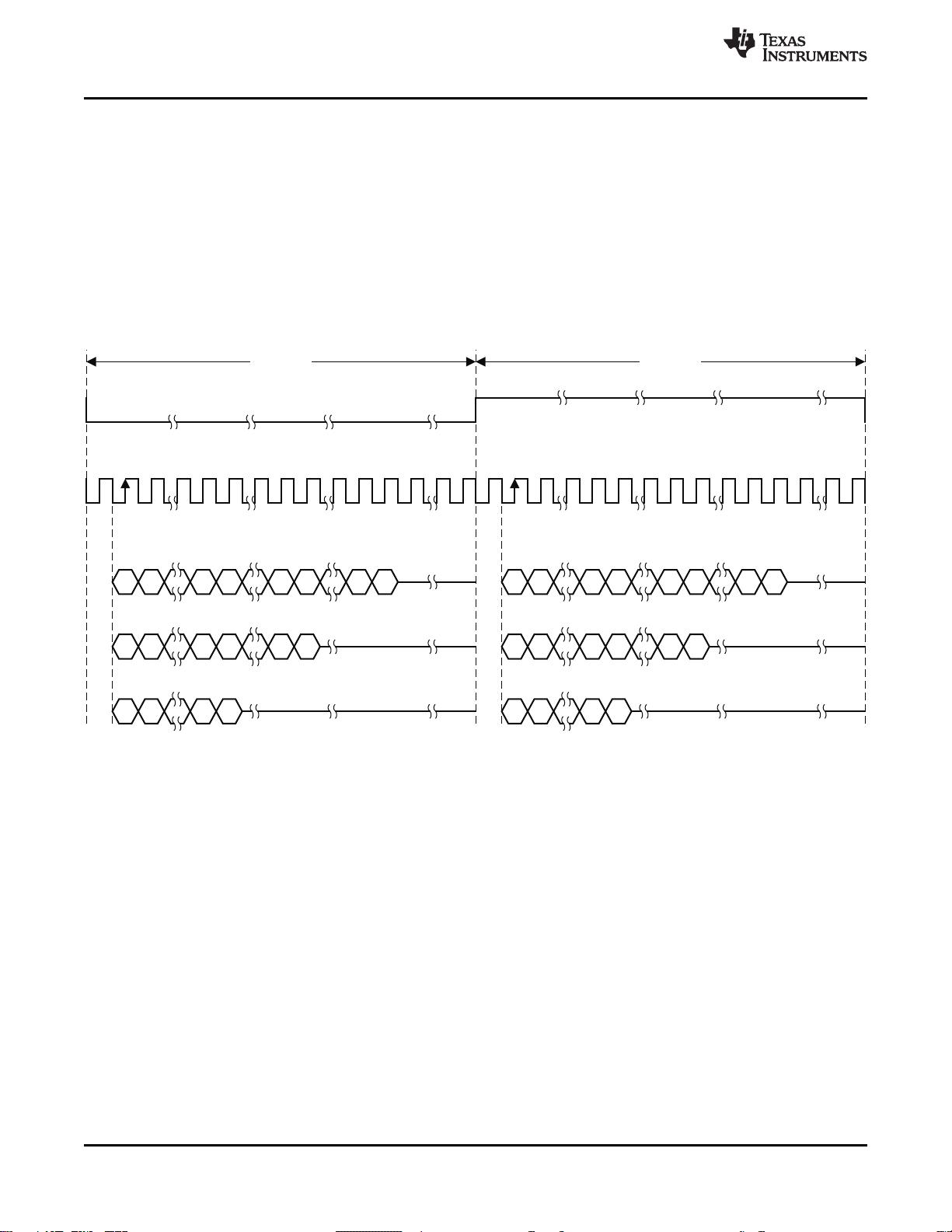

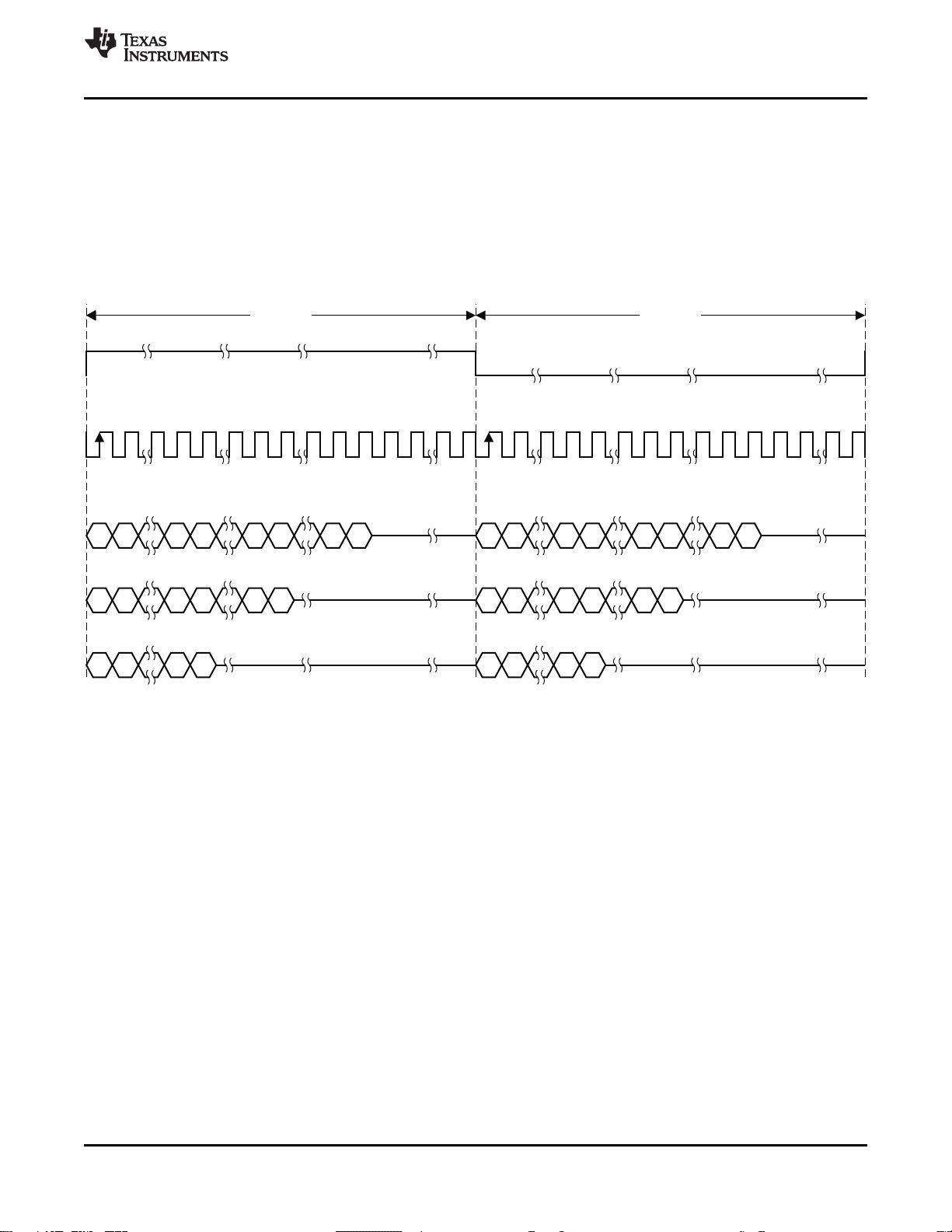

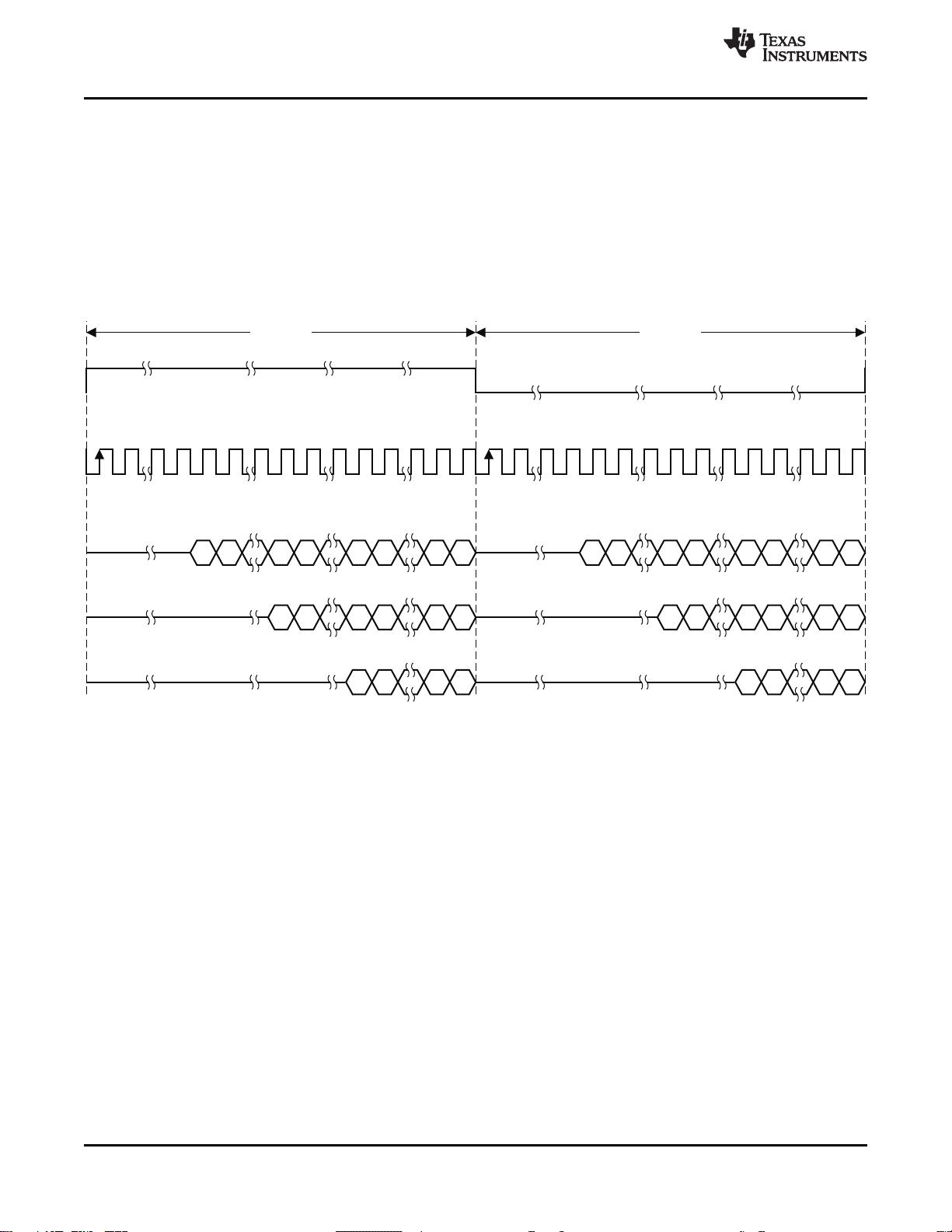

There are output pins for LRCLK output and SCK output. As the SDIN5 rate (which always follow internal sample

rate) and the SDOUT rate (which is 44.1 kHz or 48 kHz) is different, the LRCLKO will be the internal sample rate

(96 kHz or 192 kHz) when SDIN5 is activated (SDOUT is not available) and it will be 44.1 kHz or 48 kHz when

SDOUT is available. The SCLKO will be always 64x LRCLKO.

8.5 Master Clock Output (MCLKO) Master clock is generated from the MCLK input itself. There is a clock divider

with division factor of 4, 2 or 1 that can be selected from. The default is no division

7.3.5 PWM Features

The TAS5548 has eight channels of high-performance digital PWM modulators that are designed to drive

switching output stages (back ends) in both single-ended (SE) and bridge-tied-load (BTL) configurations. The

device uses noise-shaping and sophisticated, error-correction algorithms to achieve high power efficiency and

high-performance digital audio reproduction. The TAS5548 uses an AD/BD/Ternary PWM modulation scheme

combined with a fourth-order noise shaper to provide a >105-dB SNR from 20 Hz to 20 kHz.

The PWM section accepts 32-bit PCM data from the DAP and outputs eight PWM audio output channels

configurable as either:

• Six channels to drive power stages and two channels to drive a differential-input active filter to provide a

separately controllable stereo lineout

• Eight channels to drive power stages

The PWM section provides a headphone PWM output to drive an external differential amplifier like the

TPA6139A2. The headphone circuit uses the PWM modulator for channels 1 and 2. The headphone does not

operate while the six or eight back-end drive channels are operating. The headphone is enabled via a

headphone-select terminal.

The PWM section also contains the power-supply volume control (PSVC) PWM.

The interpolator, noise shaper, and PWM sections provide a PWM output with the following features:

• Up to 8× oversampling

– 4× at f

S

= 88.2 kHz, 96 kHz

– 2× at f

S

= 176.4 kHz, 192 kHz

• Fourth-order noise shaping

• 105-dB dynamic range 0–20 kHz (TAS5548 + TAS5614 system measured at speaker terminals)

• THD < 0.01%

• Adjustable modulation limit of 87.4% to 99.2%

• 3.3-V digital signal

7.3.5.1 DC Blocking (High-Pass Filter Enable/Disable)

Each input channel incorporates a first-order, digital, high-pass filter to block potential dc components. The filter

–3-dB point is approximately 2-Hz at the 96-kHz sampling rate. The high-pass filter can be enabled and disabled

via the I

2

C system control register 1 (0x03 bit D7). The default setting is 1 (high-pass filter enabled).

7.3.5.2 AM Interference Avoidance

Digital amplifiers can degrade AM reception as a result of their RF emissions. Texas Instruments' patented AM

interference-avoidance circuit provides a flexible system solution for a wide variety of digital audio architectures.

During AM reception, the TAS5548 adjusts the radiated emissions to provide an emission-clear zone for the

tuned AM frequency. The inputs to the TAS5548 for this operation are the tuned AM frequency, the IF frequency,

and the sample rate. This PWM rate modification is done by modifying the output rate of the Sample Rate

Converter, and the following DSP and PWM modulator.

7.3.6 TAS5548 Controls and Status

The TAS55 48 provides control and status information from both the I

2

C registers and device pins.

Copyright © 2012–2015, Texas Instruments Incorporated 19