Rev. A | Page 13 of 80 | July 2011

ADSP-BF504/ADSP-BF504F/ADSP-BF506F

Each mailbox consists of eight 16-bit data words. The data is

divided into fields, which includes a message identifier, a time

stamp, a byte count, up to 8 bytes of data, and several control

bits. Each node monitors the messages being passed on the net-

work. If the identifier in the transmitted message matches an

identifier in one of its mailboxes, the module knows that the

message was meant for it, passes the data into its appropriate

mailbox, and signals the processor of message arrival with an

interrupt.

The CAN controller can wake up the processor from sleep mode

upon generation of a wake-up event, such that the processor can

be maintained in a low-power mode during idle conditions.

Additionally, a CAN wake-up event can wake up the on-chip

internal voltage regulator from the powered-down

hibernate state.

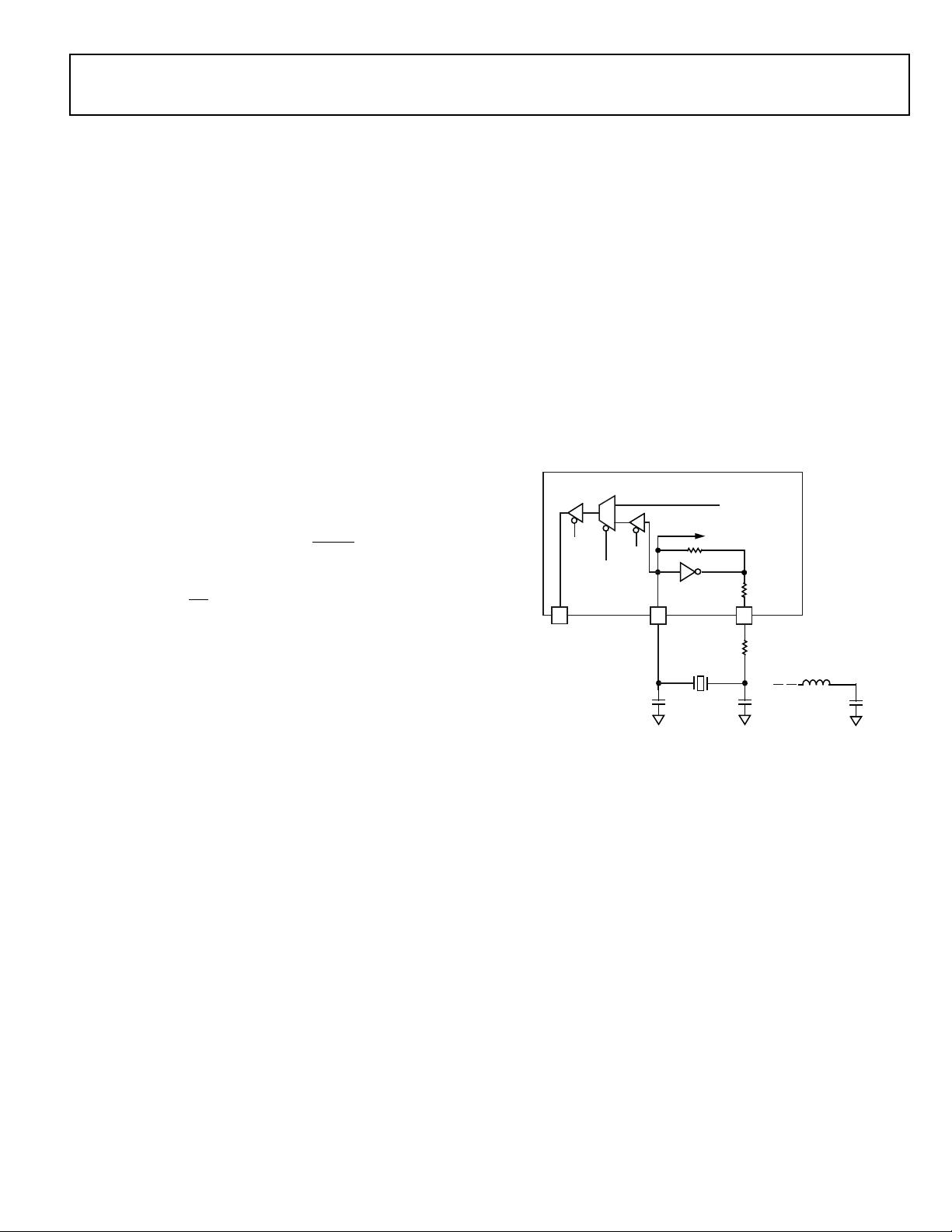

The electrical characteristics of each network connection are

very stringent. Therefore, the CAN interface is typically divided

into two parts: a controller and a transceiver. This allows a sin-

gle controller to support different drivers and CAN networks.

The ADSP-BF50x CAN module represents the controller part of

the interface. This module’s network I/O is a single transmit

output and a single receive input, which connect to a line

transceiver.

The CAN clock is derived from the processor system clock

(SCLK) through a programmable divider and therefore does not

require an additional crystal.

TWI CONTROLLER INTERFACE

The processors include a 2-wire interface (TWI) module for

providing a simple exchange method of control data between

multiple devices. The TWI is compatible with the widely used

I

2

C

®

bus standard. The TWI module offers the capabilities of

simultaneous master and slave operation, support for both 7-bit

addressing and multimedia data arbitration. The TWI interface

utilizes two pins for transferring clock (SCL) and data (SDA)

and supports the protocol at speeds up to 400K bits/sec. The

TWI interface pins are compatible with 5 V logic levels.

Additionally, the TWI module is fully compatible with serial

camera control bus (SCCB) functionality for easier control of

various CMOS camera sensor devices.

PORTS

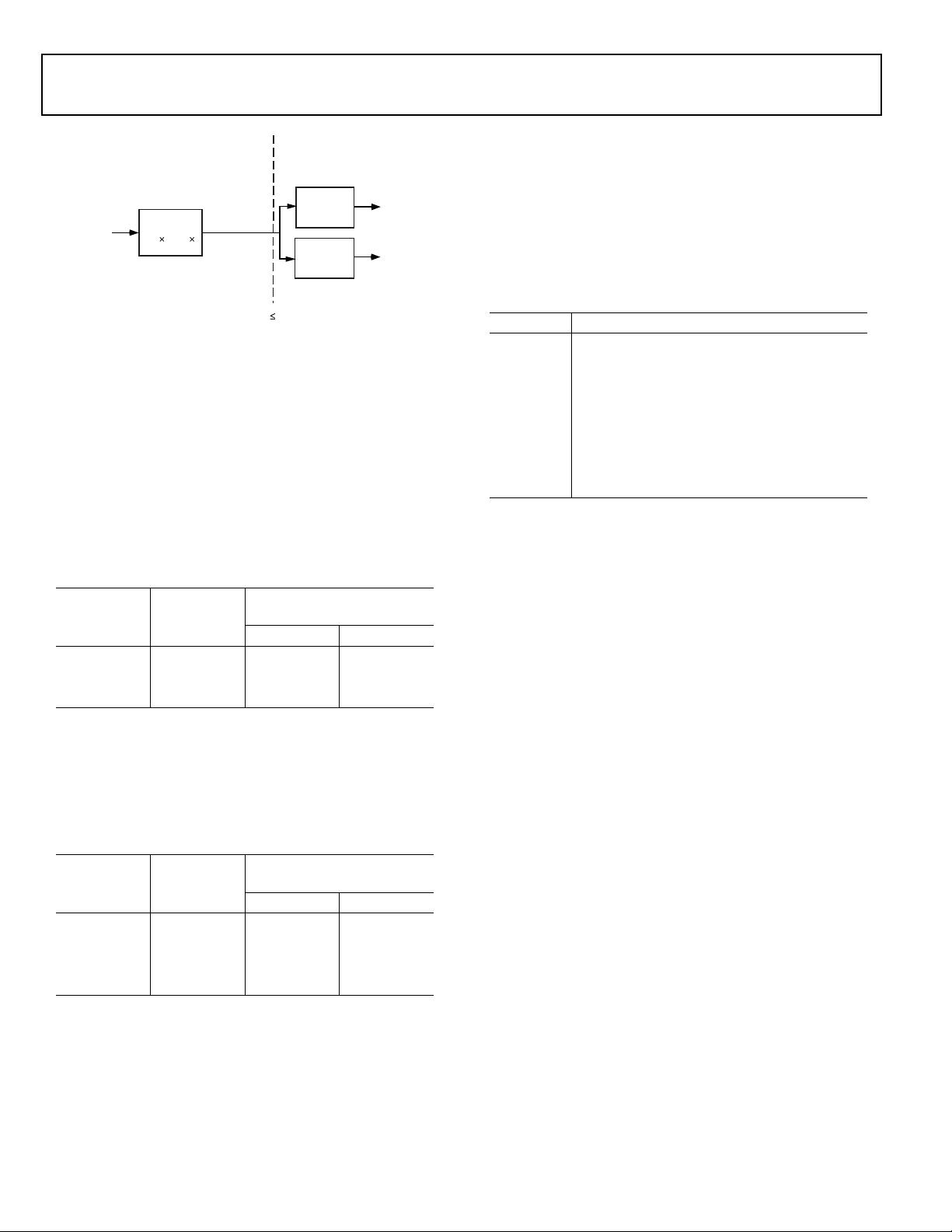

Because of the rich set of peripherals, the processor groups the

many peripheral signals to three ports—Port F, Port G, and

Port H. Most of the associated pins are shared by multiple sig-

nals. The ports function as multiplexer controls.

General-Purpose I/O (GPIO)

The processor has 35 bidirectional, general-purpose I/O (GPIO)

pins allocated across three separate GPIO modules—PORTFIO,

PORTGIO, and PORTHIO, associated with Port F, Port G, and

Port H, respectively. Each GPIO-capable pin shares functional-

ity with other processor peripherals via a multiplexing scheme;

however, the GPIO functionality is the default state of the device

upon power-up. Neither GPIO output nor input drivers are

active by default. Each general-purpose port pin can be individ-

ually controlled by manipulation of the port control, status, and

interrupt registers:

• GPIO direction control register – Specifies the direction of

each individual GPIO pin as input or output.

• GPIO control and status registers – The processor employs

a “write one to modify” mechanism that allows any combi-

nation of individual GPIO pins to be modified in a single

instruction, without affecting the level of any other GPIO

pins. Four control registers are provided. One register is

written in order to set pin values, one register is written in

order to clear pin values, one register is written in order to

toggle pin values, and one register is written in order to

specify a pin value. Reading the GPIO status register allows

software to interrogate the sense of the pins.

• GPIO interrupt mask registers – The two GPIO interrupt

mask registers allow each individual GPIO pin to function

as an interrupt to the processor. Similar to the two GPIO

control registers that are used to set and clear individual

pin values, one GPIO interrupt mask register sets bits to

enable interrupt function, and the other GPIO interrupt

mask register clears bits to disable interrupt function.

GPIO pins defined as inputs can be configured to generate

hardware interrupts, while output pins can be triggered by

software interrupts.

• GPIO interrupt sensitivity registers – The two GPIO inter-

rupt sensitivity registers specify whether individual pins are

level- or edge-sensitive and specify—if edge-sensitive—

whether just the rising edge or both the rising and falling

edges of the signal are significant. One register selects the

type of sensitivity, and one register selects which edges are

significant for edge-sensitivity.

DYNAMIC POWER MANAGEMENT

The processor provides five operating modes, each with a differ-

ent performance/power profile. In addition, dynamic power

management provides the control functions to dynamically alter

the processor core supply voltage, further reducing power dissi-

pation. When configured for a 0 volt core supply voltage, the

processor enters the hibernate state. Control of clocking to each

of the processor peripherals also reduces power consumption.

See Table 4 for a summary of the power settings for each mode.

Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed,

providing capability for maximum operational frequency. This

is the power-up default execution state in which maximum per-

formance can be achieved. The processor core and all enabled

peripherals run at full speed.

Active Operating Mode—Moderate Dynamic Power

Savings

In the active mode, the PLL is enabled but bypassed. Because the

PLL is bypassed, the processor’s core clock (CCLK) and system

clock (SCLK) run at the input clock (CLKIN) frequency. DMA

access is available to appropriately configured L1 memories.