华为FPGA开发指南:STA与工具详解

本资源是一份关于华为FPGA开发的相关资料,针对对FPGA技术感兴趣的读者,特别是对于在华为从事或者希望了解FPGA设计的专业人士。资料涉及BTS(Base Transceiver Station)硬件平台的特定版本(Version1.0),强调了静态时序分析(Static Timing Analysis, STA)的重要性,这是FPGA设计中的关键步骤,确保电路的性能和可靠性。

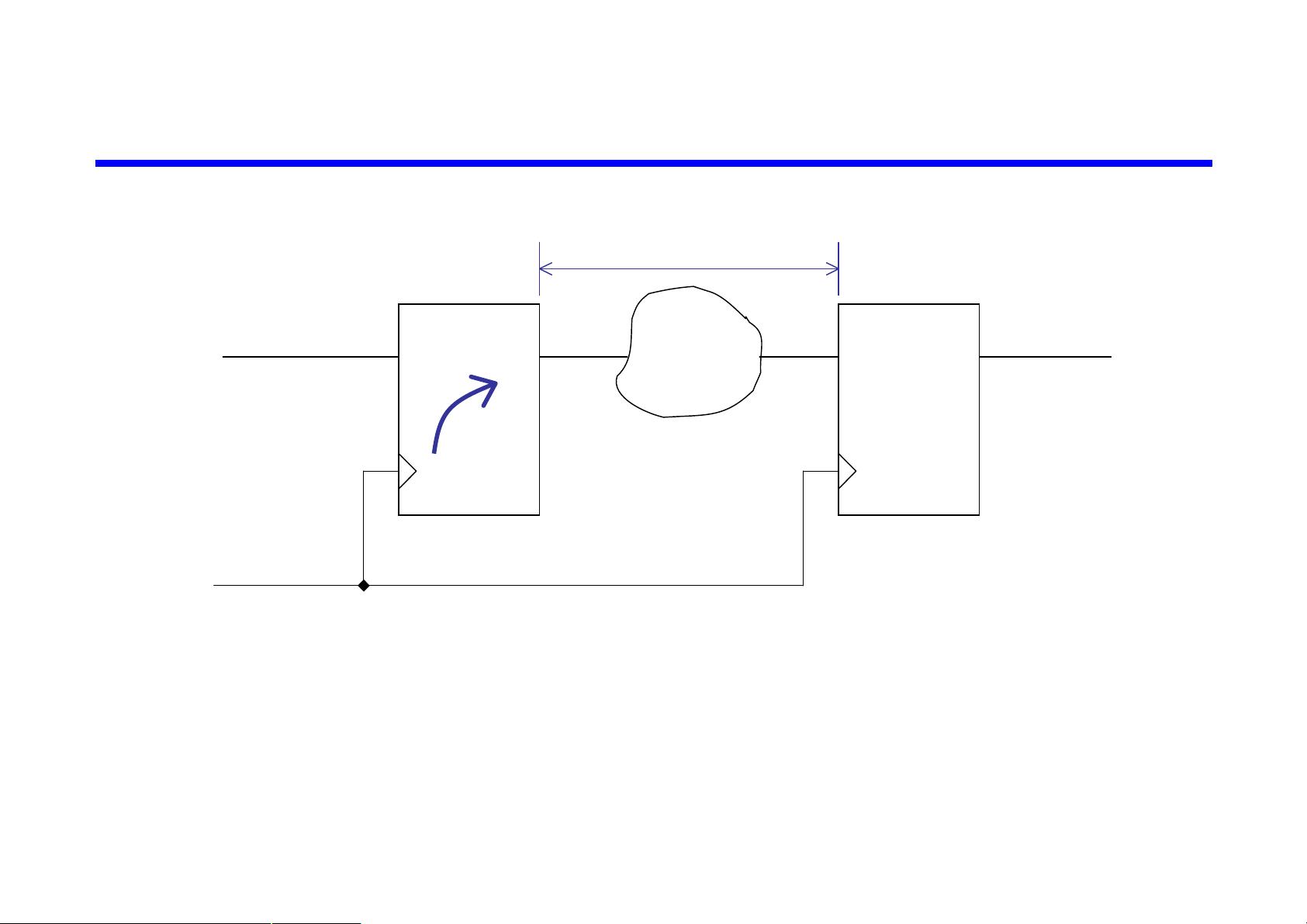

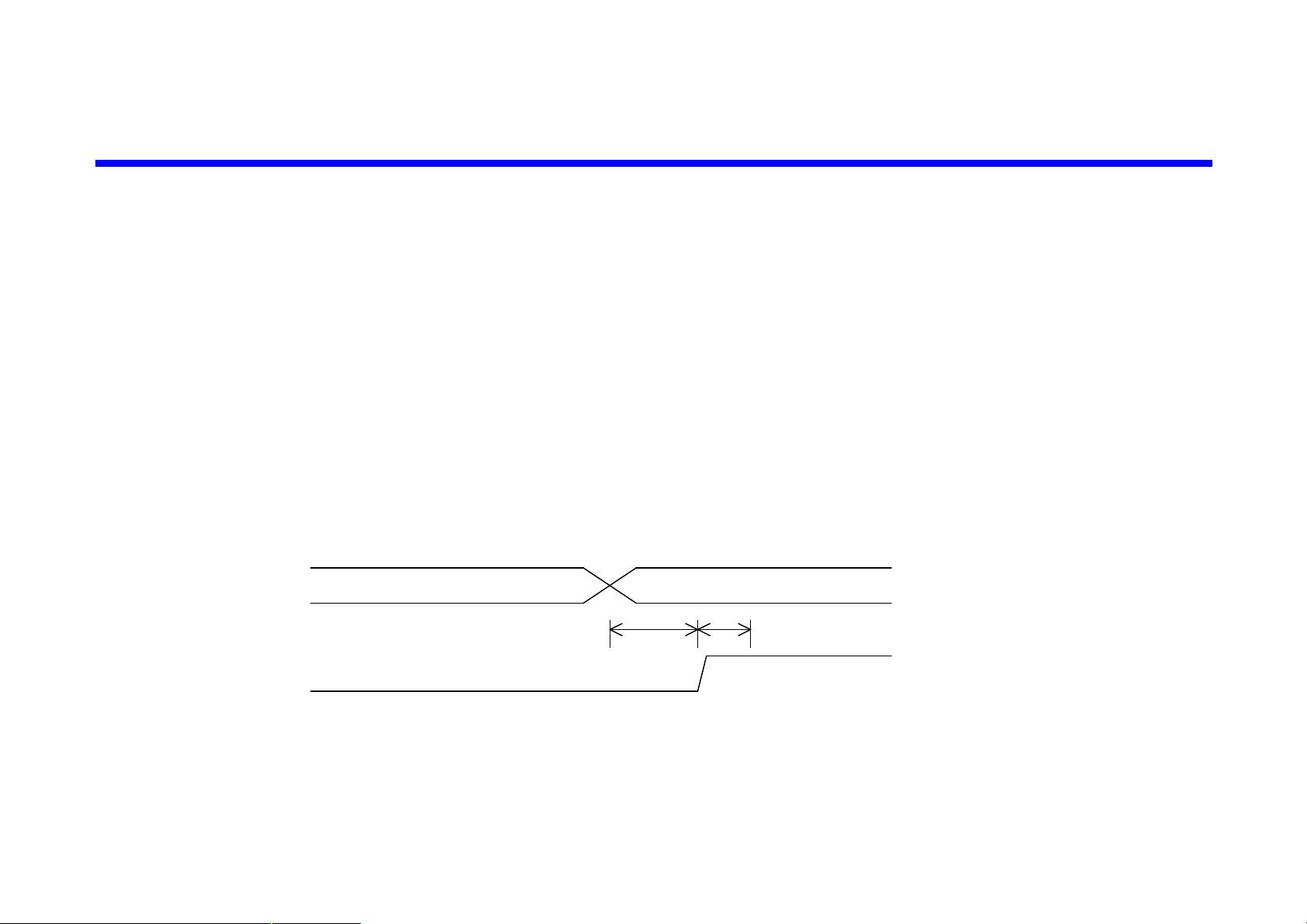

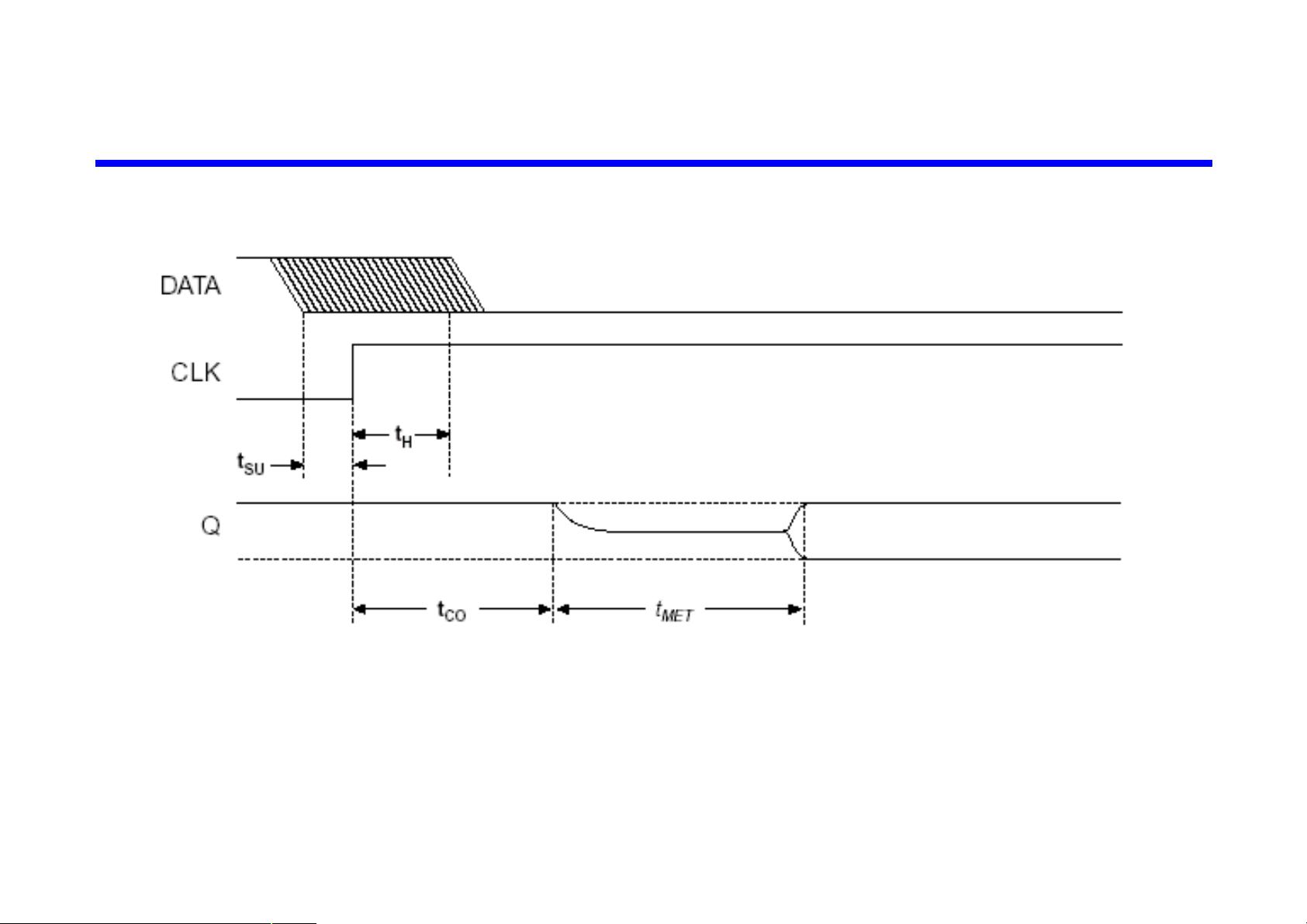

在提供的部分内容中,首先介绍了BTS的一些组成部分和结构,如不同的标识符(如BTS、-StaticTimingAnalysis等)以及版本控制信息。此外,还提到了多种工具和技术的使用,比如Synopsys PrimeTime、Mentor Graphics SST Velocity、Innoveda Blast和ãFPGAäå89等,这些都是在FPGA设计流程中常用的工具,用于进行设计验证、优化和实现。

FPGA开发中涉及到的具体概念包括时序分析,这是一种静态方法,通过对电路的逻辑行为进行模拟来预测信号延迟,确保满足预定的设计目标,如速度、功耗和性能要求。此外,资料中还提到了ASIC(Application-Specific Integrated Circuit)和ASIC设计,尽管这部分与FPGA开发并不同,但它展示了华为在集成电路设计领域的全面视角。

这份资料不仅包含理论知识,还可能包含了实践指导和案例研究,有助于华为的工程师们提升FPGA开发技能,应对日益增长的复杂度和挑战。这是一份深入且实用的资源,涵盖了华为FPGA开发的方方面面,是FPGA专业人士不可多得的学习资料。

点击了解资源详情

2009-04-08 上传

2024-04-24 上传

2011-06-15 上传

2015-08-05 上传

2009-09-16 上传

北络

- 粉丝: 238

- 资源: 30

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践