FT602Q USB3.0 UVC Bridge IC 数据手册

需积分: 10 65 浏览量

更新于2024-07-17

收藏 800KB PDF 举报

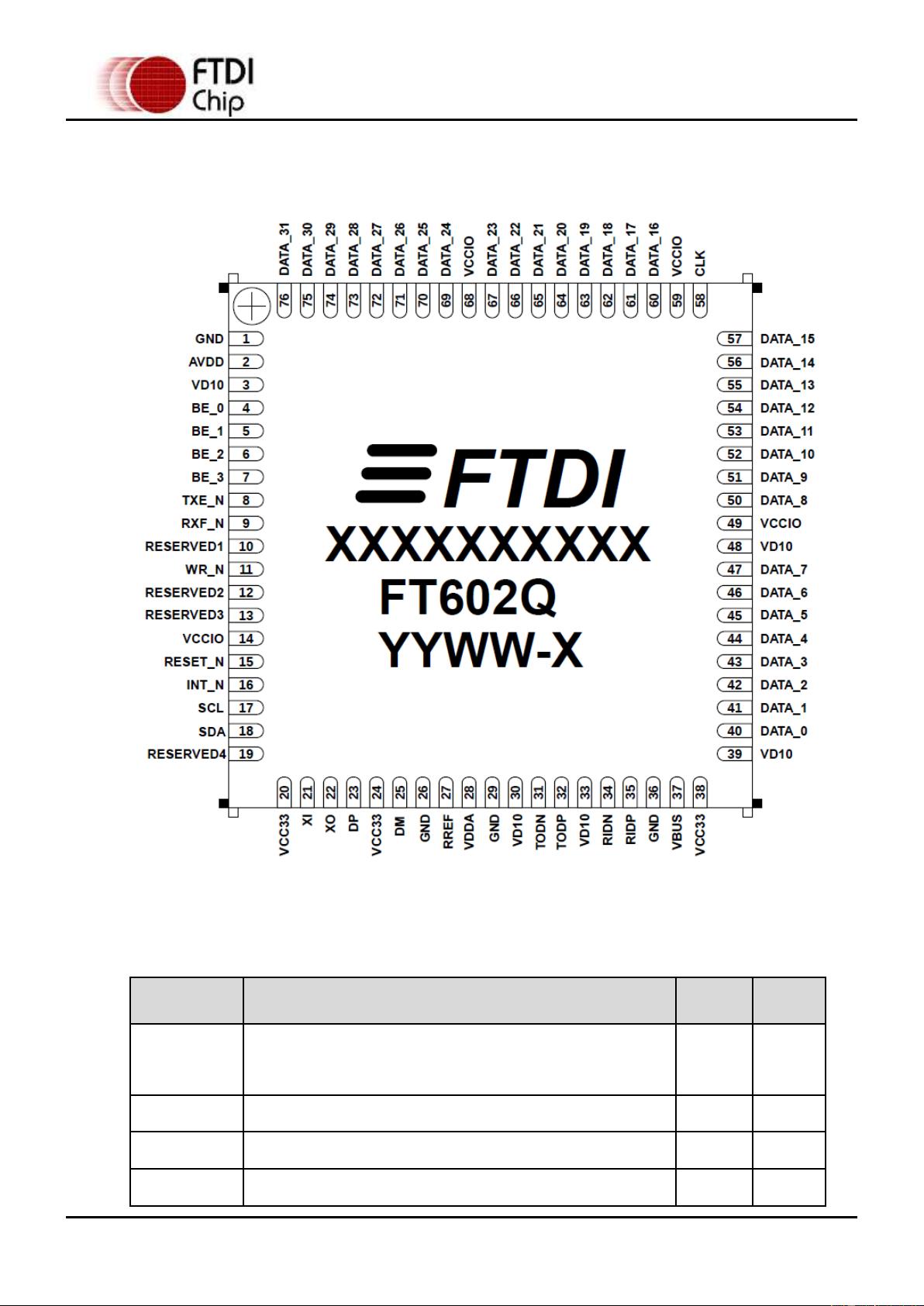

"FT602Q IC Datasheet提供了关于FT602Q这款USB3.0 UVC桥接芯片的详细规格和技术特性。该芯片由Future Technology Devices International Limited制造,适用于USB到FIFO接口的高速数据传输,支持USB3.1 Gen1 (5Gbps)和USB2.0 High Speed (480Mbps)速率,以及控制、批量和中断三种USB传输类型。"

FT602Q是专为USB Video Class (UVC) 1.1版本设计的,能够处理多达4个视频输入通道,可在FIFO总线上工作。它支持两种并行从机FIFO总线协议:245 FIFO模式和多通道FIFO模式,最大数据传输速率可达400MB/s,采用32位并行接口。此外,芯片内置16KB的数据缓冲RAM,确保了高效的数据处理能力。

该芯片还集成了I2C主接口,允许配置视频设备,支持多种电压I/O,包括1.8V、2.5V和3.3V,适应性强。内部有一个1.0V的低压差稳压器,以稳定供电。FT602Q还包括一个集成的上电复位电路,保证系统在启动时的稳定性。

用户可编程的USB和UVC描述符使得该芯片可以根据具体应用进行定制,扩展性极强。其工业级的工作温度范围从-40℃到85℃,确保了在各种环境条件下的可靠性。封装形式为无铅QFN-76,符合RoHS标准,是一款紧凑型解决方案,适用于需要高带宽、低延迟视频传输的应用场景,如高清摄像头、视频会议设备和多媒体记录设备等。

2012-03-13 上传

2019-08-24 上传

2020-02-21 上传

2022-09-23 上传

2019-08-20 上传

2019-08-14 上传

2022-07-14 上传

auiyn

- 粉丝: 3

- 资源: 106

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建