十四进制同步减法计数器设计与数字电子实验详解

版权申诉

67 浏览量

更新于2024-06-23

收藏 942KB PDF 举报

本篇文章主要介绍了在数字电子设计中应用十四进制同步减法计数器的设计过程。设计目标包括深化对教材的理解,实践理论知识,并检验个人的数字电子技术能力。设计流程分为以下几个步骤:

1. **课程设计目的**:设计任务旨在通过实际操作,验证理论知识的正确性和提高设计技能。学生需要设计一个具有实用性的十四进制同步减法计数器,同时关注触发器的选择、时钟方程的建立和卡诺图的应用。

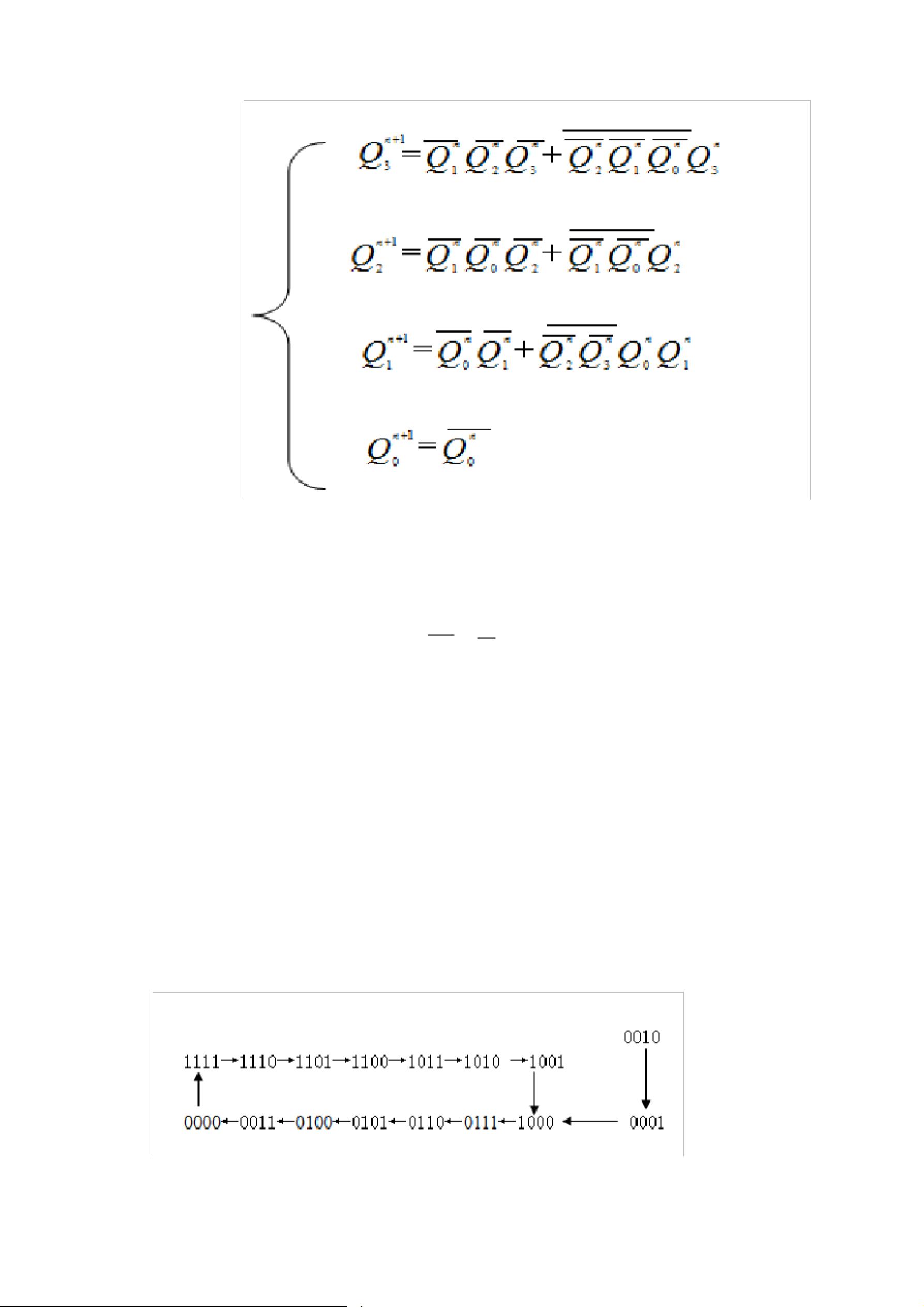

2. **设计框架**:设计过程包括绘制同步二进制加法计数器示意框图作为基础,然后构建十四进制同步减法计数器的状态图。状态图显示了从1111到0000的计数序列,以及无效态0001和0010。

3. **触发器与时钟方程**:选择JK边沿触发器作为基本单元,因为它们适合同步计数器。所有触发器的时钟输入CP相同,即CP0=CP1=CP2=CP3。接下来,通过卡诺图来确定各个状态的逻辑关系。

4. **状态方程与输出方程**:利用卡诺图分析得出状态方程,描述了各触发器的状态变化。输出方程则基于触发器特性方程,表示输出信号的逻辑关系。

5. **驱动方程**:根据JK触发器的特性,推导出驱动方程,即控制输入J和K如何影响触发器的输出。

6. **自启动检查**:通过将无效态代入状态方程和输出方程,确认计数器能够自启动,即从无效态进入有效态。

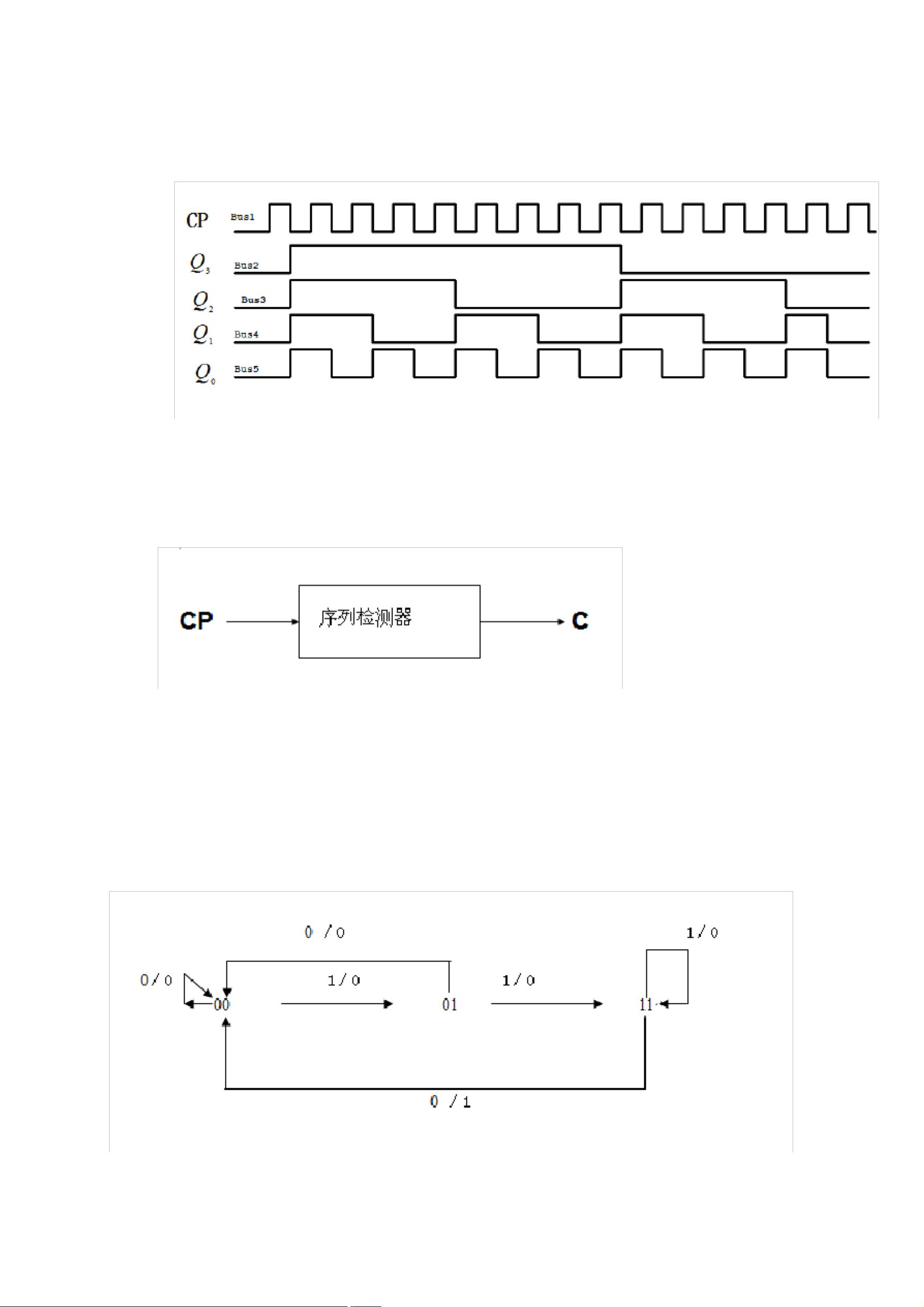

7. **序列检测器设计**:文章还涉及序列检测器的设计,针对特定序列1110,设计了状态图和相应的卡诺图,以及状态方程和输出方程的推导。

8. **加法器设计**:文章提及的序列检测器设计中,还涉及到三位二进制加法器的设计,包括次态和输出的卡诺图,以及状态方程和输出方程的编写。

通过以上步骤,学生不仅掌握了同步计数器的设计方法,还锻炼了解决实际问题的能力,如选择合适的触发器、理解和应用卡诺图等技术。整个设计过程深入浅出,展示了数字电子设计的核心原理和技术实践。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-10-17 上传

2022-07-07 上传

2022-06-16 上传

2022-11-01 上传

2022-06-20 上传

2023-08-16 上传

hhappy0123456789

- 粉丝: 74

- 资源: 5万+

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查