6 Volume I: RISC-V User-Level ISA V2.0

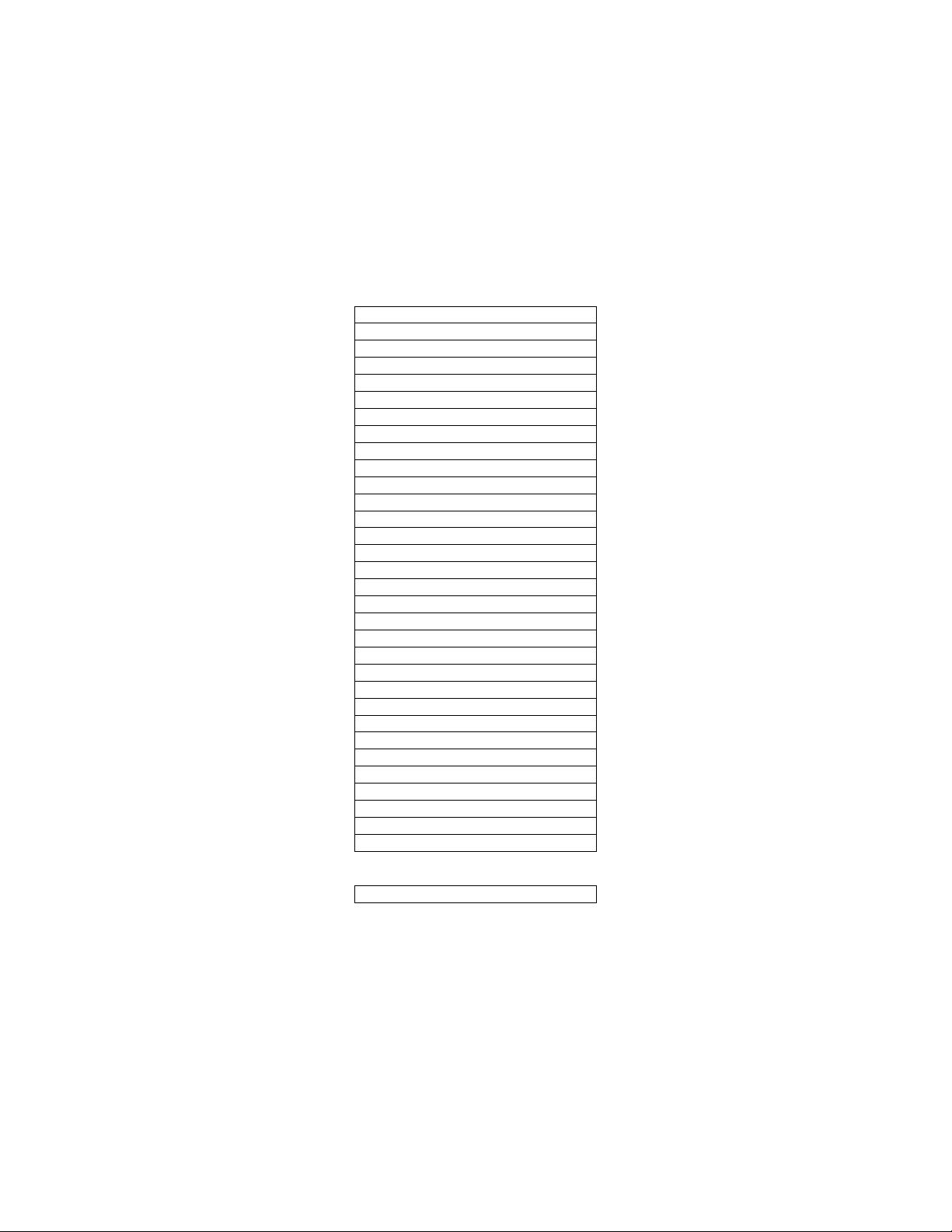

extension can map 3 additional 30-bit instruction spaces into the 32-bit fixed-width format, while

preserving support for standard >=32-bit instruction-set extensions. Further, if the implemen-

tation also does not need instructions >32-bits in length, it can recover a further four major

opcodes.

We consider it a feature that any length of instruction containing all zero bits is not legal, as

this quickly traps erroneous jumps into zeroed memory regions.

The base RISC-V ISA has a little-endian memory system, but non-standard variants can provide

a big-endian or bi-endian memory system. Instructions are stored in memory with each 16-bit

parcel stored in a memory halfword according to the implementation’s natural endianness. Parcels

comprising one instruction are stored at increasing halfword addresses, with the lowest addressed

parcel holding the lowest numbered bits in the instruction specification, i.e., instructions are always

stored in a little-endian sequence of parcels regardless of the memory system endianness. The code

sequence in Figure 1.2 will store a 32-bit instruction to memory correctly regardless of memory

system endianness.

We chose little-endian byte ordering for the RISC-V memory system because little-endian sys-

tems are currently dominant commercially (all x86 systems; iOS, Android, and Windows for

ARM). A minor point is that we have also found little-endian memory systems to be more nat-

ural for hardware designers. However, certain application areas, such as IP networking, operate

on big-endian data structures, and so we leave open the possibility of non-standard big-endian

or bi-endian systems.

We have to fix the order in which instruction parcels are stored in memory, independent

of memory system endianness, to ensure that the length-encoding bits always appear first in

halfword address order. This allows the length of a variable-length instruction to be quickly

determined by an instruction fetch unit by examining only the first few bits of the first 16-bit

instruction parcel. Once we had decided to fix on a little-endian memory system and instruction

parcel ordering, this naturally led to placing the length-encoding bits in the LSB positions of the

instruction format to avoid breaking up opcode fields.

1.3 Exceptions, Traps, and Interrupts

We use the term exception to refer to an unusual condition occurring at run time. We use the term

trap to refer to the synchronous transfer of control to a supervisor environment when caused by

an exceptional condition occurring within a RISC-V thread. We use the term interrupt to refer to

the asynchronous transfer of control to a supervisor environment caused by an event outside of the

current RISC-V thread.

The instruction descriptions in following chapters describe conditions that raise an exception dur-

ing execution. Whether and how these are converted into traps is dependent on the execution

environment, though the expectation is that most environments will take a precise trap when an

exception is signaled (except for floating-point exceptions, which, in the standard floating-point

extensions, do not cause traps).

Our use of “exception” and “trap” matches that in the IEEE-754 floating-point standard.