Altera Quartus®II 中的 LogicLock 技术在 FPGA 设计中的应用

需积分: 18 163 浏览量

更新于2024-09-13

收藏 127KB DOC 举报

“本文介绍了逻辑锁定(LogicLock)在FPGA设计中的应用,特别是在解决时序分析问题上的方法。文中以Altera的Quartus®II软件为例,展示了如何利用这一功能优化逻辑布局,以应对高速时钟和资源占用过多导致的设计问题。”

在 FPGA 设计中,逻辑锁定(LogicLock)是一种独特的优化技术,由Altera公司的Quartus®II设计软件提供。Altera作为可编程系统级芯片(SOPC)领域的先驱,其FPGA器件因其灵活性、性价比和易用性而广泛应用于各种场景。Quartus®II作为Altera专为FPGA、CPLD和结构化ASIC设计的电子设计自动化(EDA)工具,具备多项优势,包括领先的性能、设计流程支持、系统设计与IP集成、布局布线以及验证方案等。

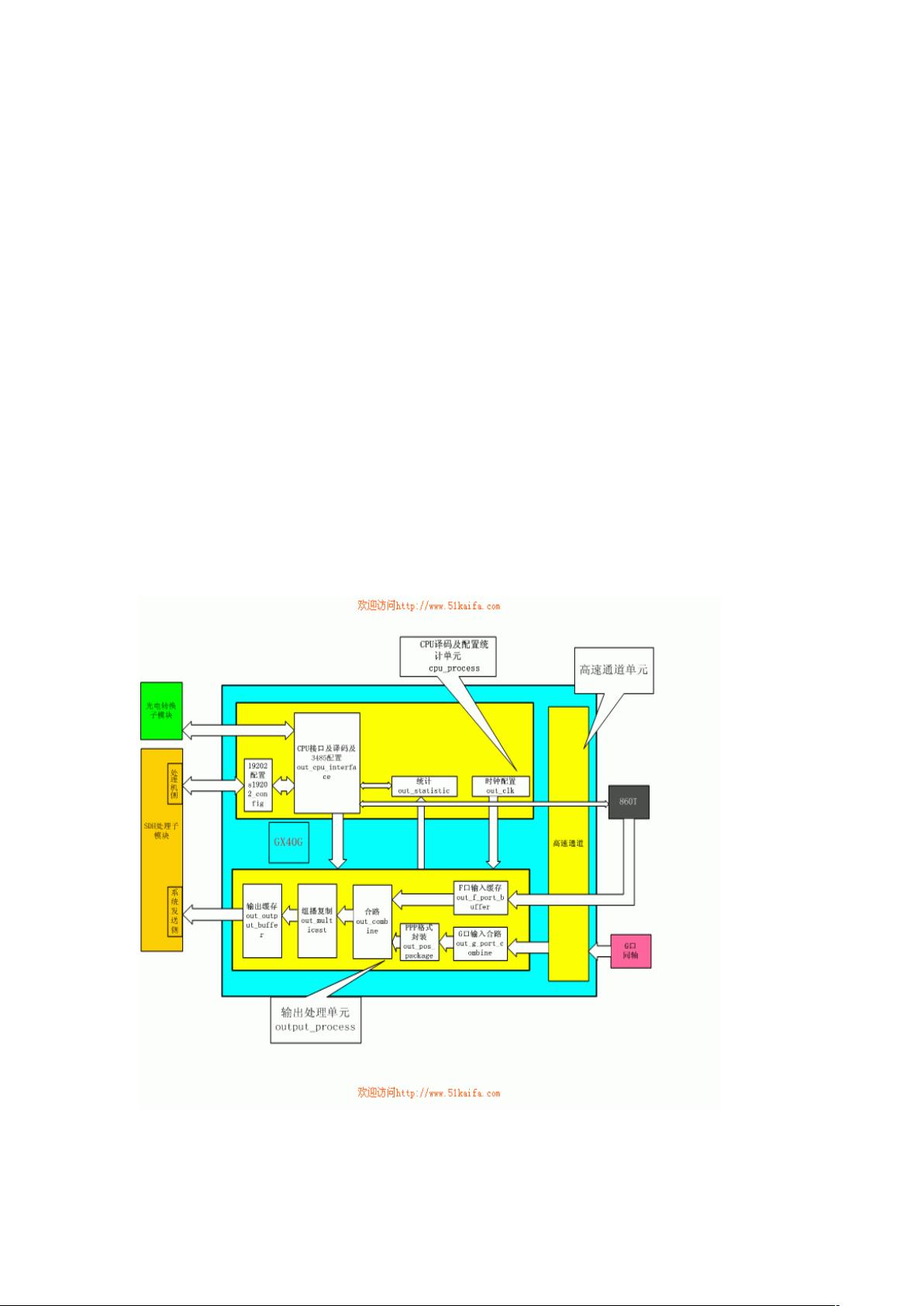

在实际工程中,逻辑锁定常常用于解决时序分析问题。文章以“T比特路由器项目”的4X2.5G线路接口卡为例,其中使用了Altera的Stratix™GX系列EP1SGX40G FPGA和AMCC公司的S19202芯片。由于S19202的200MHz高速时钟和数据分片接收,使得FPGA的输出缓存模块占用过多资源,导致时序分析无法通过。Quartus®II在分析综合后的布局布线过程中,可能会出现资源分布不均的问题,进而形成致命路径,无法满足设计的时序要求。

为了解决这个问题,文章提出了利用LogicLock技术。LogicLock允许设计者锁定特定的逻辑块或连接,防止它们在布局布线阶段被移动,从而可以强制某些逻辑保持在原地,优化资源分配,确保关键路径的时序得以满足。通过这种方式,设计者可以手动干预布局,确保高速路径得到适当的资源支持,以达到更高的工作频率。

在应用LogicLock时,首先需要识别出设计中的关键路径和导致时序问题的模块,然后在Quartus®II中选择要锁定的逻辑元素。锁定操作完成后,重新进行布局布线,通常可以改善时序分析的结果。文中提到的案例中,通过应用LogicLock,设计者能够解决因资源紧张导致的时序失败问题,提高设计的时钟速度和稳定性。

逻辑锁定是FPGA设计中解决时序问题的一个重要策略,特别是在面对高速时钟和复杂逻辑布局时。通过理解并有效运用这一技术,设计师可以更好地优化资源利用,提高设计的性能和可靠性。

144 浏览量

172 浏览量

494 浏览量

705 浏览量

158 浏览量

2022-08-03 上传

点击了解资源详情

linda_wang1999

- 粉丝: 0

最新资源

- Lindo软件入门与线性规划实例详解

- 数学建模比赛指导:聚类与判别分析在SPSS中的应用

- 数学建模:相关分析与SPSS应用

- Rails4Days中文版:四天学会Rails开发

- 淮海工学院图书管理系统开发与关键技术研究

- 构建J2EE应用程序指南

- 超市管理信息系统:设计与实现

- 数据结构讲义:信息处理与抽象数据类型

- Ubuntu安装全攻略:图解步骤详解

- Oracle入门指南:从8i到9i

- ACM竞赛入门指南:语言、数学、数据结构与实践提升

- Java实现HTTP 1.0简单Web服务器

- J2EE与Spring框架实战:从理论到核心组件

- J2EE学习笔记:ValueObject与JSP基础

- REST架构风格与中文翻译:网络软件设计基石

- C++泛型编程深度探索:Templates完全指南