FPGA实现SERDES协议详解与挑战

需积分: 50 19 浏览量

更新于2024-08-06

收藏 1007KB PDF 举报

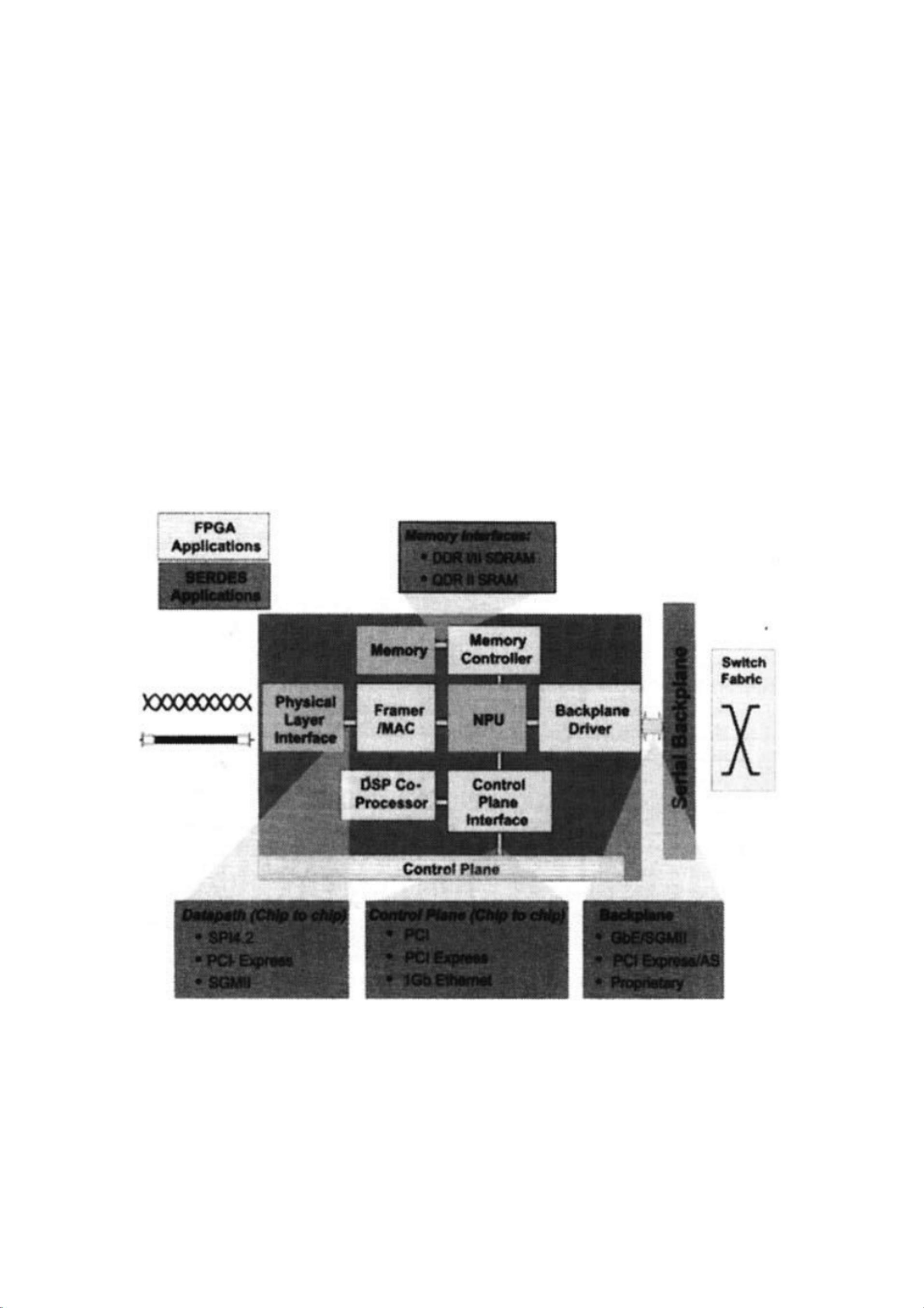

"本文主要探讨了如何在FPGA中实现SERDES协议,强调了SERDES在高数据速率和低引脚数需求中的重要性。通过使用高速差分对,SERDES能够有效地提升数据传输效率,例如,单个PCI-Express通道可以替代传统的PCI总线,实现更高的数据速率。在FPGA中,SERDES可以应用于各种接口,如数据通路、背板接口、存储器接口等。文章特别关注了时钟数据恢复(CDR)接口,因为它在高速运行和长距离传输中面临更大的设计挑战。CDR接收机通过恢复嵌入在数据中的时钟信号来工作,首先进行8b/10b编码以减少干扰,然后通过锁相技术在接收端校准数据,最终解码为系统可用的8位数据。"

在FPGA实现SERDES协议的过程中,关键在于理解并掌握SERDES的工作原理和其在系统中的作用。SERDES协议的核心是将并行数据转换为串行数据,通过高速差分对进行传输,以减少引脚数量,提高数据传输速率。这种转变对于应对不断增长的芯片功能和数据吞吐量需求至关重要。

在FPGA中,SERDES可以被用于各种不同的应用场景,如芯片到芯片的通信、SPI4.2、PCI-Express、SGMII等数据通路,以及GbE/GSMII、PCIExpress/AS、专用背板接口,还包括DDR1/II SDRAM和QDR II SRAM等存储器接口。这些应用通常需要定制化的接口控制器,如存储器控制器、帧调节器/MAC、DSP协处理器和控制板接口等。

源同步(SS)接口和时钟数据恢复(CDR)接口是SERDES的两种主要类型。源同步接口依赖于与数据一起传输的独立时钟信号,而CDR接口则通过检测数据流中的开关转换来恢复时钟。由于CDR接口在高速和长距离传输中更为复杂,因此在实际设计中,尤其是在FPGA实现中,CDR技术的研究和优化是关键。

时钟数据恢复(CDR)接收机是实现高效串行通信的关键组件。它的工作流程包括接收串行位流并锁定其时钟,然后校准数据,再在接收器的参考时钟下对齐数据,最后进行8b/10b解码。8b/10b编码是一种常用的前向错误校正技术,它通过确保“0”和“1”的均衡分布来减小干扰,并提供足够的数据边缘以确保接收机能够正确锁定时钟。

理解并熟练运用FPGA中的SERDES协议和CDR技术是现代高速数字系统设计中的重要技能,这对于实现高性能、低功耗和紧凑的电子设备具有重要意义。在设计过程中,需要考虑信号完整性、噪声抑制、电源管理等多个方面,以确保数据的准确传输和系统的稳定运行。

2023-05-23 上传

2014-04-12 上传

点击了解资源详情

2023-05-13 上传

2023-11-25 上传

2020-10-11 上传

2020-08-24 上传

271 浏览量

weixin_38548231

- 粉丝: 7

- 资源: 892

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器