同步与异步电路解析:建立时间与保持时间的关键

需积分: 17 63 浏览量

更新于2024-07-25

收藏 352KB DOC 举报

"线与"逻辑是两个输出信号相连可以实现与的功能,即只有当所有参与"线与"的输出都为低电平时,最终的逻辑输出才是低电平。在硬件实现上,通常采用集电极开路(OC门)或三态门(TTL电路中的T型门或CMOS电路中的三态门)来实现。OC门的特点是其输出端可以并联在一起,通过外部的上拉电阻提供高电平。如果多个OC门的输出并联且都为低电平时,整个线路呈现低电平,实现了“线与”功能。但是,如果不使用OC门直接连接,可能会导致大量的电流(灌电流)流过,超出逻辑门的承受能力,从而损坏电路。因此,为了安全起见,必须在输出端口添加一个上拉电阻,确保在不需要“线与”时,输出能被拉高至高电平。

5.什么是Setup和Holdup时间?它们有什么区别?

答:建立时间(Tsu:setup time)和保持时间(Th:hold time)是数字集成电路设计中的关键概念,主要涉及数字系统中时钟同步的问题。建立时间是指在时钟边沿到来前,数据信号必须稳定在一个确定的阈值范围内的最短时间。如果数据在时钟边沿到来前未达到稳定状态,那么触发器无法正确捕获数据,导致数据错误。

保持时间则是在时钟边沿之后,数据必须保持稳定的时间长度。如果数据在时钟边沿之后发生了变化,同样会导致触发器无法正确读取数据,产生错误。简而言之,建立时间关注的是数据在时钟上升沿到来之前必须稳定,而保持时间关注的是数据在时钟上升沿之后必须保持稳定。

6.同步电路和异步电路在实际应用中的优缺点是什么?

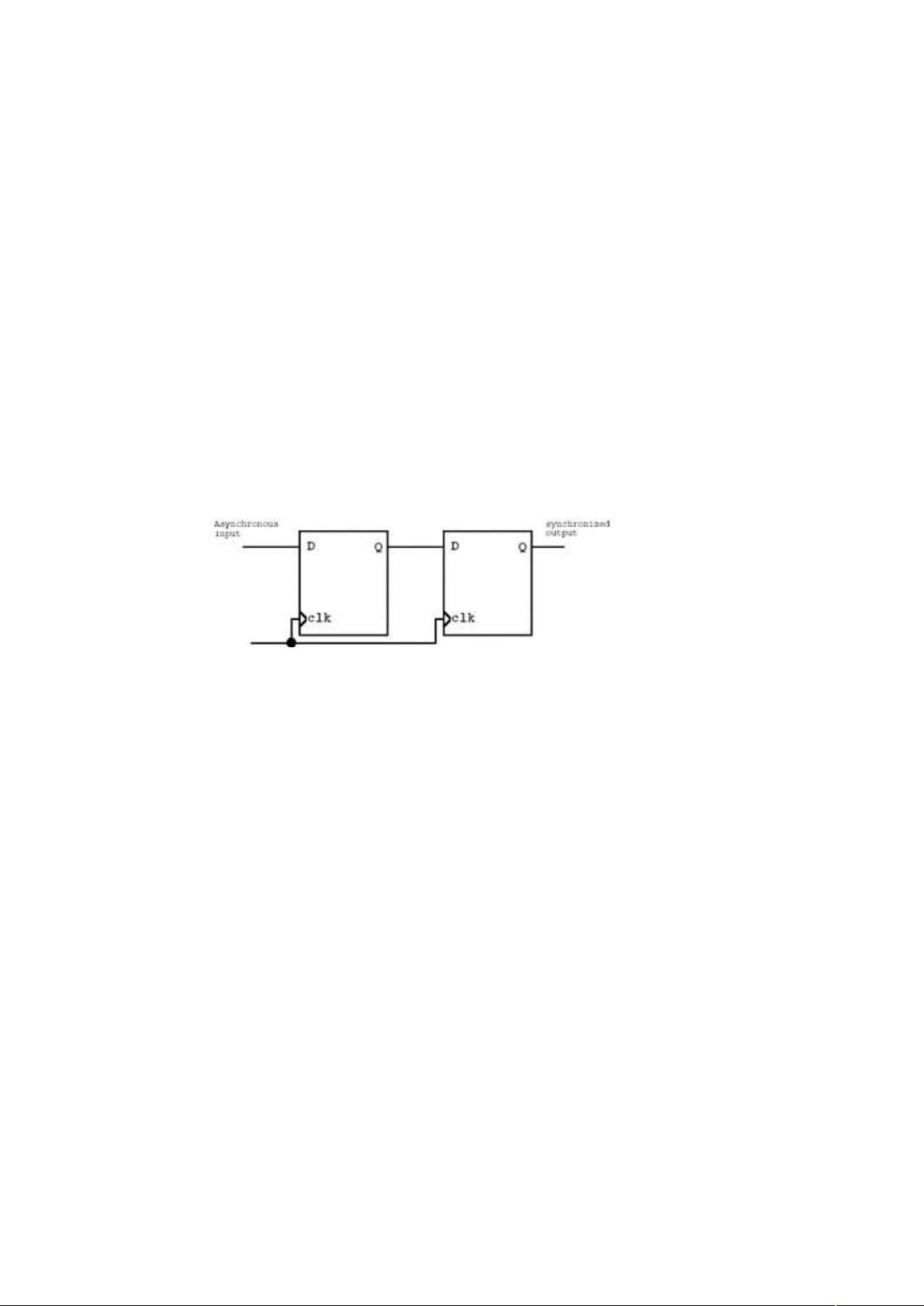

同步电路的优点在于其时序明确,所有操作都在统一的时钟控制下进行,使得设计和分析相对简单,系统工作更可靠。然而,同步电路需要一个全局时钟,这会引入延迟并增加功耗。此外,时钟同步还可能导致亚稳态问题,需要额外的设计考虑。

异步电路则具有更高的灵活性,因为它不受单一时钟的限制,可以在不同的速率下工作,适合处理非同步事件。但异步电路设计复杂,分析和验证难度大,容易出现竞争冒险,且功耗和面积通常比同步电路更大。

7.同步逻辑和异步逻辑在实际电路设计中如何选择?

同步逻辑通常用于对时序要求严格、系统稳定性至关重要的场合,如处理器、存储器和高速通信系统。异步逻辑则适用于低速、局部的控制逻辑或者对时序要求不那么严格的场景,例如接口电路和部分嵌入式系统的控制单元。

8.在数字系统设计中,如何确保满足Setup和Holdup时间要求?

确保满足Setup和Holdup时间的关键在于时序分析。设计者需要计算从数据源到触发器的数据路径延迟,并确保这个延迟加上数据的传输延迟小于建立时间。同样,从触发器到数据接收端的延迟加上保持时间应大于时钟周期。此外,使用适当的时钟分配网络、优化布线、选择适当的器件速度等级以及利用时钟树综合等技术,都可以帮助满足时序约束。

电子工程师在面试中需要对这些基本概念有深入的理解,以便于设计出高效、可靠的数字电路系统。这些知识点涵盖了数字电路设计的基础,对于解决实际工程问题至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-06-11 上传

2020-08-14 上传

2010-01-02 上传

柏斯特湾

- 粉丝: 0

- 资源: 1

最新资源

- WordPress作为新闻管理面板的实现指南

- NPC_Generator:使用Ruby打造的游戏角色生成器

- MATLAB实现变邻域搜索算法源码解析

- 探索C++并行编程:使用INTEL TBB的项目实践

- 玫枫跟打器:网页版五笔打字工具,提升macOS打字效率

- 萨尔塔·阿萨尔·希塔斯:SATINDER项目解析

- 掌握变邻域搜索算法:MATLAB代码实践

- saaraansh: 简化法律文档,打破语言障碍的智能应用

- 探索牛角交友盲盒系统:PHP开源交友平台的新选择

- 探索Nullfactory-SSRSExtensions: 强化SQL Server报告服务

- Lotide:一套JavaScript实用工具库的深度解析

- 利用Aurelia 2脚手架搭建新项目的快速指南

- 变邻域搜索算法Matlab实现教程

- 实战指南:构建高效ES+Redis+MySQL架构解决方案

- GitHub Pages入门模板快速启动指南

- NeonClock遗产版:包名更迭与应用更新