Verilog HDL深度解析:数字信号处理与硬件实现

需积分: 5 170 浏览量

更新于2024-07-30

收藏 1.73MB PDF 举报

"这是一份全面的Verilog HDL教程,涵盖了数字信号处理、计算、程序设计、算法和硬线逻辑的基础知识,适合于学习和理解集成电路设计中的Verilog语言应用。"

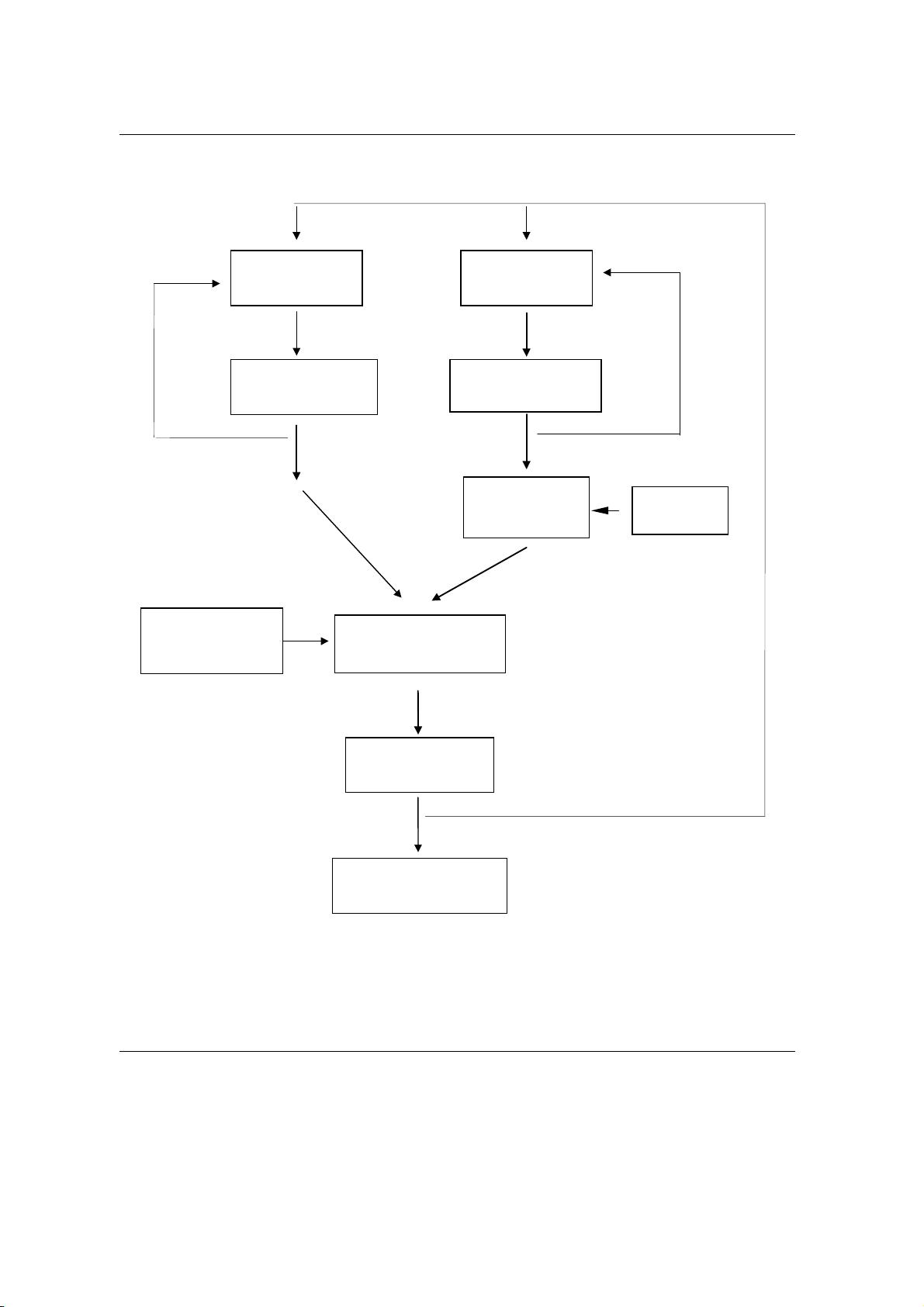

在数字信号处理(DSP)领域,Verilog HDL(硬件描述语言)是一种重要的工具,用于设计和实现高速、专用的硬件系统。本教程首先引入了数字信号处理的基本概念,包括滤波、变换、加密、解密、编码、解码、纠错和压缩等操作,这些都是现代计算机和通信系统中不可或缺的部分。这些操作本质上是数学运算,尽管可以使用软件编程语言(如C、Pascal或汇编)进行模拟,但对实时性和速度有严格要求的应用场景,硬件实现成为必要。

非实时的数字信号处理,例如石油地质调查中的数据分析,可以通过通用计算机逐步完成,因为处理时间不构成约束。然而,对于军用通信和雷达系统等需要快速响应的应用,通用计算机的性能往往不足以满足需求。在这种情况下,Verilog HDL就显得尤为重要,它允许设计者创建定制的硬件系统,直接在硬件层面执行复杂的运算,从而实现高速、低延迟的数据处理。

高速FPGA(现场可编程门阵列)和ASIC(专用集成电路)是实现硬线逻辑电路的常见平台。与通用微处理器不同,这些设备的设计目标是针对特定任务优化,可以避免微处理器的指令级处理和内存访问延迟。通过Verilog HDL,设计者能够精确地定义电路逻辑,确保在严格的时序限制下完成所需运算。

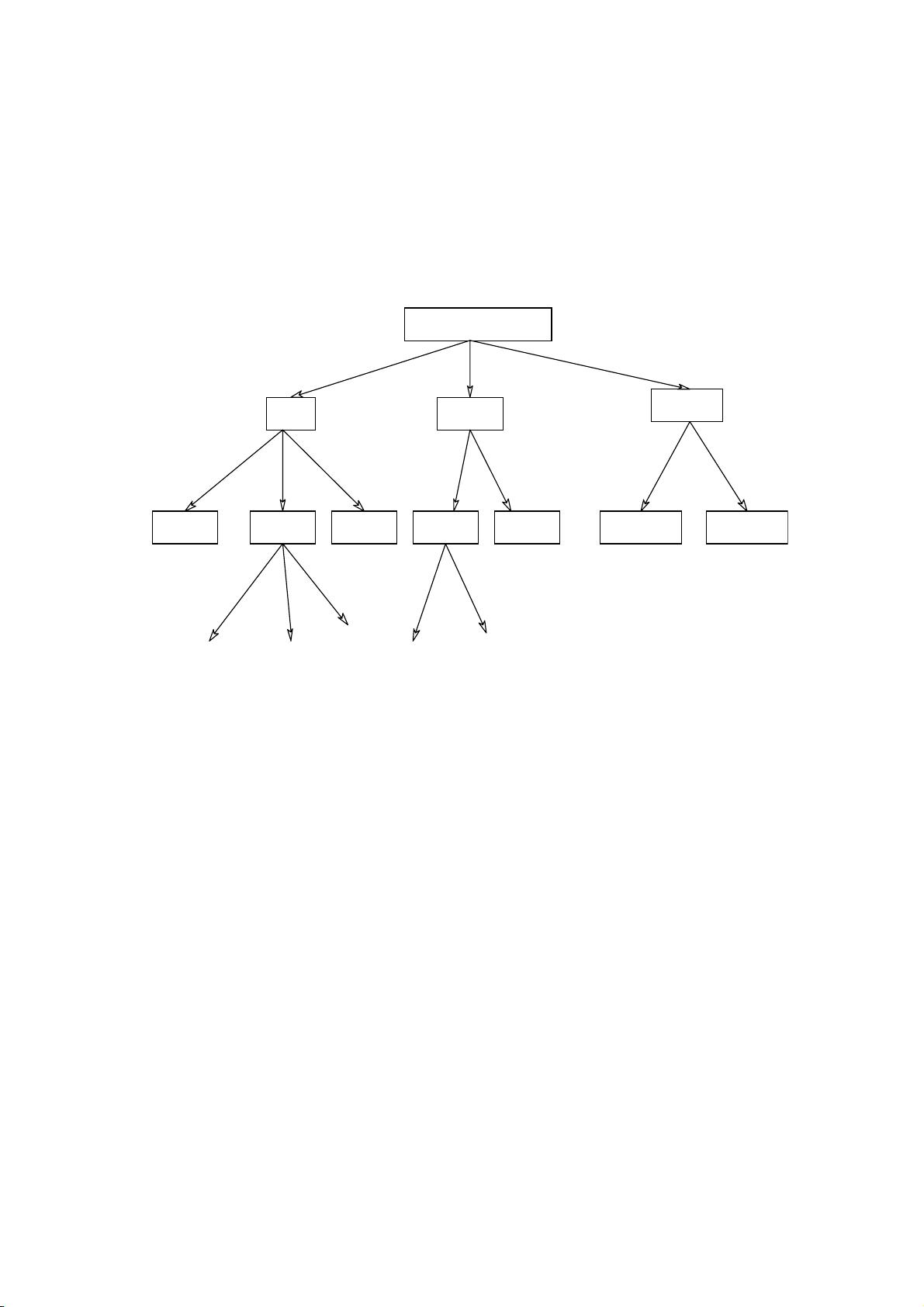

Verilog HDL不仅用于描述算法,还用于构建硬件结构,包括内部总线和运算部件,这些都可根据特定信号处理任务的需求进行定制。在教程中,读者将学习如何使用Verilog来定义数字系统,创建逻辑门、触发器、移位寄存器等基本元素,以及如何组合这些元素形成复杂的系统,如数字滤波器、加法器、乘法器等。

通过深入学习本教程,读者将掌握Verilog语言的基础和高级特性,包括模块化设计、接口定义、行为级建模和时序分析,从而具备设计和实现高效数字信号处理硬件系统的能力。这不仅对电子工程师有益,也对那些希望了解硬件层面计算原理的软件开发者和算法设计者具有很高的价值。

168 浏览量

197 浏览量

1106 浏览量

273 浏览量

2013-05-29 上传

2009-08-28 上传

2022-09-14 上传

点击了解资源详情

2022-09-14 上传

husanlim

- 粉丝: 42

- 资源: 11

最新资源

- 靛蓝1

- 简洁大气喜庆新年风春节主题ppt模板

- mysql安装配置详细教程.zip

- CATS Movie HD Wallpapers Theme-crx插件

- 屏蔽鼠标右键特效代码

- PHP实例开发源码-易运维(一站式运维管理系统) v2.0.zip

- 创建任意多个文件和文件夹的python脚本,用于测试create.zip

- AI_CS6_SDK_Win_682.6 版本

- 2020_1_CDM_AppHerois:不能重复使用SQLite的布局,不希望使用任何其他东西

- Needs More Glitter-crx插件

- Yahtzee-JS:Yahtzee(始于2002年)-HTML,JavaScript和CSS

- 最新vscode安装教程.zip

- jq鼠标滚动视差效果特效代码

- github-users-finder:一个简单的GitHub users finder应用程序

- 2015 0ctf exploit freenote 400.rar

- Windows下与USB通信、HID通信源码