OUT

OUT

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87

6 5 4

3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

EVT

PROTO 2

PROTO 1

PROTO 0

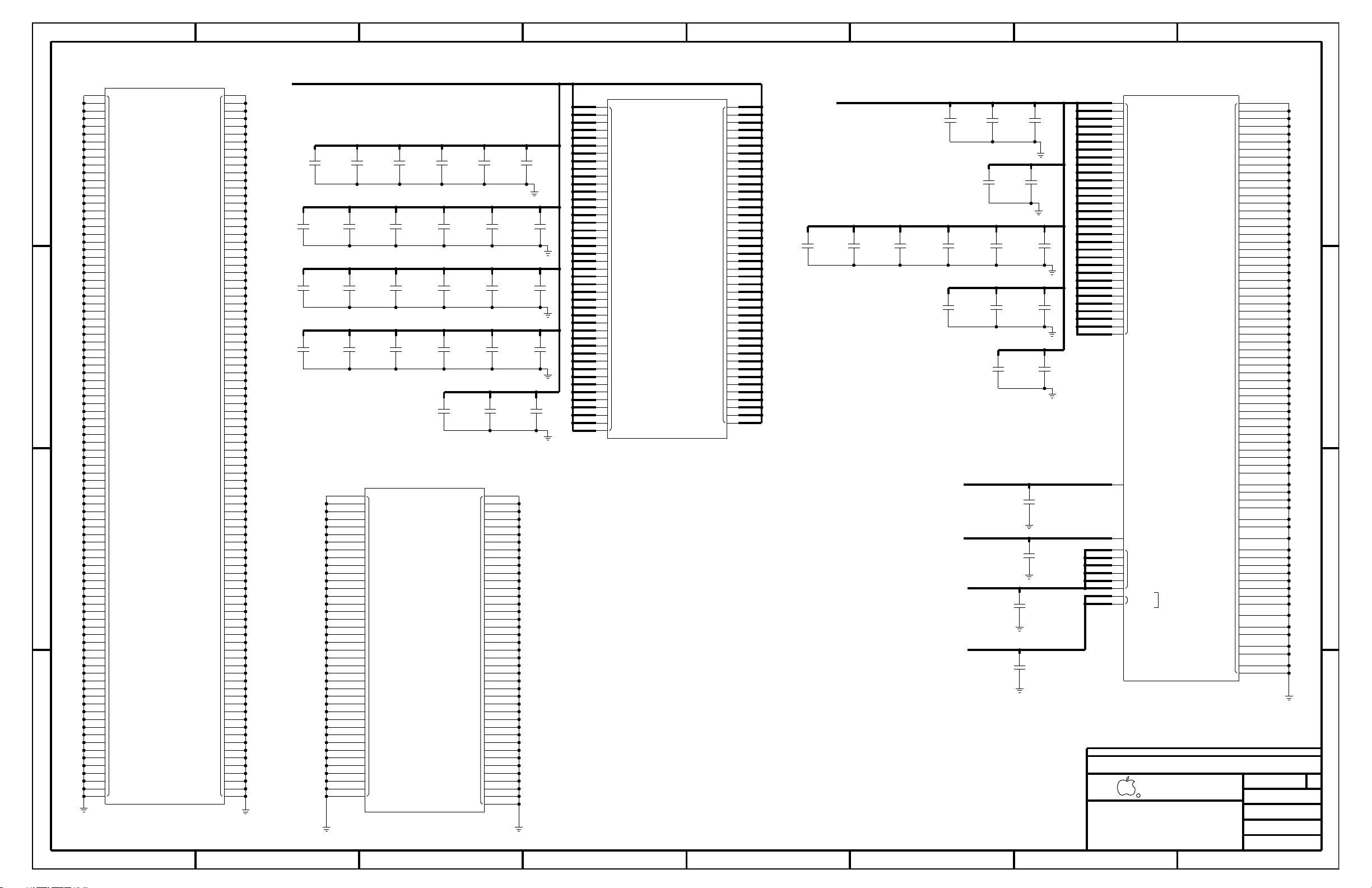

BRD_REV[2-0]

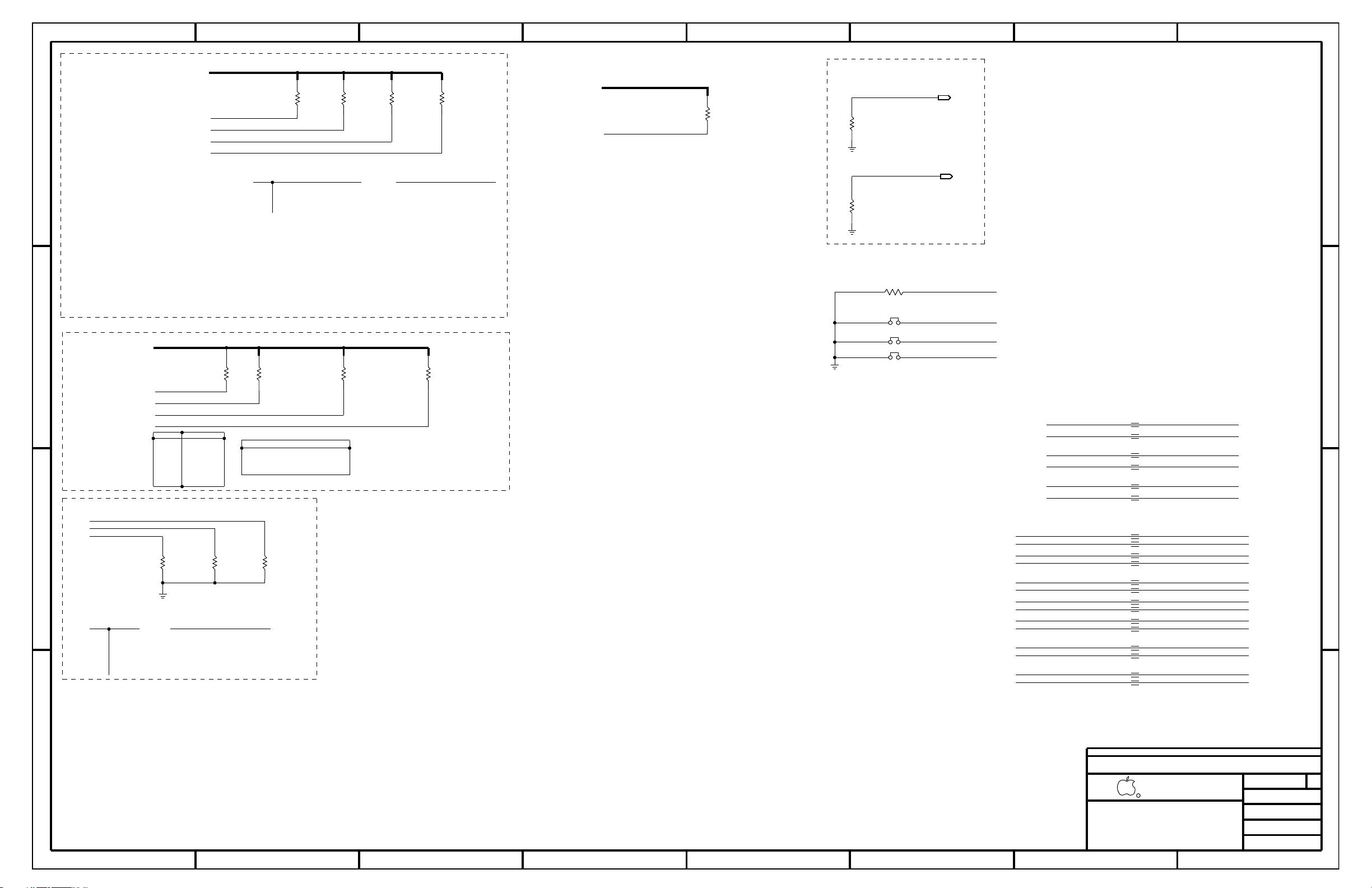

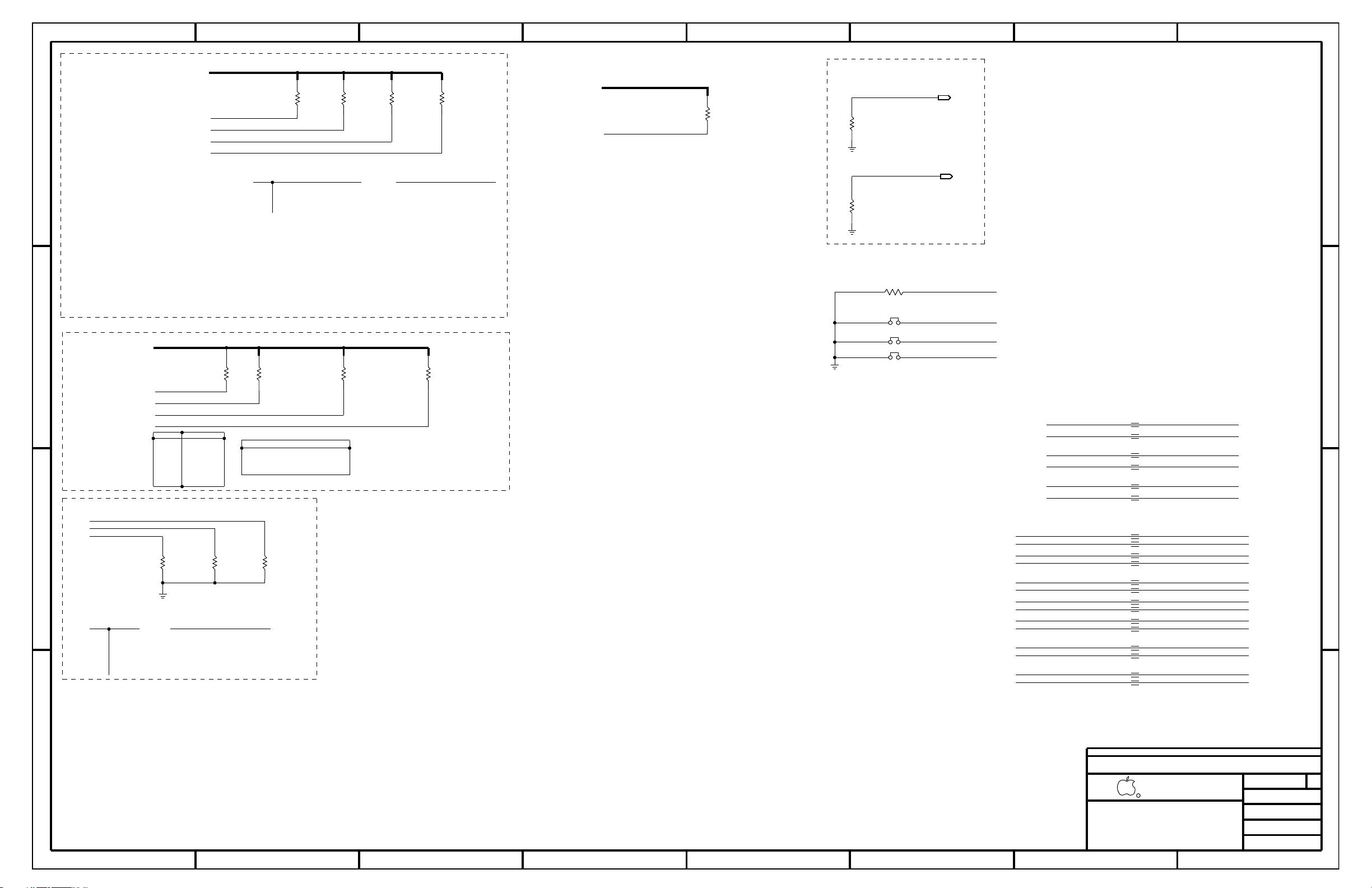

SINGLE-PIN NETS

1011 P105 DEV

BOARD_ID[1]

BOARD_ID[2]

BOARD_ID[3]

3. READ

S/W READ FLOW

1. SET GPIO AS INPUT

1110 FMI0/1 4/4 CS W/TEST

1011 RESERVED

BOARD ID

BOOT_CONFIG[2] (GPIO28)

BOOT_CONFIG[0] (GPIO18)

BOOT_CONFIG[1] (GPIO25)

S/W READ FLOW

BOOT_CONFIG[3:0]

0100 FMI0 2CS

0111 RESERVED

FOR REFERENCE

0010 SPI0 W/TEST

0001 SPI3

0011 SPI3 W/TEST

1. SET GPIO AS INPUT

2. ENABLE PU AND DISABLE PD

3. READ

DVT

000

010

100

011

001

JTAG

3. READ

BOOT_CONFIG[3] (GPIO29)

2. DISABLE PU AND ENABLE PD

NOTE: PADS USED FOR DEBUG

BOOT CONFIG ID

BOOT_CONFIG[3-0]

2. DISABLE PU AND ENABLE PD

1. SET GPIO AS INPUT

ID[3-0] SYSTEM

BOARD_ID[0]

X123A

X123B

1100 P106 AP

1101 P106 DEV

1110 P107 AP

1111 P107 DEV

1010 P105 AP

1111 RESERVED

S/W READ FLOW

BOARD REVISION

1101 FMI0/1 4/4 CS

1100 FMI0/1 2/2 CS

1010 FMI1 4CS W/TEST

0110 FMI0 4CS W/TEST

1001 FMI1 4 CS

1000 FMI1 2 CS

0101 FMI0 4CS

0000 SPI0

CURRENT SETTING ->

1100

FMI0/1 2/2 CS

5%

2.2K

01005

1/32W

MF

BOARD_ID_P105_P107

R1205

3

44

R1201

MF

1/32W

01005

2.2K

5%

MF

1/32W

2.2K

5%

01005

R1200

5%

2.2K

01005

1/32W

MF

R1203

FMI_4CS_NOTEST

MF

1/32W

01005

2.2K

5%

BOARD_ID_DEV

R1206

BOARD_ID_P106_P107

5%

2.2K

01005

1/32W

MF

R1204

SHORT-01005

XW0602

SHORT-01005

XW0601

SHORT-01005

XW0603

01005

1/32W

MF

100

5%

R1260

1/20W

5%

MF

1K

201

NOSTUFF

R1270

01005

1/32W

2.2K

5%

MF

R1213

3

01005

MF

1/32W

5%

100

R1210

R1202

2.2K

5%

MF

1/32W

01005

FMI_4CS_TEST

01005

MF

1/32W

5%

100

R1211

NOSTUFF

5%

2.2K

01005

1/32W

MF

R1207

NOSTUFF

2.2K

MF

1/32W

01005

5%

R1208

5%

2.2K

01005

1/32W

MF

R1209

AP: MISC & ALIASES

SYNC_DATE=04/11/2011

SYNC_MASTER=N/A

GPIO_BOOT_CONFIG1

GPIO_BOARD_REV2

GPIO_BOOT_CONFIG3

=PP1V8_H4

GPIO_BOOT_CONFIG2

GPIO_BOOT_CONFIG0

FMI0_RE_P

FMI1_DQS_N

NC_FMI0_DQS_NEG

MAKE_BASE=TRUE

NC_FMI0_RE_POS

MAKE_BASE=TRUE

NC_FMI1_DQS_NEG

MAKE_BASE=TRUE

NC_FMI1_RE_POS

MAKE_BASE=TRUE

NC_PMU_SHDWN

MAKE_BASE=TRUE

NC_JTAG_SOC_TDO

MAKE_BASE=TRUE

JTAG_SOC_TDO

PMU_SHDWN

FMI1_RE_P

FMI0_DQS_N

GPIO_BOARD_REV1

GPIO_BOARD_ID2

GPIO_BOARD_ID1

=PP1V8_H4

GPIO_BOARD_ID0

SOC_TST_STPCLK

SOC_HOLD_RESET

SOC_FAST_SCAN_CLK

SOC_TESTMODE

JTAG_SOC_SEL

JTAG_SOC_TRST_L

GPIO_BOARD_REV0

=PP1V8_S2R_MISC

GPIO_FORCE_DFU

GPIO_BOARD_ID3

NC_MIPI0C_CAM_REAR_DATA_N<2>

NC_AP_MIPI0C_DNDATA2

MAKE_BASE=TRUE

NC_MIPI0C_CAM_REAR_DATA_P<2>

NC_AP_MIPI0C_DPDATA2

MAKE_BASE=TRUE

NC_MIPI0C_CAM_REAR_DATA_N<3>

NC_AP_MIPI0C_DNDATA3

MAKE_BASE=TRUE

NC_MIPI0C_CAM_REAR_DATA_P<3>

NC_AP_MIPI0C_DPDATA3

MAKE_BASE=TRUE

NC_MIPI1D_AP_CLK_PNC_AP_MIPI1D_DPCLK

MAKE_BASE=TRUE

NC_MIPI1D_AP_CLK_NNC_AP_MIPI1D_DNCLK

MAKE_BASE=TRUE

NC_MIPI1D_AP_DATA_P<0>NC_AP_MIPI1D_DPDATA0

MAKE_BASE=TRUE

NC_MIPI1D_AP_DATA_N<0>NC_AP_MIPI1D_DNDATA0

MAKE_BASE=TRUE

NC_USB_FS_D_PNC_AP_USB11_DPD

MAKE_BASE=TRUE

NC_USB_FS_D_NNC_AP_USB11_DND

MAKE_BASE=TRUE

NC_AP_MIPI1D_DNDATA1

MAKE_BASE=TRUE

NC_AP_MIPI1D_DPDATA1

MAKE_BASE=TRUE

NC_MIPI1D_AP_DATA_N<1>

NC_MIPI1D_AP_DATA_P<1>

NC_MIPI1C_CAM_FRONT_DATA_P<1>

NC_MIPI1C_CAM_FRONT_DATA_N<1>

MAKE_BASE=TRUE

NC_AP_MIPI1C_DPDATA1

MAKE_BASE=TRUE

NC_AP_MIPI1C_DNDATA1

051-9374

13.0.0

12 OF 102

9 OF 46

1

2

1

2

1

2

1

2

1

2

1

2

12

12

12

12

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

4

4

4

3 4 6 9

39

4

4

11

11

3

44

42

11

11

4

4

4

3 4 6 9

39

4

3

3

3

3

4

4

10 39

4

4

6

6

6

6

6

6

6

6

3

3

6

6

6

6