Xilinx 7系列FPGA时钟资源使用规则和设计指南

下载需积分: 50 | PDF格式 | 1.12MB |

更新于2024-09-12

| 153 浏览量 | 举报

Xilinx 7系列FPGA时钟资源使用规则

Xilinx 7系列FPGA时钟资源是 FPGA 设计中非常重要的一部分,对于 FPGA 的时钟系统设计和实现有着至关重要的影响。了解 Xilinx 7系列FPGA时钟资源的使用规则对于 FPGA 设计者的设计和实现具有重要意义。

一、Clocking Resources 概述

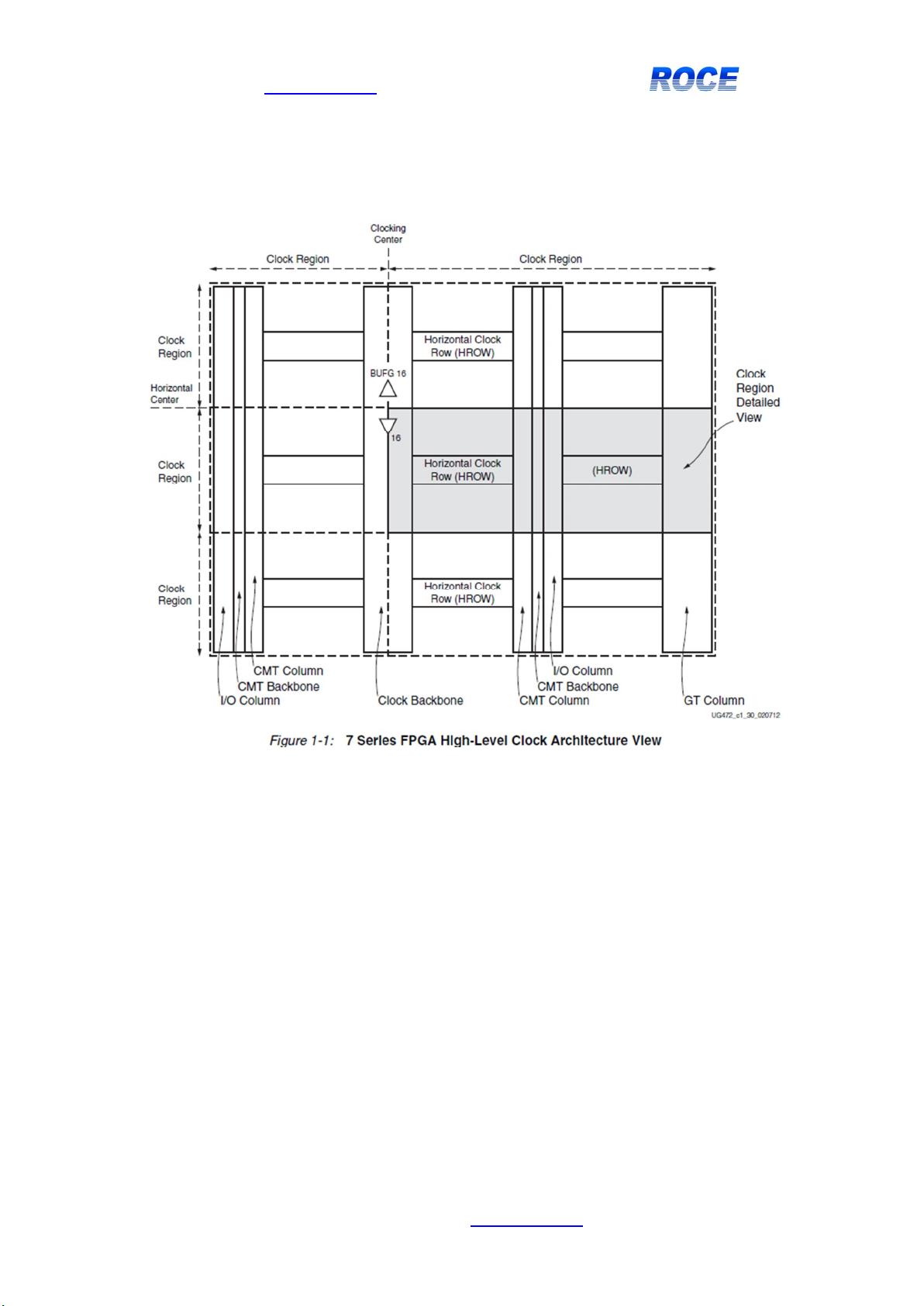

Xilinx 7系列FPGA时钟资源主要包括 Clock Management Tiles (CMT)、Clock Backbone、Horizontal Center、HROW 等几个部分。其中,CMT 由一个 MMCM 和一个 PLL 组成,提供了频率合成、去偏差、过滤抖动的功能。Clock Backbone 把芯片分成左右两半部分,而 Horizontal Center 把芯片分成上下两半部分,对 BUFG 的使用有一些限制。HROW 在每个时钟域的中部。

二、时钟域结构

一个时钟域包含 50 CLBs、10 个 36K block RAM、20 个 DSP 和 12 个 BUFH、一个 CMT、一个 IO Bank (50 I/Os)、一个 GTquard (视不同型号而定)。每个时钟域都可以驱动该时钟域下的所有时钟点。

三、BUFH 和 BUFG 的使用

BUFH 和 BUFG 共享 12 条布线资源,可以驱动该时钟域下的所有时钟点。BUFH 和 BUFG 可以驱动水平邻近时钟域下的时钟资源。CMTs、CC 管脚、GT 管脚可以通过 BUFH 驱动水平邻近时钟域下的时钟资源。

四、BUFIO 和 BUFR 的使用

BUFIO 和 BUFR 只横跨一个 bank,每个 bank 有 4 个 BUFIO、4 个 BUFR。BUFMR/BUFMRCE 可以完成垂直 BANK 之间的时钟互联,BUFMR/BUFMRCE 可以驱动垂直邻近时钟域的 BUFIO 和 BUFR。

五、CMT 的使用

CMT 由一个 MMCM 和一个 PLL 组成,提供了频率合成、去偏差、过滤抖动的功能。7系列必须通过设置特定的属性完成 CMT 的级联(会有相位偏移)。相邻 CMT 之间的级联由于资源有限并不被 Xilinx 推荐。

六、BUFIO 的时钟使能信号

BUFIO 的时钟使能信号允许输入信号的同步使能或异步使能。BUFIO 的时钟使能信号可以根据不同的应用场景进行设置。

七、Xilinx 7系列FPGA时钟资源的更新

与 V6FPGA 的区别是,BUFIO、BUFR 只横跨一个 bank,每个 bank 有 4 个 BUFIO、4 个 BUFR。使用 BUFMR/BUFMRCE 完成垂直 BANK 之间的时钟互联。GC 输入管脚被 CCIO(clock-capable clock input pin/pairs)替代,每个 bank 有 4 对 CCIO,比 GC 更强大。BUFUGMUX 增加了 CLK_SEL_TYPE 属性,用于两个输入时钟同步或异步方式的选择。

Xilinx 7系列FPGA时钟资源的使用规则对于 FPGA 设计者的设计和实现具有重要意义。了解这些规则可以帮助设计者更好地设计和实现 FPGA 的时钟系统,从而提高 FPGA 的性能和可靠性。

相关推荐

1548 浏览量

rocetech

- 粉丝: 0

- 资源: 2