ARM920T MMU与Cache详解:虚拟内存与硬件协作

需积分: 13 35 浏览量

更新于2024-07-26

1

收藏 1.79MB PDF 举报

MMU与Cache详解深入解析ARM920T架构

在ARM920T处理器中,内存管理单元(MMU)和Cache是两个关键组件,它们在提高系统性能、保护系统资源以及实现虚拟内存管理方面起着至关重要的作用。

一、虚拟地址与物理地址

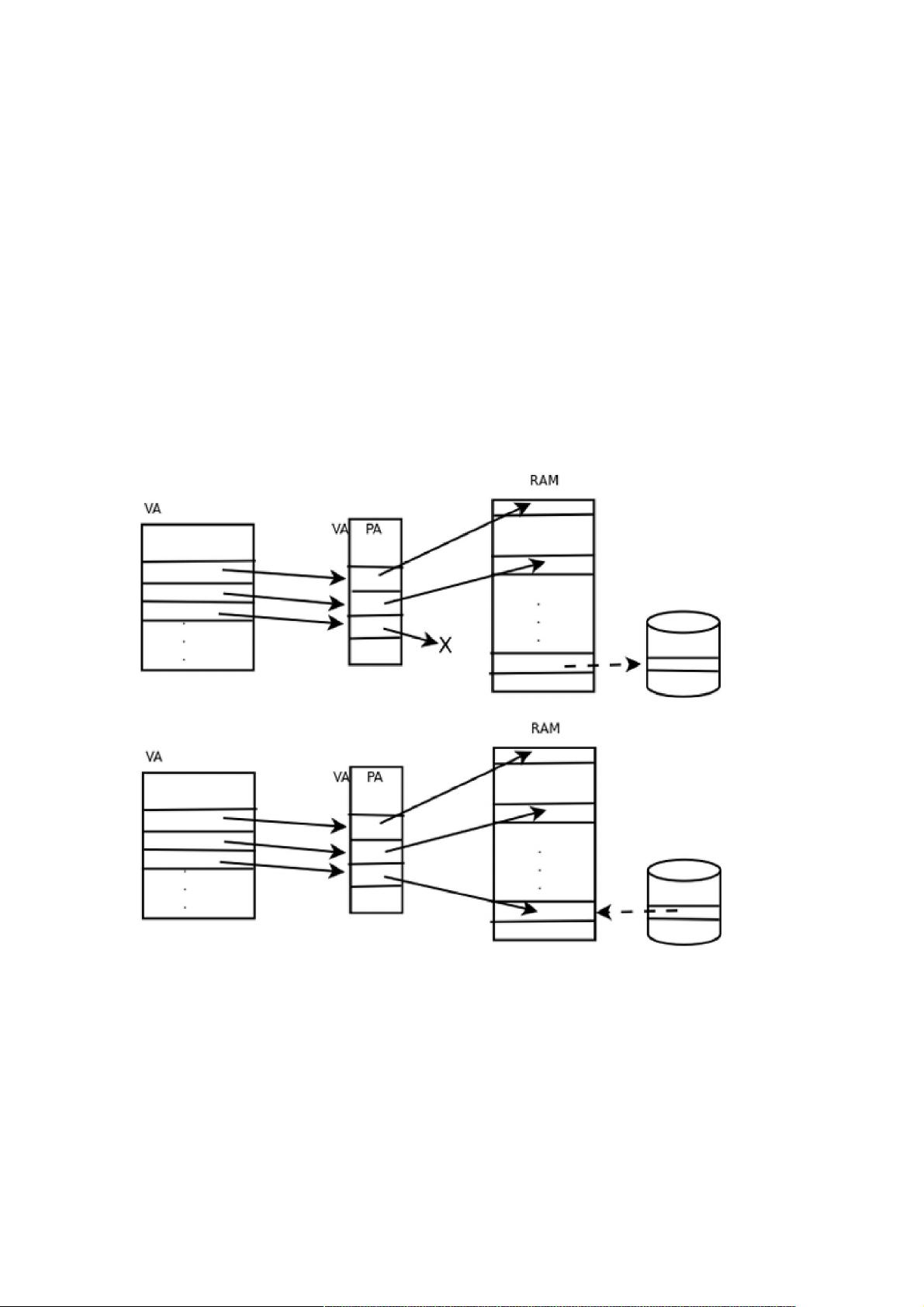

在计算机体系结构中,CPU通过地址来访问内存。地址有两种形式:虚拟地址(VA,Virtual Address)和物理地址(PA,Physical Address)。当CPU未启用MMU或MMU未激活时,发出的地址是物理地址,它直接指向内存芯片上的存储单元。然而,MMU的存在使得CPU能够处理虚拟地址,这是一种逻辑地址,与硬件无关,由操作系统管理和转换。

在32位CPU中,比如ARM920T,虚拟地址空间通常为4GB,每一页大小为4KB。MMU将虚拟地址分解为页,将虚拟地址0xb7001000~0xb7001fff映射到物理地址0x2000~0x2fff,这样的映射是页级别的。

二、虚拟内存管理

现代操作系统利用MMU的功能进行虚拟内存管理。以进程地址空间为例,每个进程都有自己的地址空间,如bash进程,其地址范围被划分为不同的区域,包括代码段(只读)、数据段(可读写)和堆区(可读写但不关联特定磁盘文件)。操作系统通过虚拟内存管理系统(VMS)确保这些区域的安全性和资源隔离,限制用户进程对内核空间的访问,并动态分配和回收内存。

三、MMU功能

ARM920T的CP15协处理器负责管理MMU,它执行地址变换,将虚拟地址转换为物理地址。这个过程涉及到页表和页目录等数据结构,用于跟踪和维护虚拟地址到物理地址的映射关系。MMU能够提供内存保护,确保不同进程之间的数据隔离,防止非法访问。

四、Cache优化

ARM920T还配置了Cache,这是一种高速缓冲存储器,用于存储频繁访问的数据,减少内存访问时间。Cache通过缓存指令和数据,提升了系统的整体性能。在内核启动代码中,开发者需操作MMU和Cache设置,确保它们与系统的初始化和运行模式协同工作,例如设置Cache的替换策略、缓存行大小等参数。

五、参考资料

理解ARM920T的MMU与Cache工作原理,需要参考相关的技术文档和教程,这些资料可以帮助深入学习MMU的内部结构、页表管理、内存分配算法以及Cache的实现细节。同时,了解现代操作系统如Linux内核如何利用这些特性来优化内存使用和提升性能也是十分必要的。

总结,MMU和Cache在ARM920T中扮演着核心角色,它们共同构成了高性能计算的基础,确保了系统的可靠性和效率。深入研究这两个组件有助于开发人员编写更高效的代码和优化系统性能。