数字分频器对锁相环相位噪声与杂散影响的研究

" 本文深入探讨了锁相环中数字分频器对输出信号相位噪声和杂散的影响,分析了数字分频器的非线性特性如何导致线性模型预测误差,并提出了一种新的计算方法以提高预测准确性。

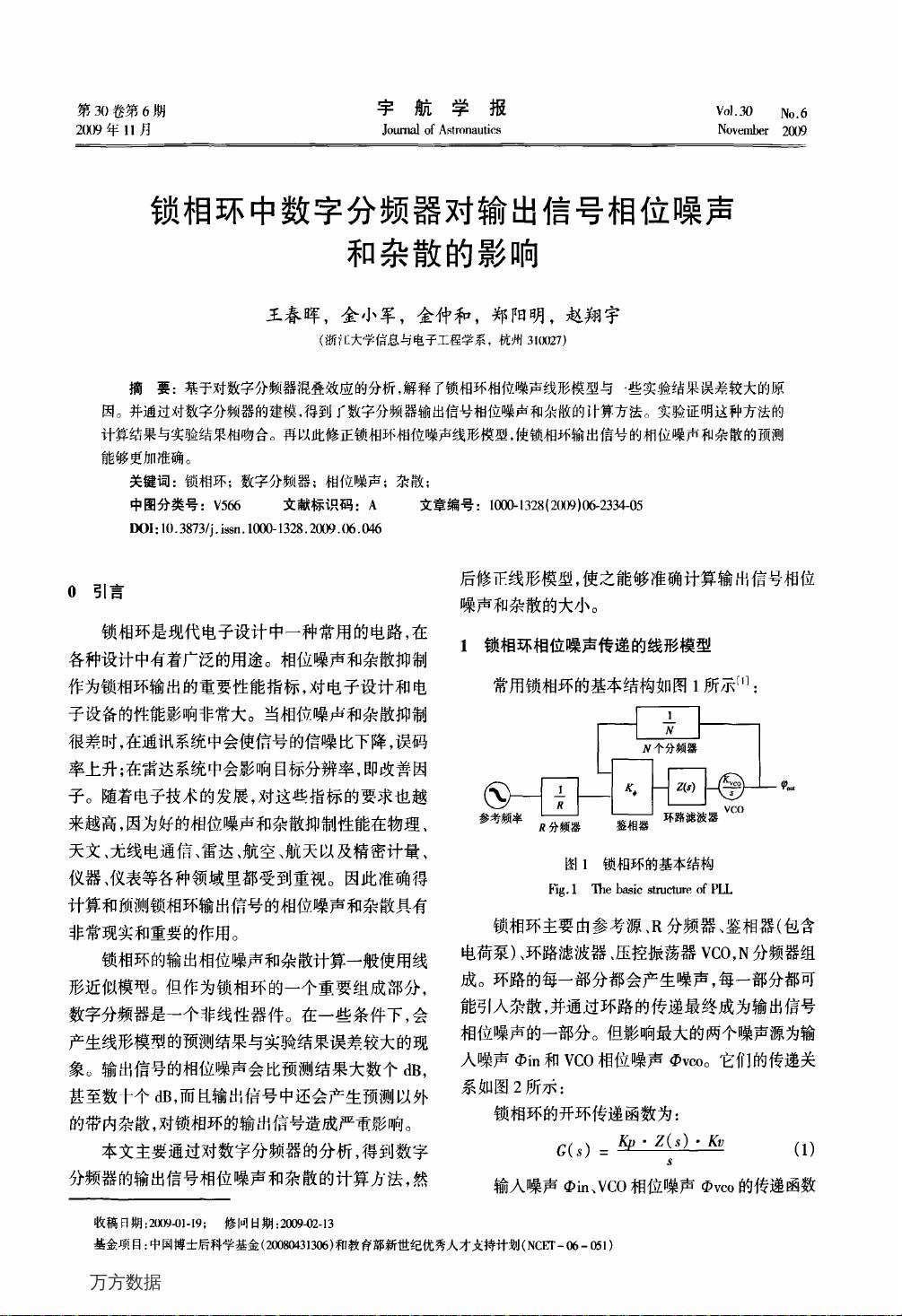

锁相环(Phase-Locked Loop,PLL)是电子系统中的关键组件,广泛应用于频率合成、数据通信和信号处理等领域。其工作原理是通过比较输入参考信号和由压控振荡器(VCO)产生的信号之间的相位差,以调整VCO的频率,从而实现锁定状态。在这个过程中,相位噪声和杂散是衡量锁相环性能的重要参数,直接影响系统的通信质量和分辨率。

传统的锁相环相位噪声分析通常采用线性模型,该模型简化了环路内部各组件的复杂行为,但忽略了数字分频器的非线性效应。数字分频器(Digital Divider)在锁相环中起到下变频和频率分频的作用,但由于其工作方式,可能会引入混叠效应,导致输出相位噪声增加和未预期的带内杂散产生。这种现象可能导致实际测量值与理论预测值之间存在显著差异。

作者王春晖等人通过分析数字分频器的工作机制,建立了一个更精确的模型,以计算数字分频器输出的相位噪声和杂散。他们通过实验验证了该模型的有效性,计算结果与实验数据吻合良好。利用这个改进的模型,可以更准确地预测锁相环输出信号的相位噪声和杂散,这对于优化锁相环设计和提升系统性能至关重要。

在文章中,作者首先介绍了锁相环的基本结构,包括鉴相器、低通滤波器和VCO,然后详细阐述了线性模型的局限性,尤其是数字分频器的非线性特性如何导致预测误差。接着,他们提出了数字分频器的数学模型,并展示了如何运用这个模型计算相位噪声和杂散。最后,通过实例对比,证明了新模型相对于传统线性模型的优越性。

这篇文章对理解和改进锁相环系统中的相位噪声和杂散控制提供了有价值的见解。对于电子工程师和研究人员来说,了解数字分频器的非线性影响以及如何通过修正模型来准确预测性能,是优化锁相环设计的关键。"

916 浏览量

960 浏览量

591 浏览量

2023-02-28 上传

2023-02-28 上传

简易锁相环技术介绍:从鉴频鉴相到压控振荡器的精确锁定流程详解 - 基于SMIC 130mmrf工艺、快速锁定、超低相位噪声和matlab优化方案支持 ,简易锁相环电路设计:输入20MHz输出800MH

2025-02-14 上传

2021-11-19 上传

3161 浏览量

drager11

- 粉丝: 0

最新资源

- Web远程教学系统需求分析指南

- 禅道6.2版本发布,优化测试流程,提高安全性

- Netty传输层API中文文档及资源包免费下载

- 超凡搜索:引领搜索领域的创新神器

- JavaWeb租房系统实现与代码参考指南

- 老冀文章编辑工具v1.8:文章编辑的自动化解决方案

- MovieLens 1m数据集深度解析:数据库设计与电影属性

- TypeScript实现tca-flip-coins模拟硬币翻转算法

- Directshow实现多路视频采集与传输技术

- 百度editor实现无限制附件上传功能

- C语言二级上机模拟题与VC6.0完整版

- A*算法解决八数码问题:AI领域的经典案例

- Android版SeetaFace JNI程序实现人脸检测与对齐

- 热交换器效率提升技术手册

- WinCE平台CPU占用率精确测试工具介绍

- JavaScript实现的压缩包子算法解读