Quartus II 设计自动化工具简介

需积分: 16 108 浏览量

更新于2024-07-24

2

收藏 2.62MB PDF 举报

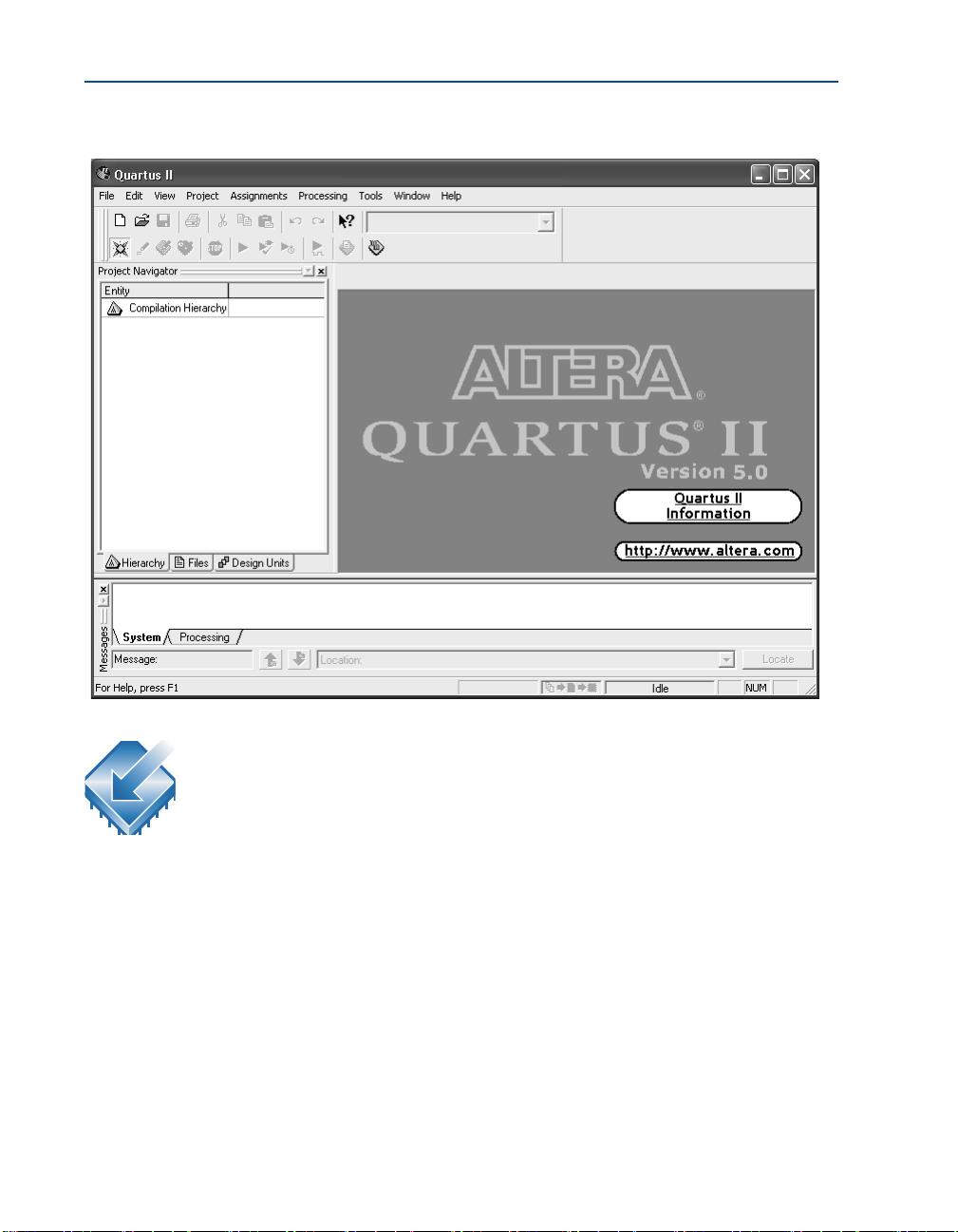

Quartus II 简介

Quartus II 是 Altera 公司的一款 FPGA 开发软件,用于设计和开发基于 FPGA 的数字电路。Quartus II 是 Altera 公司的注册商标。

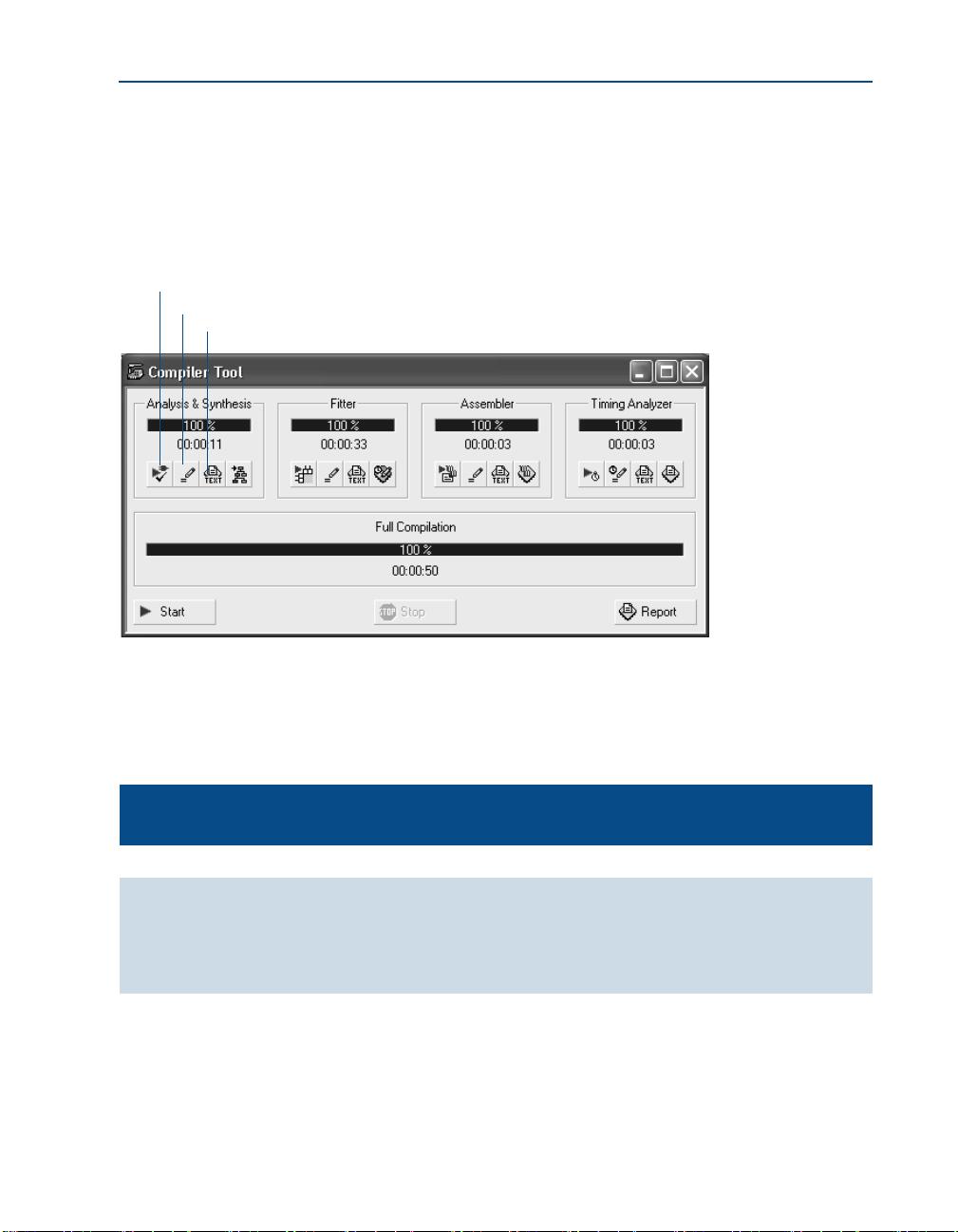

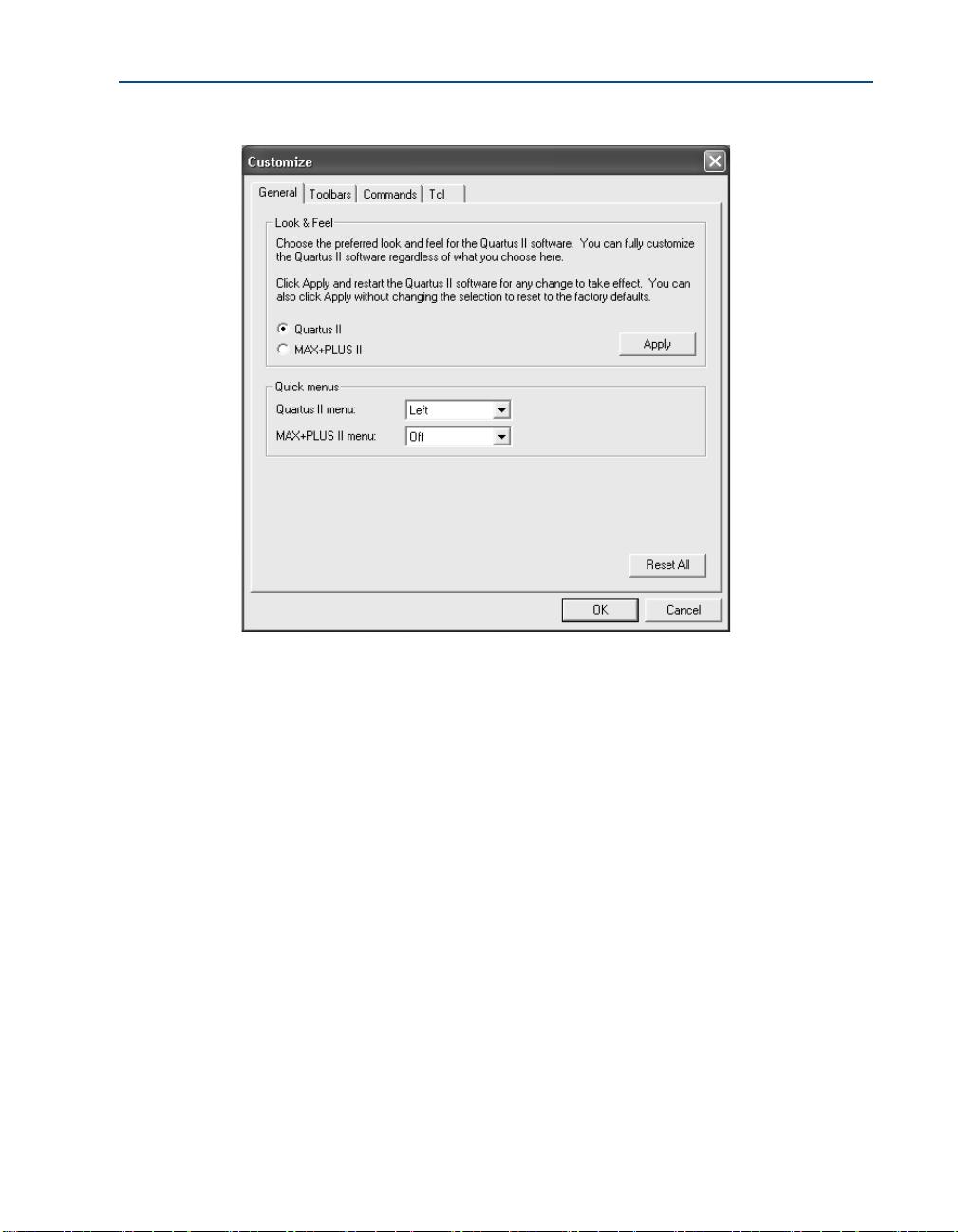

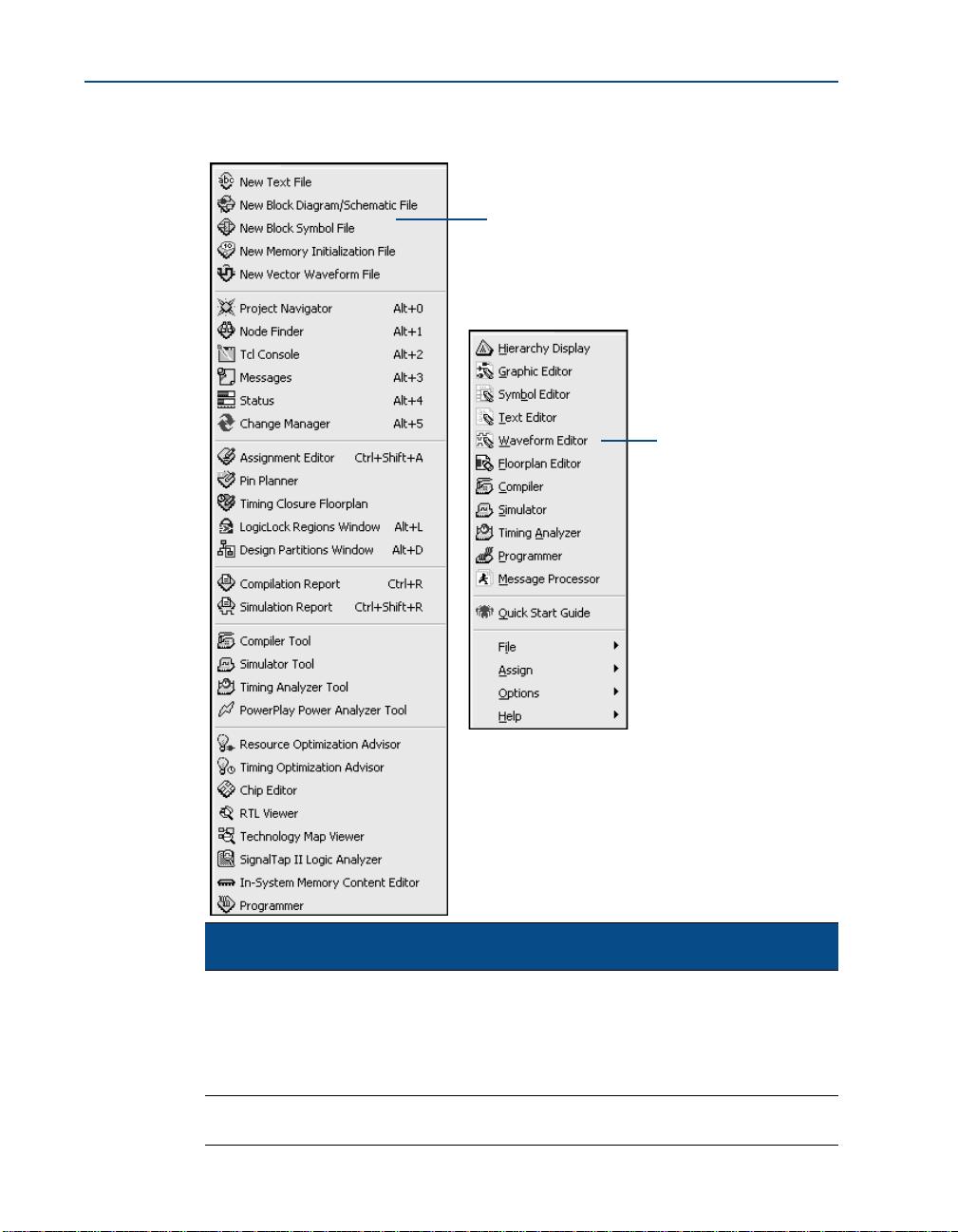

Quartus II 的主要特点是提供了一个集成的开发环境,包括设计、仿真、编译和烧写等功能。用户可以使用 Quartus II 来设计和开发基于 FPGA 的数字电路,包括数字信号处理、数据处理和控制系统等。

Quartus II 的主要应用领域包括数字信号处理、数据处理、控制系统、通信系统、军事电子、汽车电子、医疗电子、消费电子等。

Quartus II 的版本历史包括:

* 版本 5.0:这是 Quartus II 的第一个版本,发布于 2005 年 4 月。这版本引入了许多新的功能,包括设计环境、仿真环境和编译环境的改进。

Quartus II 的主要特点包括:

* 集成的开发环境:Quartus II 提供了一个集成的开发环境,包括设计、仿真、编译和烧写等功能。

* 高性能:Quartus II 能够实现高性能的数字电路设计和开发。

* 广泛的应用领域:Quartus II 可以应用于数字信号处理、数据处理、控制系统、通信系统、军事电子、汽车电子、医疗电子、消费电子等领域。

Quartus II 的技术支持包括:

* 文档支持:Quartus II 提供了详细的文档支持,包括使用手册、指南、应用笔记等。

* 在线支持:Quartus II 提供了在线支持,包括技术支持论坛、在线帮助等。

* 训练支持:Quartus II 提供了培训支持,包括在线培训、脱机培训等。

Quartus II 的版权和商标信息包括:

* Altera、Altera 标识、FastTrack、HardCopy、MAX、MAX+PLUS、MAX+PLUSII、MegaCore、MegaWizard、NativeLink、Nios、OpenCore、Quartus、QuartusII、QuartusII 标识和 SignalTap 是 Altera 公司在美国和其他国家的注册商标。

* Avalon、ByteBlaster、ByteBlasterMV、Cyclone,Excalibur,IPMegaStore,Jam,LogicLock、MasterBlaster,MegaLAB,PowerFit,SignalProbe,Stratix 和 USB-Blaster 是 Altera 公司在美国和其他国家的商标以及服务标志。

Quartus II 是一个功能强大且广泛应用的 FPGA 开发软件,可以满足数字电路设计和开发的需求。

2010-05-29 上传

2009-09-26 上传

2022-09-19 上传

2012-06-12 上传

2022-08-03 上传

2008-11-03 上传

2022-08-03 上传

jiangboyu1993

- 粉丝: 1

- 资源: 2

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率