NCP1650芯片演示:100W PFC转换器的广泛特性与保护功能

需积分: 9 60 浏览量

更新于2025-01-07

收藏 61KB PDF 举报

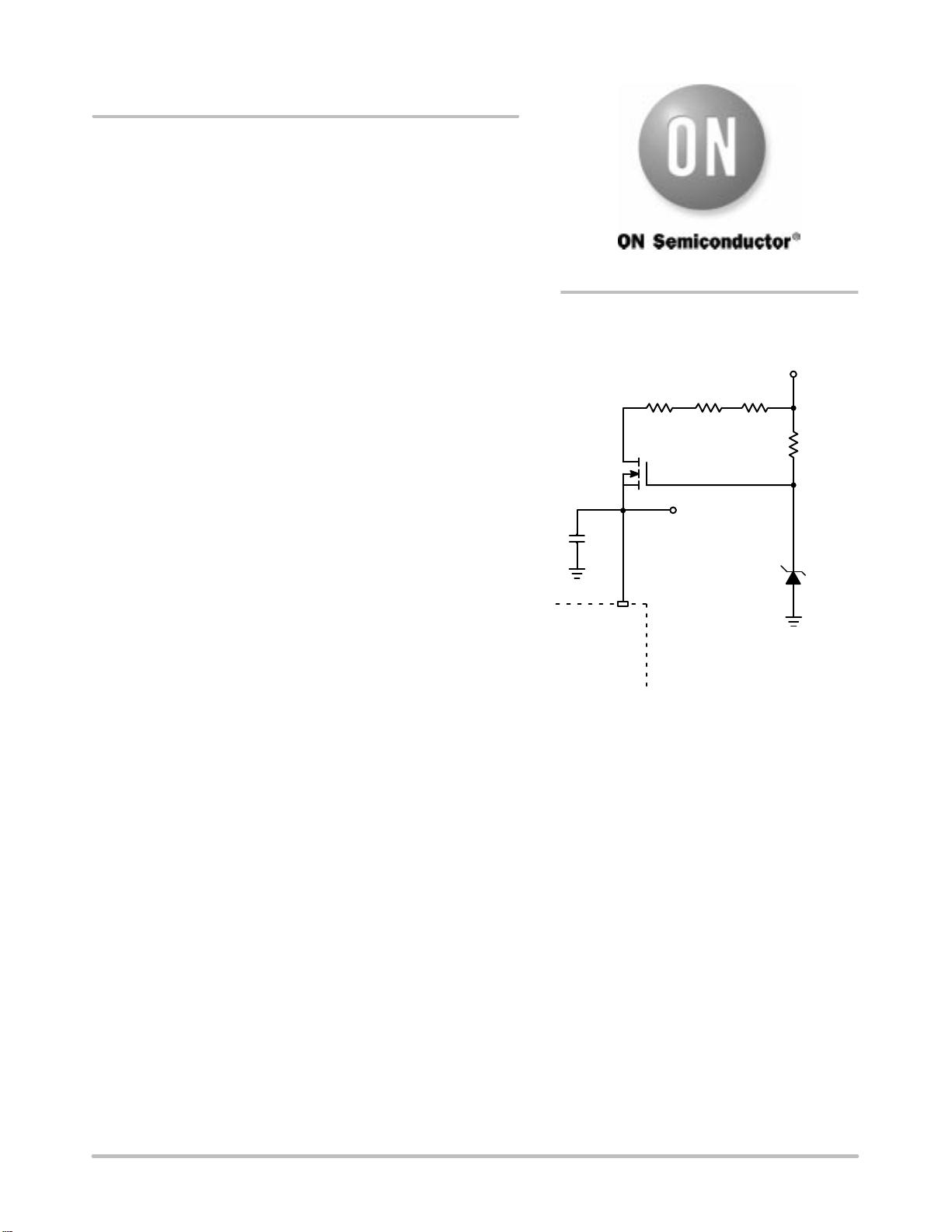

标题:"PFC电路1212121" 提供了一篇关于高性能100瓦功率因数校正(PFC)转换器的详细介绍。该转换器基于ON Semiconductor的NCP1650芯片设计,旨在实现宽范围的特性,尤其在千瓦级别以下的控制能力。PFC电路的主要目的是提高电力设备的效率,通过改善输入电源的功率因数,减少电网的谐波干扰。

描述中提到,这款转换器具备固定频率操作,无论是连续模式还是断续模式下都能稳定工作。它还集成了多种保护功能,包括瞬时电流限制、平均电流限制以及真正的功率限制,确保系统的安全性和稳定性。这些特性使得该电路能够适应广泛的输入电压范围,从85Vrms到265Vrms,以及50Hz到60Hz的频率变化。

电路设计中特别强调了其固定频率控制,这意味着输出不会随着电网频率的变化而波动,提高了系统响应的精确性。此外,内置的关断电路确保了转换器在不需运行时的节能状态。为了简化集成,该PFC转换器包含了一个高电压启动电路,以及一个自供电的偏置电路,它可以从主的Boost电感器获取能量,进一步节省了外部元件的需求。

值得注意的是,该转换器还配备了多种保护机制,能够在各种异常情况下自动调整或关闭,确保系统免受过载或短路等故障的影响。同时,其内置的真正功率限制功能能有效防止长时间的过度功率消耗,从而保护整个电路系统和连接的负载。

总结来说,这款1212121号PFC电路是针对广泛应用场合设计的,它集成了高性能、高效率、多保护和易于集成的优势,是现代电子设备中提升能源利用效率的理想选择。

788 浏览量

2822 浏览量

182 浏览量

1787 浏览量

2025-02-22 上传

三相APFC电路与单相Boost PFC电路仿真模型:电压外环电流内环双闭环控制策略研究,三相电路仿真模型:APFC电路与单相BoostPFC电路的双闭环控制策略研究,APFC电路,单相PFC电路,单

2025-02-22 上传

897 浏览量

2025-01-22 上传

2025-01-18 上传

windylover

- 粉丝: 0

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例