绕过D盾IIS防火墙:SQL注入攻防策略及实战姿势

需积分: 0 125 浏览量

更新于2024-08-05

收藏 464KB PDF 举报

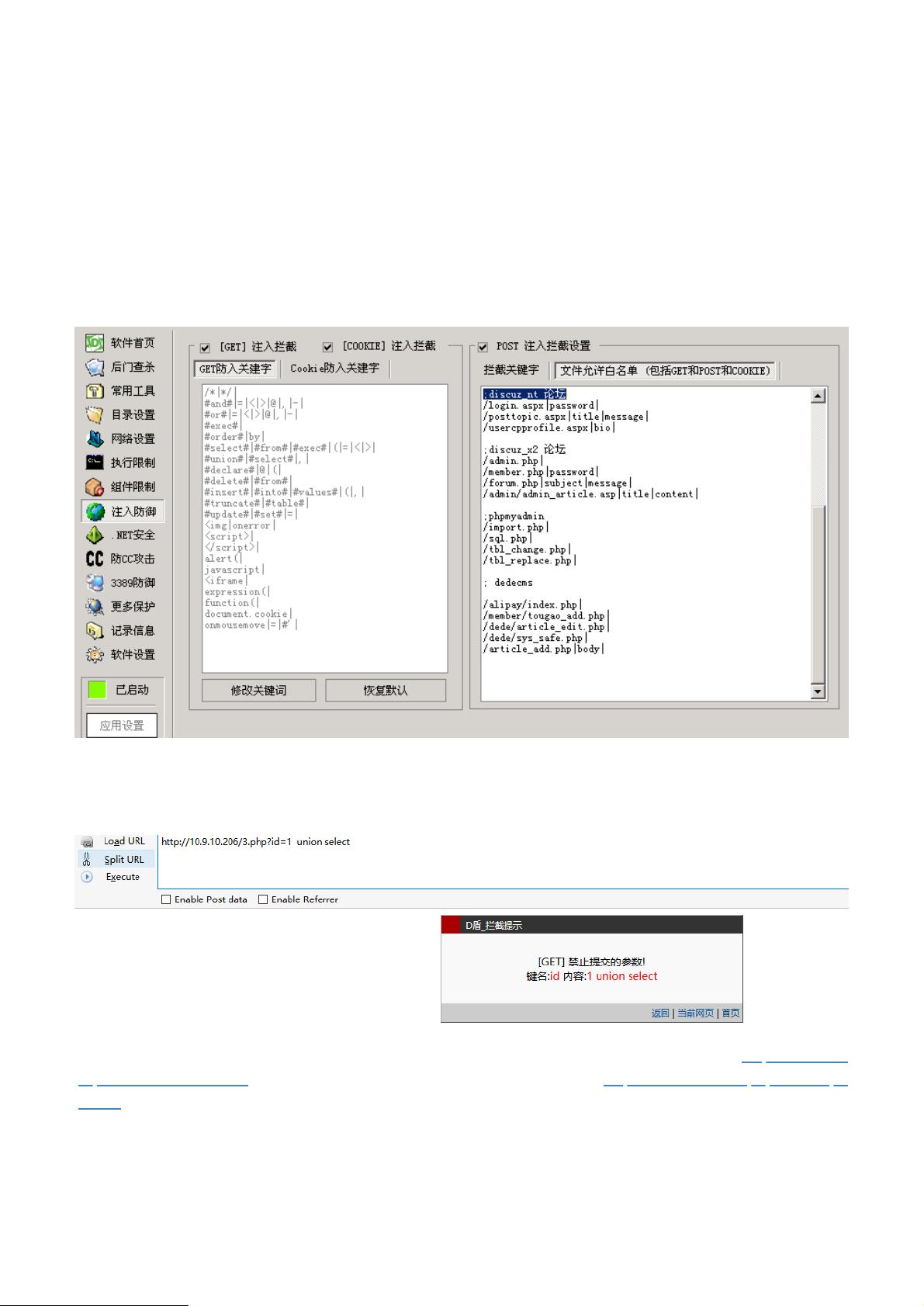

本文主要探讨的是如何在Windows 2003服务器环境下,使用IIS防火墙D盾进行SQL注入防御时的测试和绕过策略。D盾IIS防火墙主要针对GET、POST和COOKIE请求,并支持白名单设置,以防止恶意SQL注入攻击。作者针对三种不同环境——IIS+PHP+MySQL、IIS+PHP+MSSQL以及IIS+ASP/ASPX+MSSQL,进行了深入的实验和分析。

首先,作者提到白名单策略,这是基本的防护措施,但通过PHP中的PATH_INFO特性,攻击者可以利用URL路径的额外部分绕过过滤,例如在URL后面添加任意地址如`/admin.php?id=1unionselect1,2,schema_namefrominformation_schema.SCHEMATA`,即使在GET、POST和COOKIE请求中,这个技巧也能生效。

第二个绕过姿势涉及使用Mysql中的特殊字符,尤其是百分号编码的空格 `%a0`,攻击者巧妙地将其与`select`关键字结合,导致防火墙未能识别并阻止这种注入攻击。通过在SQL语句中插入`\N`,作者发现这是一种在unionselect检测前的潜在绕过方法,同时也适用于selectfrom检测。

在IIS+ASP/ASPX+MSSQL环境中,尽管防火墙策略更为复杂,但通过理解SQL注入攻击的原理,如利用路径变量和特殊字符,攻击者依然能找到策略来避开D盾的防护。这表明在实际应用中,仅仅依赖白名单和常规防御机制可能不足以抵挡高级的SQL注入攻击,开发者和安全专家需要不断更新防御手段并持续测试以应对不断演变的威胁。

本文提供了关于如何在IIS防火墙D盾下进行SQL注入测试,以及通过技术手段绕过其防御机制的方法,这对于理解和提升Web应用程序的安全性具有重要参考价值。同时,也提醒了开发者在设计和实施安全策略时,应注重动态防御和定期审计,以适应不断变化的威胁态势。

107 浏览量

133 浏览量

117 浏览量

150 浏览量

178 浏览量

柏傅美

- 粉丝: 33

最新资源

- 掌握AngularJs与Java Web服务器的交互技术

- 打造仿QQ商城焦点图效果的jQuery图片轮播

- Android签名工具signapk.jar的分析与研究

- Windows XP PPPoE驱动下载:搭建服务器的必需品

- OpenBOR迁至GitHUB:探索开源2D侧滚动引擎的全功能

- 深入理解TMS320C28x系列DSP的CPU架构与外设功能

- Matlab模糊控制查询表及其曲面图实现

- ETcad2014版——免安装快捷键设计软件

- C#银行交易管理系统VS SQL Server实现

- Delphi开发的干湿球湿度计算软件

- 聚合物Web组件:本地化日期时间选择器使用指南

- 跨域与固态认证协议的实体面板

- 探索HTML5与CSS3的权威指南-新书介绍

- 轻松阅读MS Project文档的免费浏览器

- Matlab Simulink六自由度平台仿真教程及素材

- Quartus II 8.0实现VHDL编程的可调数字时钟