没有合适的资源?快使用搜索试试~ 我知道了~

首页Apple Q59v13 电路设计与组件详细图

"APPLE Q59v13 图纸 电路图"

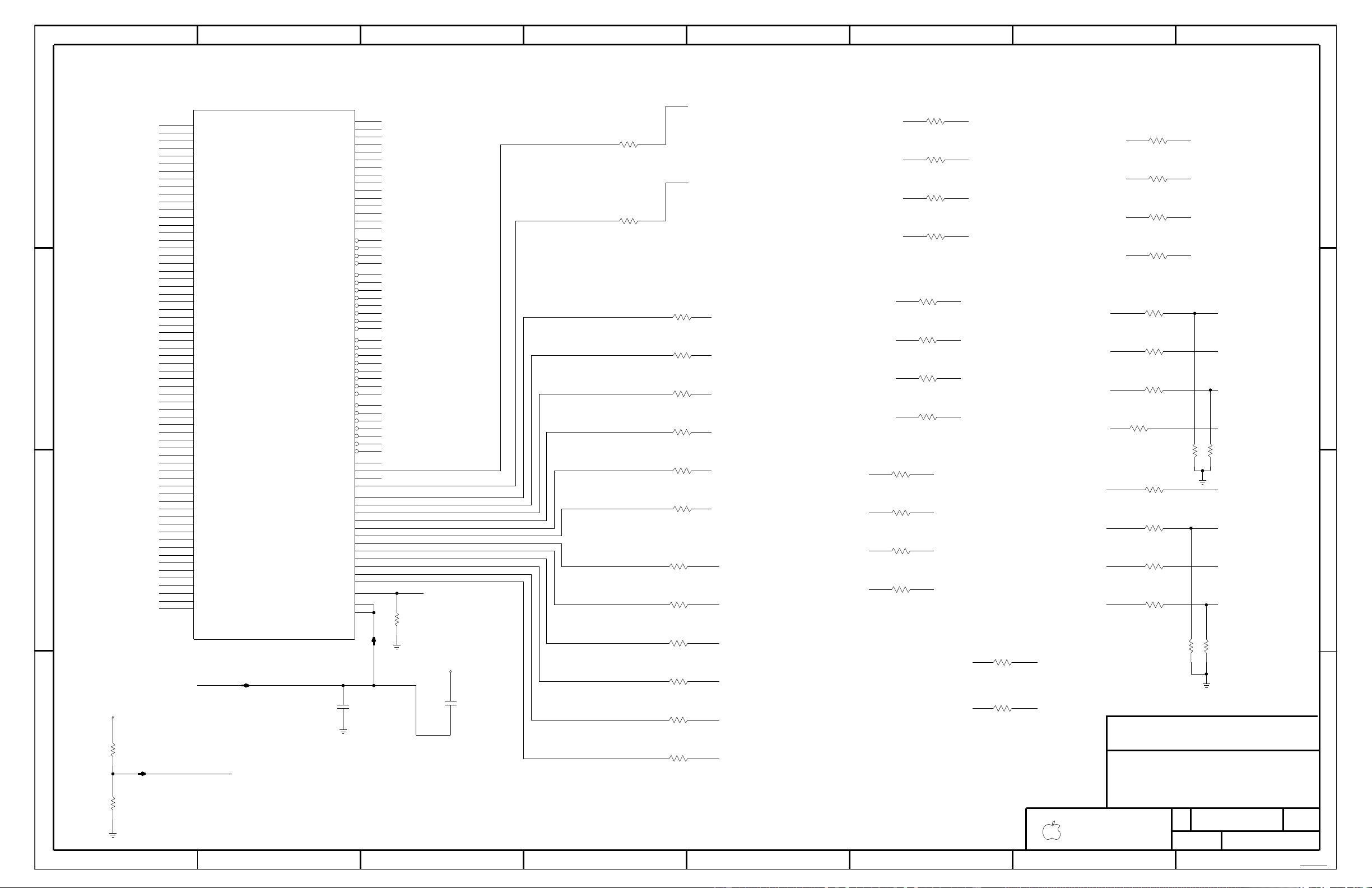

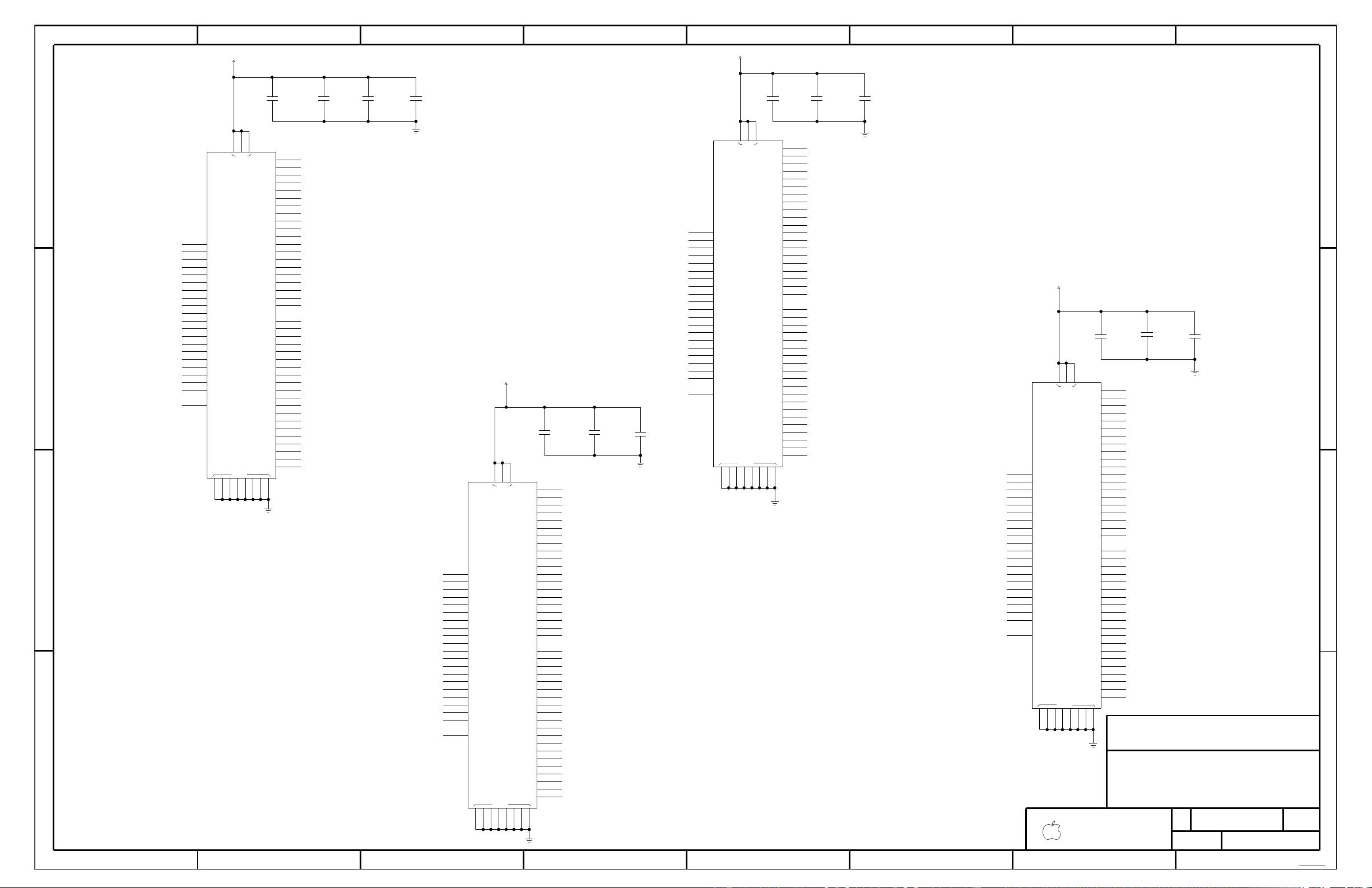

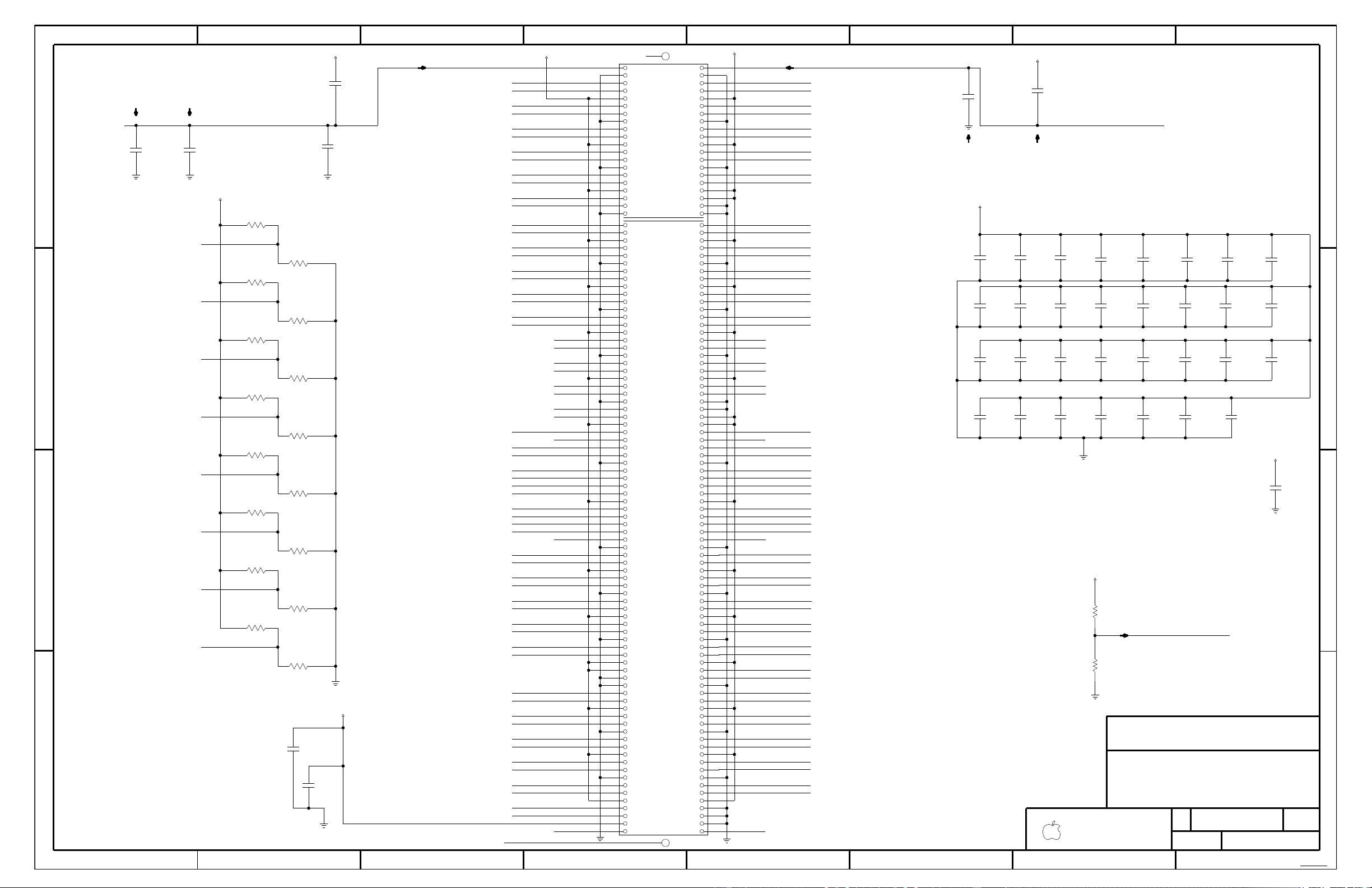

该文件是一份关于APPLE Q59v13型号的电路图,通常用于笔记本电脑的设计和维修。这份图纸包含了许多关键信息,如晶体振荡器的频率值、电容的微法拉单位、电阻的欧姆值以及相关的制造和设计细节。以下是对这份图纸的详细解读:

1. **电路图**:电路图是电子设备设计的核心,它展示了各个组件如何相互连接,形成一个完整的电路系统。在APPLE Q59v13的电路图中,我们可以看到电源管理、处理器连接、内存、显卡、无线接口、网络接口(Ethernet & FireWire)、模数转换器(DAC/DVI)、CPU连接器、扩展存储处理器(ESP)、CPU旁路,以及可能包括的蓝牙和调制解调器等模块。

2. **NVIDIA DAC/DVI, Clocks & Straps(第2和5部分)**:这部分涉及到图形处理单元(GPU)的数字模拟转换器(DAC),用于将数字信号转化为显示器可识别的模拟信号。DVI(Digital Visual Interface)是视频接口标准,而Clocks & Straps可能指的是GPU时钟信号和配置引脚,这些决定了GPU的工作模式和性能。

3. **Wireless PCI**:这可能指的是无线网络适配器,如Wi-Fi或蓝牙模块,它们通过PCI接口与主板通信。

4. **Intrepid Ethernet & FireWire (Section 4)**:Intrepid可能是以太网控制器的代号,提供有线网络连接;FireWire,也称为IEEE 1394,是一种高速数据传输接口,常用于连接外部设备。

5. **CPU Connectors, ESP, CPU Bypass**:CPU连接器指处理器与主板的接口;ESP(扩展存储处理器)可能是指辅助处理器,用于处理特定任务;CPU Bypass可能是一个功能,允许系统在CPU故障时仍能运行。

6. **Block Diagram, System, Power & PCB Info**:这部分包含了系统的整体架构图,包括电源管理的详细信息,以及印刷电路板(PCB)的设计细节。

7. **Table of Contents**:目录提供了图纸各个部分的快速参考,便于用户查找特定的信息。

8. **proprietary property**:文件明确指出,所有信息属于Apple Computer, Inc.,具有专有性质,要求接收者保守秘密,不泄露、复制或公开信息,表明其对Apple产品的知识产权保护。

总结起来,这份图纸详细描绘了APPLE Q59v13笔记本电脑的内部电路布局和组件交互,对于理解设备工作原理、故障排查和维护升级具有重要价值。由于图纸涉及的技术细节广泛且专业,通常只有具备电子工程背景的人员才能充分理解和利用其中的信息。

(2 OF 9)

DDR_VREF_1

DDR_VREF_0

DDR_DATA_0

DDR_DATA_1

DDR_DATA_2

DDR_DATA_3

DDR_DATA_4

DDR_DATA_5

DDR_DATA_6

DDR_DATA_7

DDR_DATA_8

DDR_DATA_9

DDR_DATA_10

DDR_DATA_11

DDR_DATA_12

DDR_DATA_13

DDR_DATA_14

DDR_DATA_15

DDR_DATA_16

DDR_DATA_17

DDR_DATA_18

DDR_DATA_19

DDR_DATA_20

DDR_DATA_21

DDR_DATA_25

DDR_DATA_26

DDR_DATA_27

DDR_DATA_28

DDR_DATA_29

DDR_DATA_30

DDR_DATA_33

DDR_DATA_34

DDR_DATA_35

DDR_DATA_36

DDR_DATA_37

DDR_DATA_38

DDR_DATA_39

DDR_DATA_40

DDR_DATA_41

DDR_DATA_42

DDR_DATA_43

DDR_DATA_44

DDR_DATA_45

DDR_DATA_46

DDR_DATA_47

DDR_DATA_48

DDR_DATA_49

DDR_DATA_50

DDR_DATA_51

DDR_DATA_52

DDR_DATA_53

DDR_DATA_54

DDR_DATA_55

DDR_DATA_56

DDR_DATA_57

DDR_DATA_58

DDR_DATA_59

DDR_DATA_60

DDR_DATA_61

DDR_DATA_62

DDR_DATA_63

DDR_DATA_22

DDR_DATA_23

DDR_DATA_24

DDR_DATA_31

DDR_DATA_32

DDR_BA_0

DDR_BA_1

DDRCS_3

DDRCS_2

DDRCS_1

DDRCS_0

DDR_DQS_7

DDR_DQS_6

DDR_DQS_5

DDR_DQS_4

DDR_DQS_3

DDR_DQS_2

DDR_DQS_1

DDR_DQS_0

DDR_DM_7

DDR_DM_6

DDR_DM_5

DDR_DM_4

DDR_DM_3

DDR_DM_2

DDR_DM_1

DDR_DM_0

DDRRAS

DDRCAS

DDRWE

DDRCKE0

DDRCKE1

DDRCKE2

DDRCKE3

DDR_MCLK_0_P

DDR_MCLK_0_N

DDR_MCLK_1_P

DDR_MCLK_1_N

DDR_MCLK_2_P

DDR_MCLK_2_N

DDR_MCLK_3_P

DDR_MCLK_3_N

DDR_MCLK_4_P

DDR_MCLK_4_N

DDR_MCLK_5_P

DDR_MCLK_5_N

DDR_REF

DDR_SELHI_0

DDR_SELHI_1

DDR_SELLO_0

DDR_SELLO_1

MEMORY

DDR

INTERFACE

DDR_A_10

DDR_A_11

DDR_A_12

DDR_A_9

DDR_A_8

DDR_A_7

DDR_A_6

DDR_A_5

DDR_A_4

DDR_A_3

DDR_A_2

DDR_A_1

DDR_A_0

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

SERIES RESISTORS FOR CONTROL SIGNALS

SYSCLK_DDRCLK_A0_UF

LOCATE THESE RESISTORS NEAR INTREPID

SYSCLK_DDRCLK_B2_L_UF

SYSCLK_DDRCLK_B2_UF

SYSCLK_DDRCLK_B1_UF

SYSCLK_DDRCLK_B0_UF

SYSCLK_DDRCLK_A0_L_UF

SYSCLK_DDRCLK_A1_UF

SYSCLK_DDRCLK_A1_L_UF

DDR MUX CONNECTIONS

0-ohm resistors to allow

INTREPID DDR CNTRL

(ON PAGE 12)

’1’S ARE SAME POLARITY (ACTIVE HI)

SYSCLK_DDRCLK_A2_UF

’0’S ARE SAME POLARITY (ACTIVE LO)

SEL = 1; HOST=A PORT, B PORT = 100 OHMGND

SYSCLK_DDRCLK_A2_L_UF

SYSCLK_DDRCLK_B1_L_UF

SYSCLK_DDRCLK_B0_L_UF

SEL = 0; HOST=B PORT, A PORT = 100 OHMGND

rewiring if necessary

MEM_MUXSEL_H<1>

MEM_MUXSEL_L<1>

LOCATE 2 DECOUPLING CAPS

DIRECTLY AT DDR_VREF_X BALLS

(U25-Y22 & T22)

22

5%

1/16W

SM1

5%

1/16W

SM1

22

SM1

5%

1/16W

22

SM1

1/16W

5%

22

SM1

1/16W

22

5%

SM1

5%

22

1/16W

22

SM1

1/16W

5%

22

SM1

5%

1/16W

22

SM1

1/16W

5%

22

SM1

5%

1/16W

22

SM1

1/16W

5%

22

SM1

5%

1/16W

22

SM1

1/16W

5%

22

SM1

5%

1/16W

SM1

5%

1/16W

22

SM1

1/16W

5%

22

SM1

5%

1/16W

22

SM1

1/16W

5%

22

22

1/16W

5%

SM1

22

5%

SM1

1/16W

1/16W

5%

SM1

22

5%

SM1

1/16W

22

22

1/16W

5%

SM1

22

5%

SM1

MEM_CKE<3>

1/16W

22

1/16W

5%

SM1

22

5%

1/16W

SM1

MEM_CKE<1>

402

MF

1/16W

5%

22

5%

1/16W

MF

402

22

1/16W

5%

SM1

22

1/16W

5%

SM1

22

1%

1/16W

402

MF

NOSTUFF

10K

NOSTUFF

10K

1/16W

MF

402

1%

NOSTUFF

402

MF

1/16W

1%

10K

NOSTUFF

402

MF

1/16W

1%

10K

1%

1K

402

MF

1/16W

INTREPID

BGA

SEE_TABLE

402

MF

1/16W

5%

47

MF

1/16W

5%

47

402

SM1

5%

1/16W

22

+2_5V_MAIN

1/16W

SM1

22

5%

22

SM1

5%

1/16W

5%

SM1

1/16W

22

22

SM1

1/16W

5%

SM1

22

5%

1/16W

1/16W

SM1

5%

22

1/16W

22

SM1

5%

051-6497

13

12 69

RAM_CS_L<3>

RAM_ADDR<11>

MEM_ADDR<11>

RAM_WE_LMEM_WE_L

RAM_BA<0>

MEM_BA<0>

RAM_BA<1>MEM_BA<1>

RAM_ADDR<9>

MEM_ADDR<9>

RAM_ADDR<0>

MEM_ADDR<0>

RAM_ADDR<1>MEM_ADDR<1>

RAM_ADDR<2>

MEM_ADDR<2>

MEM_CAS_L RAM_CAS_L

MEM_RAS_L RAM_RAS_L

RAM_CS_L<0>

MEM_CKE<0>

MEM_CS_L<0>

MEM_CKE<2>

RAM_CS_L<2>MEM_CS_L<2>

MEM_CS_L<3>

SYSCLK_DDRCLK_A0_UF

SYSCLK_DDRCLK_A0_L_UF

SYSCLK_DDRCLK_A1_UF

SYSCLK_DDRCLK_A1_L_UF

SYSCLK_DDRCLK_A2_UF

SYSCLK_DDRCLK_B2_UF

NO_TEST

SYSCLK_DDRCLK_B2_L_UF

RAM_ADDR<10>MEM_ADDR<10>

RAM_ADDR<7>MEM_ADDR<7>

RAM_ADDR<3>MEM_ADDR<3>

RAM_ADDR<4>MEM_ADDR<4>

SYSCLK_DDRCLK_B1_UF

NC_SYSCLK_DDRCLK_A2_L

NO_TEST

NO_TEST

NC_SYSCLK_DDRCLK_A2

SYSCLK_DDRCLK_A1_L

SYSCLK_DDRCLK_A1

SYSCLK_DDRCLK_A0_L

SYSCLK_DDRCLK_A0

MEM_MUXSEL_H<1>

MUX_SEL_L

INT_MEM_REF

MEM_DATA<54>

MEM_DATA<31>

MEM_DATA<29>

MEM_DATA<25>

MEM_DATA<24>

MEM_DATA<15>

MEM_DATA<63>

MEM_DATA<62>

MEM_DATA<61>

MEM_DATA<60>

MEM_DATA<59>

MEM_DATA<58>

MEM_DATA<57>

MEM_DATA<56>

MEM_DATA<55>

MEM_DATA<53>

MEM_DATA<52>

MEM_DATA<51>

MEM_DATA<50>

MEM_DATA<49>

MEM_DATA<48>

MEM_DATA<47>

MEM_DATA<46>

MEM_DATA<45>

MEM_DATA<44>

MEM_DATA<43>

MEM_DATA<42>

MEM_DATA<41>

MEM_DATA<40>

MEM_DATA<39>

MEM_DATA<38>

MEM_DATA<37>

MEM_DATA<36>

MEM_DATA<35>

MEM_DATA<34>

MEM_DATA<33>

MEM_DATA<32>

MEM_DATA<30>

MEM_DATA<28>

MEM_DATA<27>

MEM_DATA<26>

MEM_DATA<23>

MEM_DATA<22>

MEM_DATA<21>

MEM_DATA<20>

MEM_DATA<19>

MEM_DATA<18>

MEM_DATA<17>

MEM_DATA<16>

MEM_DATA<14>

MEM_DATA<13>

MEM_DATA<12>

MEM_DATA<11>

MEM_DATA<9>

MEM_DATA<8>

MEM_DATA<7>

MEM_DATA<6>

MEM_DATA<5>

MEM_DATA<4>

MEM_DATA<2>

MEM_DATA<0>

MEM_ADDR<0>

MEM_ADDR<12>

MEM_BA<0>

MEM_BA<1>

MEM_CS_L<0>

MEM_CS_L<1>

MEM_CS_L<2>

MEM_DQS<1>

MEM_ADDR<1>

MEM_ADDR<2>

MEM_ADDR<3>

MEM_ADDR<4>

MEM_ADDR<5>

MEM_ADDR<6>

MEM_ADDR<7>

MEM_ADDR<8>

MEM_ADDR<9>

MEM_ADDR<10>

MEM_ADDR<11>

MEM_DQS<2>

MEM_DQS<3>

MEM_DQS<4>

MEM_DQS<5>

MEM_DQS<6>

MEM_DQS<7>

MEM_DQM<2>

MEM_DQM<0>

MEM_DQM<1>

MEM_DQM<3>

MEM_DQM<4>

MEM_DQM<5>

MEM_DQM<6>

MEM_DQM<7>

MEM_RAS_L

MEM_CAS_L

MEM_WE_L

MEM_CKE<0>

MEM_CKE<1>

MEM_CKE<2>

MEM_CKE<3>

MEM_DATA<10>

SYSCLK_DDRCLK_B0_UF

SYSCLK_DDRCLK_B0

SYSCLK_DDRCLK_B1

SYSCLK_DDRCLK_B2

SYSCLK_DDRCLK_B2_L

MEM_ADDR<12>

RAM_ADDR<12>

MEM_ADDR<8>

RAM_ADDR<8>

MEM_ADDR<6>

RAM_ADDR<6>

MEM_ADDR<5>

RAM_ADDR<5>

MEM_DQS<0>

SYSCLK_DDRCLK_A2_L_UF

SYSCLK_DDRCLK_B0_L

SYSCLK_DDRCLK_B0_L_UF

SYSCLK_DDRCLK_B1_L

SYSCLK_DDRCLK_B1_L_UF

MEM_DATA<1>

MEM_CS_L<3>

RAM_CKE<1>

RAM_CKE<3>

RAM_CKE<0>

NC_MEM_MUXSEL_H<0>

NC_MEM_MUXSEL_L<0>

MEM_DATA<3>

MEM_MUXSEL_L<1>

MUX_SEL_H

INT_MEM_VREF

MIN_LINE_WIDTH=25

RAM_CKE<2>

MEM_CS_L<1> RAM_CS_L<1>

402

CERM

402

0.1UF

20%

10V

0.1UF

20%

10V

CERM

+2_5V_MAIN

MIN_LINE_WIDTH=20

DDR_VREF

100

100

1/16W

MF

402

1%

1/16W

MF

402

1%

<XR_PAGE_TITLE>

R625

1

2

U25

H32

AN35

AM35

AM36

AL36

AN34

AN36

AL35

AL33

L29

K30

H35

G35

G33

H33

D35

G36

F36

F35

E35

E36

G32

D36

H36

L30

M29

AK32

AK33

AH35

AG36

AH36

AH32

AG32

AG31

AE32

AF35

AF36

AE36

AK31

AE35

AE33

AD36

AD35

AA36

AA35

AA33

AB36

AB35

AC36

AK35

AA32

AB33

V36

U33

U32

V35

T30

U36

U35

T36

AK36

P33

R30

P35

P36

R36

R35

R33

R32

N35

M36

AJ32

L35

M35

M33

L36

N33

M30

J32

J33

J35

K32

AJ35

K33

J36

K36

K35

AJ36

AG33

AG35

AJ33

AH33

AD33

AC35

T35

T33

N32

L33

AJ31

AH31

AD32

AB30

V30

P32

N29

L32

Y33

Y32

Y36

Y35

W30

Y30

W33

W32

V32

V33

W36

W35

AA22

AB32

AE29

N30

T32

Y22

T22

R288

1 2

R261

1 2

RP102

1 8

RP102

2 7

RP102

3 6

RP102

4 5

RP105

1 8

RP105

2 7

RP105

3 6

RP109

4 5

RP109

1 8

RP109

2 7

RP68

1 8

RP68

2 7

RP68

3 6

RP68

4 5

RP62

1 8

RP62

2 7

RP62

3 6

RP62

4 5

RP116

1 8

RP116

2 7

RP116

3 6

RP116

4 5

RP71

1 8

RP71

2 7

RP71

3 6

RP71

4 5

RP51

1 8

RP51

2 7

RP51

3 6

RP51

4 5

RP52

1 8

RP52

2 7

RP52

3 6

RP52

4 5

R286

1 2

R697

1 2

C14

1

2

C30

1

2

R82

1

2

R93

1

2

RP109

3 6

RP105

4 5

R137

1

2

R214

1

2

R172

1

2

R235

1

2

LAST_MODIFIED=Wed Sep 17 12:15:52 2003

52A6>

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53C6<

53C6<

53C6<

15D8<

53C6<

53C6<

53C6<

15C4> 53D6<

15B6< 53C6<

15B6< 53D6<

15B6< 53D6<

15C6< 53D6<

15B6< 53D6<

15B6< 53D6<

15C6< 53D6<

53C6< 15B6<

53C6< 15B4>

53C6<

53C6<

53C6<

53C6<

53C6< 53C6<

53C6<

15B4> 53D6<

15C6< 53D6<

15C4> 53D6<

15C6< 53D6<

53C6<

53C6<

53C6<

53C6<

13C8<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53C6<

53C6<

53C6<

53C6<

53C6<

53D6<

53B6<

53B6<

53B6<

53B6<

53D6< 15C4>

53D6< 15C4>

53D6< 15C4>

53D6< 15C6<

53D6<

53B6<

53B6<

53D6<

53C6<

15C1<

15C4>

15C1<

53D6<

13C4<>

15C6<

53C6<

53C6<

14D8<>

12B6<>

12B6<>

15B4>

14B4<> 12D6<>

14B6<> 12C6<>

14B6<> 12D6<>

14B4<> 12D6<>

14B6<> 12D6<>

14B4<> 12D6<>

14B6<> 12D6<>

14B4<> 12D6<>

12C6<> 14B4<>

12C6<> 14B4<>

14B6<>

12C6<>

12C6<>

12B6<>

15B4>

12C6<>

12C6<>

53C6<

53C6<

53C6<

53C6<

53C6<

53B6<

53B6<

14B6<> 12D6<>

14B6<> 12D6<>

14B6<> 12D6<>

14B4<> 12D6<>

53B6<

14A4<>

14A4<>

14D6<>

14D6<>

53C6<

13A6<>

13B3<>

13A6<>

13A6<>

13A6<>

13A6<>

13C8<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13B3<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C4<>

13A6<>

13A6<>

13A6<>

13A6<>

13B6<>

13B6<>

13B6<>

13B6<>

13B6<>

13B6<>

13B6<>

13B6<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

13C8<>

12C3<

12D2<

12B3<

12B3<

12C2<

12C2<

12B2<

13C8<>

12C3<

12C3<

12D3<

12D3<

12C2<

12D2<

12D3<

12D2<

12C3<

12C3<

12B3<

13A6<>

13A6<>

13C4<>

13C4<>

13B3<>

13B3<>

13A6<>

13C8<>

13C8<>

13A6<>

13C4<>

13C4<>

13B3<>

13B3<>

12A3<

12A3<

12B3<

12C2<

12B2<

12C2<

12B2<

13C8<>

53B6<

15B4>

15D6<

15A6<

15A6<

12D6<> 14B6<>

12D6<> 14B4<>

12D6<> 14B4<>

12D6<> 14B6<>

13C8<>

53B6<

15B3>

53B6<

15C6<

53B6<

13C8<>

12B2<

14B6<>

15A1<

14B4<>

13C8<>

53C6<

13A3<>

14A1<

15B1<

12C6<> 14B4<>

14D2<>

SYM_VER-3

GND

SEL

DB19*

DB18*

DB17*

DB16*

DB15*

DB14*

DB13*

DB12*

DB11*

DB10*

DB9*DH19

DH14

DH13

DH12

DH11

DH10

DH9

DH15

DH16

DH17

DH18

DB4*

DB5*

DB6*

DB7*

DB8*

DB0*

DB1*

DB2*

DB3*

DH4

DH3

DH2

DH1

DH0

DH8

DH7

DH6

DH5

DA15

DA16

DA17

DA18

DA19

DA13

DA14

DA12

DA11

DA10

DA5

DA6

DA7

DA8

DA9

DA0

DA1

DA2

DA3

DA4

VDD

SYM_VER-3

GND

SEL

DB19*

DB18*

DB17*

DB16*

DB15*

DB14*

DB13*

DB12*

DB11*

DB10*

DB9*DH19

DH14

DH13

DH12

DH11

DH10

DH9

DH15

DH16

DH17

DH18

DB4*

DB5*

DB6*

DB7*

DB8*

DB0*

DB1*

DB2*

DB3*

DH4

DH3

DH2

DH1

DH0

DH8

DH7

DH6

DH5

DA15

DA16

DA17

DA18

DA19

DA13

DA14

DA12

DA11

DA10

DA5

DA6

DA7

DA8

DA9

DA0

DA1

DA2

DA3

DA4

VDD

SYM_VER-3

GND

SEL

DB19*

DB18*

DB17*

DB16*

DB15*

DB14*

DB13*

DB12*

DB11*

DB10*

DB9*DH19

DH14

DH13

DH12

DH11

DH10

DH9

DH15

DH16

DH17

DH18

DB4*

DB5*

DB6*

DB7*

DB8*

DB0*

DB1*

DB2*

DB3*

DH4

DH3

DH2

DH1

DH0

DH8

DH7

DH6

DH5

DA15

DA16

DA17

DA18

DA19

DA13

DA14

DA12

DA11

DA10

DA5

DA6

DA7

DA8

DA9

DA0

DA1

DA2

DA3

DA4

VDD

SYM_VER-3

GND

SEL

DB19*

DB18*

DB17*

DB16*

DB15*

DB14*

DB13*

DB12*

DB11*

DB10*

DB9*DH19

DH14

DH13

DH12

DH11

DH10

DH9

DH15

DH16

DH17

DH18

DB4*

DB5*

DB6*

DB7*

DB8*

DB0*

DB1*

DB2*

DB3*

DH4

DH3

DH2

DH1

DH0

DH8

DH7

DH6

DH5

DA15

DA16

DA17

DA18

DA19

DA13

DA14

DA12

DA11

DA10

DA5

DA6

DA7

DA8

DA9

DA0

DA1

DA2

DA3

DA4

VDD

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

DDR MUXES

<XR_PAGE_TITLE>

MUX_SEL_H

MEM_DQM<7>

MEM_DQS<7>

MEM_DATA<63>

MEM_DATA<62>

MEM_DATA<61>

MEM_DATA<60>

MEM_DQM<6>

MEM_DATA<56>

MEM_DATA<57>

MEM_DATA<59>

MEM_DATA<58>

MEM_DATA<52>

MEM_DATA<53>

MEM_DATA<54>

MEM_DATA<55>

MEM_DQS<6>

MEM_DATA<49>

MEM_DATA<48>

MEM_DATA<51>

MEM_DATA<50>

RAM_DQM_B<7>

RAM_DATA_B<61>

RAM_DATA_B<62>

RAM_DATA_B<63>

RAM_DQS_B<7>

RAM_DATA_B<60>

RAM_DATA_B<56>

RAM_DATA_B<57>

RAM_DATA_B<58>

RAM_DATA_B<59>

RAM_DQM_B<6>

RAM_DQS_B<6>

RAM_DATA_B<55>

RAM_DATA_B<54>

RAM_DATA_B<53>

RAM_DATA_B<52>

RAM_DATA_B<48>

RAM_DATA_B<49>

RAM_DATA_B<51>

RAM_DATA_B<50>

RAM_DATA_A<62>

RAM_DATA_A<61>

RAM_DATA_A<63>

RAM_DQS_A<7>

RAM_DQM_A<7>

RAM_DATA_A<59>

RAM_DATA_A<60>

RAM_DATA_A<56>

RAM_DATA_A<57>

RAM_DATA_A<58>

RAM_DATA_A<54>

RAM_DATA_A<53>

RAM_DATA_A<55>

RAM_DQS_A<6>

RAM_DQM_A<6>

RAM_DATA_A<49>

RAM_DATA_A<48>

RAM_DATA_A<50>

RAM_DATA_A<51>

RAM_DATA_A<52>

MUX_SEL_H

MEM_DQM<5>

MEM_DQS<5>

MEM_DATA<47>

MEM_DATA<46>

MEM_DATA<45>

MEM_DATA<44>

MEM_DQM<4>

MEM_DATA<40>

MEM_DATA<41>

MEM_DATA<43>

MEM_DATA<42>

MEM_DATA<36>

MEM_DATA<37>

MEM_DATA<38>

MEM_DATA<39>

MEM_DQS<4>

MEM_DATA<33>

MEM_DATA<32>

MEM_DATA<35>

MEM_DATA<34>

RAM_DQM_B<5>

RAM_DATA_B<45>

RAM_DATA_B<46>

RAM_DATA_B<47>

RAM_DQS_B<5>

RAM_DATA_B<44>

RAM_DATA_B<40>

RAM_DATA_B<41>

RAM_DATA_B<42>

RAM_DATA_B<43>

RAM_DQM_B<4>

RAM_DQS_B<4>

RAM_DATA_B<39>

RAM_DATA_B<38>

RAM_DATA_B<37>

RAM_DATA_B<36>

RAM_DATA_B<32>

RAM_DATA_B<33>

RAM_DATA_B<35>

RAM_DATA_B<34>

RAM_DATA_A<46>

RAM_DATA_A<45>

RAM_DATA_A<47>

RAM_DQS_A<5>

RAM_DQM_A<5>

RAM_DATA_A<43>

RAM_DATA_A<44>

RAM_DATA_A<40>

RAM_DATA_A<41>

RAM_DATA_A<42>

RAM_DATA_A<38>

RAM_DATA_A<37>

RAM_DATA_A<39>

RAM_DQS_A<4>

RAM_DQM_A<4>

RAM_DATA_A<33>

RAM_DATA_A<32>

RAM_DATA_A<34>

RAM_DATA_A<35>

RAM_DATA_A<36>

MUX_SEL_L

MEM_DQM<1>

MEM_DQS<1>

MEM_DATA<15>

MEM_DATA<14>

MEM_DATA<13>

MEM_DATA<12>

MEM_DQM<0>

MEM_DATA<8>

MEM_DATA<9>

MEM_DATA<11>

MEM_DATA<10>

MEM_DATA<4>

MEM_DATA<5>

MEM_DATA<6>

MEM_DATA<7>

MEM_DQS<0>

MEM_DATA<1>

MEM_DATA<0>

MEM_DATA<3>

MEM_DATA<2>

RAM_DQM_B<1>

RAM_DATA_B<13>

RAM_DATA_B<14>

RAM_DQS_B<1>

RAM_DATA_B<8>

RAM_DATA_B<9>

RAM_DATA_B<10>

RAM_DATA_B<11>

RAM_DQM_B<0>

RAM_DQS_B<0>

RAM_DATA_B<7>

RAM_DATA_B<6>

RAM_DATA_B<5>

RAM_DATA_B<4>

RAM_DATA_B<0>

RAM_DATA_B<1>

RAM_DATA_B<3>

RAM_DATA_B<2>

RAM_DATA_A<14>

RAM_DATA_A<13>

RAM_DATA_A<15>

RAM_DQS_A<1>

RAM_DQM_A<1>

RAM_DATA_A<11>

RAM_DATA_A<12>

RAM_DATA_A<8>

RAM_DATA_A<9>

RAM_DATA_A<10>

RAM_DATA_A<6>

RAM_DATA_A<5>

RAM_DATA_A<7>

RAM_DQS_A<0>

RAM_DQM_A<0>

RAM_DATA_A<1>

RAM_DATA_A<0>

RAM_DATA_A<2>

RAM_DATA_A<3>

RAM_DATA_A<4>

MUX_SEL_L

MEM_DQM<3>

MEM_DQS<3>

MEM_DATA<31>

MEM_DATA<30>

MEM_DATA<29>

MEM_DATA<28>

MEM_DQM<2>

MEM_DATA<24>

MEM_DATA<25>

MEM_DATA<27>

MEM_DATA<26>

MEM_DATA<20>

MEM_DATA<21>

MEM_DATA<22>

MEM_DATA<23>

MEM_DQS<2>

MEM_DATA<17>

MEM_DATA<16>

MEM_DATA<19>

MEM_DATA<18>

RAM_DQM_B<3>

RAM_DATA_B<29>

RAM_DATA_B<30>

RAM_DATA_B<31>

RAM_DQS_B<3>

RAM_DATA_B<28>

RAM_DATA_B<24>

RAM_DATA_B<25>

RAM_DATA_B<26>

RAM_DATA_B<27>

RAM_DQM_B<2>

RAM_DQS_B<2>

RAM_DATA_B<23>

RAM_DATA_B<22>

RAM_DATA_B<21>

RAM_DATA_B<20>

RAM_DATA_B<16>

RAM_DATA_B<17>

RAM_DATA_B<19>

RAM_DATA_B<18>

RAM_DATA_A<30>

RAM_DATA_A<29>

RAM_DATA_A<31>

RAM_DQS_A<3>

RAM_DQM_A<3>

RAM_DATA_A<27>

RAM_DATA_A<28>

RAM_DATA_A<24>

RAM_DATA_A<25>

RAM_DATA_A<26>

RAM_DATA_A<22>

RAM_DATA_A<21>

RAM_DATA_A<23>

RAM_DQS_A<2>

RAM_DQM_A<2>

RAM_DATA_A<17>

RAM_DATA_A<16>

RAM_DATA_A<18>

RAM_DATA_A<19>

RAM_DATA_A<20>

051-6497

13

13 69

BGA

CBTV4020

BGA

CBTV4020

CBTV4020

BGA

CBTV4020

RAM_DATA_B<12>

RAM_DATA_B<15>

BGA

+2_5V_MAIN

+2_5V_MAIN

+2_5V_MAIN

+2_5V_MAIN

402

CERM

10V

20%

0.1UF

NOSTUFF

20%

10V

CERM

402

0.1UF

20%

10V

402

0.1UF

NOSTUFF

CERM

402

10V

20%

0.1UF

CERM

0.1UF

402

CERM

10V

20%

0.1UF

402

CERM

10V

20%

402

CERM

10V

20%

0.1UF

20%

10V

402

CERM

0.1UF

NOSTUFF

0.1UF

20%

10V

CERM

402

0.1UF

NOSTUFF

CERM

402

10V

20%

10UF

Y5V

10V

N20P80%

805

0.1UF

20%

10V

CERM

402

0.1UF

402

CERM

10V

20%

C611

1

2

C612

1

2

C230

1

2

C613

1

2

C671

1

2

C859

1

2

C908

1

2

C670

1

2

C669

1

2

C858

1

2

C860

1

2

C909

1

2

C910

1

2

U18

F1

H1

K1

K3

K4

K6

J7

K9

J10

G10

E10

C10

A10

A8

A7

A5

B4

A2

B1

D1

G1

J1

K2

J4

K5

K7

K8

K10

H10

F10

D10

B10

A9

B7

A6

A4

A3

A1

C1

E1

F2

H2

J2

J3

J5

J6

J8

J9

H9

F9

E9

C9

B9

B8

B6

B5

B3

B2

C2

E2

C5

C6

D2

D9

G2

G9

H5

H6

E3

E8

F3

F8

U22

F1

H1

K1

K3

K4

K6

J7

K9

J10

G10

E10

C10

A10

A8

A7

A5

B4

A2

B1

D1

G1

J1

K2

J4

K5

K7

K8

K10

H10

F10

D10

B10

A9

B7

A6

A4

A3

A1

C1

E1

F2

H2

J2

J3

J5

J6

J8

J9

H9

F9

E9

C9

B9

B8

B6

B5

B3

B2

C2

E2

C5

C6

D2

D9

G2

G9

H5

H6

E3

E8

F3

F8

U27

F1

H1

K1

K3

K4

K6

J7

K9

J10

G10

E10

C10

A10

A8

A7

A5

B4

A2

B1

D1

G1

J1

K2

J4

K5

K7

K8

K10

H10

F10

D10

B10

A9

B7

A6

A4

A3

A1

C1

E1

F2

H2

J2

J3

J5

J6

J8

J9

H9

F9

E9

C9

B9

B8

B6

B5

B3

B2

C2

E2

C5

C6

D2

D9

G2

G9

H5

H6

E3

E8

F3

F8

U29

F1

H1

K1

K3

K4

K6

J7

K9

J10

G10

E10

C10

A10

A8

A7

A5

B4

A2

B1

D1

G1

J1

K2

J4

K5

K7

K8

K10

H10

F10

D10

B10

A9

B7

A6

A4

A3

A1

C1

E1

F2

H2

J2

J3

J5

J6

J8

J9

H9

F9

E9

C9

B9

B8

B6

B5

B3

B2

C2

E2

C5

C6

D2

D9

G2

G9

H5

H6

E3

E8

F3

F8

LAST_MODIFIED=Wed Sep 17 12:15:54 2003

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

13C4<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15A8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14A8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

13A3<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14B8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

13A6<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14D6<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14D6<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

13C8<>

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15C8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14C8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

14C8<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

12D4<

12C6<>

12C6<>

12B8<>

12B8<>

12B8<>

12B8<>

12C6<>

12B8<>

12B8<>

12B8<>

12B8<>

12B8<>

12B8<>

12B8<>

12B8<>

12C6<>

12B8<>

12B8<>

12B8<>

12B8<>

15A4>

15A4>

15A4>

15A4>

15A6<

15A4>

15A6<

15A6<

15A6<

15A6<

15A4>

15A6<

15A4>

15A4>

15A4>

15A4>

15A6<

15A6<

15A6<

15A6<

14A4<>

14A4<>

14A4<>

14A6<>

14A4<>

14A6<>

14A4<>

14A6<>

14A6<>

14A6<>

14A4<>

14A4<>

14A4<>

14A6<>

14A4<>

14A6<>

14A6<>

14A6<>

14A6<>

14A4<>

12D4<

12C6<>

12C6<>

12B8<>

12B8<>

12B8<>

12B8<>

12C6<>

12B8<>

12B8<>

12B8<>

12B8<>

12C8<>

12C8<>

12C8<>

12C8<>

12C6<>

12C8<>

12C8<>

12C8<>

12C8<>

15B4>

15B4>

15A4>

15A4>

15B6<

15B4>

15B6<

15B6<

15A6<

15A6<

15B4>

15B6<

15B4>

15B4>

15B4>

15B4>

15B6<

15B6<

15B6<

15B6<

14A4<>

14B4<>

14A4<>

14A6<>

14A4<>

14A6<>

14B4<>

14B6<>

14B6<>

14A6<>

14B4<>

14B4<>

14B4<>

14B6<>

14B4<>

14B6<>

14B6<>

14B6<>

14B6<>

14B4<>

12D4<

12C6<>

12C6<>

12C8<>

12C8<>

12D8<>

12D8<>

12C6<>

12D8<>

12D8<>

12D8<>

12D8<>

12D8<>

12D8<>

12D8<>

12D8<>

12C6<>

12D8<>

12D8<>

12D8<>

12D8<>

15D4>

15D4>

15C4>

15C8<

15D6<

15D6<

15C6<

15C6<

15D4>

15C8<

15D4>

15D4>

15D4>

15D4>

15D6<

15D6<

15D6<

15D6<

14D4<>

14D4<>

14D4<>

14C8<

14D4<>

14D6<>

14D4<>

14D6<>

14D6<>

14D6<>

14D4<>

14D4<>

14D4<>

14C8<

14D4<>

14D6<>

14D6<>

14D6<>

14D6<>

14D4<>

12D4<

12C6<>

12C6<>

12C8<>

12C8<>

12C8<>

12C8<>

12C6<>

12C8<>

12C8<>

12C8<>

12C8<>

12C8<>

12C8<>

12C8<>

12C8<>

12C6<>

12C8<>

12C8<>

12C8<>

12C8<>

15C4>

15C4>

15C4>

15C4>

15B8<

15C4>

15C6<

15C6<

15C6<

15C6<

15C4>

15C6<

15C4>

15C4>

15C4>

15C4>

15C6<

15C6<

15C6<

15C6<

14C4<>

14C4<>

14C4<>

14C6<>

14C4<>

14C6<>

14C4<>

14C6<>

14C6<>

14C6<>

14C4<>

14C4<>

14C4<>

14C6<>

14C4<>

14C6<>

14D6<>

14C6<>

14C6<>

14D4<>

15D4>

15C4>

DQ58

RFU18

KEY

VREF0

VDD0

DQ0

DQ1

VSS0

DQS0

VSS2

DQ3

DQ8

DQ2

VDD2

VSS4

DQS1

DQ10

DQ9

DQ11

CK0

CK0*

VSS7

VDD4

DQ16

DQ18

VDD7

DQ17

DQS2

VSS9

DQ25

VDD9

DQ24

DQ19

DQS3

VDD11

DQ27

DQ26

VSS11

RFU0

VDD13

RFU4

VSS13

RFU2

RFU6

RFU13

RFU12

RFU8

RFU10

VSS15

A9

CKE1

RFU14

VDD16

A1

A5

A7

VSS18

A3

BA0

VDD18

S0*

WE*

A10_AP

DQ33

VSS20

DQ32

VDD20

RFU16

DQS4

DQ34

VSS22

DQ35

DQ40

VDD22

DQ41

DQS5

VSS24

DQ42

DQ43

DQ48

VSS26

VDD26

VDD24

VSS27

VSS29

DQ50

DQ49

DQS6

VDD27

DQS7

DQ51

VDD29

DQ56

DQ57

SDA

VDD31

VSS31

DQ59

VDDSPD

SCL

RFU19

VDD32

VSS28

CK1

DQ52

VDD28

DM6

DQ54

VSS30

DM7

DQ55

DQ60

VDD30

DQ61

DQ53

SA1

SA2

SA0

DQ63

DQ62

VSS32

VSS25

DM5

DQ45

VDD23

VDD21

VSS21

DQ36

RFU17

DQ44

DM4

DQ39

VSS23

DQ38

DQ37

RAS*

CAS*

S1*

DQ46

DQ47

CK1*

VDD25

RFU7

RFU5

VDD14

VSS17

VDD15

CKE0

RFU15

VDD17

A11

A8

RFU11

VSS16

RFU9

VSS19

A0

A2

A4

A6

BA1

VDD19

VDD12

VSS12

DQ31

DQ30

DM3

DQ22

DQ21

VDD8

DQ20

DQ29

VSS10

VDD10

DQ28

DQ23

DM2

VSS6

VSS8

RFU1

VSS14

RFU3

VREF1

DQ5

DQ4

DM0

DQ6

DQ12

DQ7

VSS3

VSS1

VDD1

VDD3

DM1

VSS5

DQ14

DQ13

DQ15

VDD5

VDD6

A12

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DRAWING

ALONG VREF TRACE

DISTRIBUTE THESE TWO CAPS

(516S0029)

ADDR=0 (0xA0)

LOCATE THESE RESISTORS BETWEEN DIMMS

DDR DECOUPLING

SLOT "A"

1 - 10UF

24 - 0.1UF

SO-DIMM SLOT A

DIRECTLY ON PIN AT J26-1

LOCATE C1601 AND C1401

LOCATE C1602 AND C1402

DIRECTLY ON PIN AT J26-2

1/16W

MF

402

MF

1/16W

1%

100

1%

100

INT_MEM_VREF

MIN_LINE_WIDTH=25

402

10V

20%

0.1UF

10V

20%

0.1UF

CERM

402

402

CERM

+2_5V_MAIN

CERM

10V

20%

0.1UF

10V

20%

0.1UF

10V

20%

0.1UF

10V

20%

0.1UF

402

CERM

NOSTUFF

CERM

402

NOSTUFF

402

CERM

402

<XR_PAGE_TITLE>

RAM_DQS_A<2>

RAM_DQS_A<1>

RAM_DATA_A<2>

NC_SODIMM85

NO_TEST

RAM_DATA_A<25>

RAM_DQS_A<3>

NC_SODIMM89

NO_TEST

RAM_DATA_A<16>

RAM_DATA_A<24>

NC_SODIMM91

NO_TEST

MIN_LINE_WIDTH=20

DDR_VREF

RAM_DATA_A<7>

NC_SODIMM201

NO_TEST

NC_SODIMM202

NO_TEST

RAM_DATA_A<0>

RAM_DATA_A<1>

RAM_DQS_A<0>

RAM_DATA_A<3>

RAM_DATA_A<8>

RAM_DATA_A<9>

RAM_DQS_A<1>

SYSCLK_DDRCLK_A0_L

RAM_DATA_A<17>

RAM_DATA_A<18>

RAM_DATA_A<27>

NC_SODIMM71

NO_TEST

NC_SODIMM73

NO_TEST

NC_SODIMM83

NO_TEST

RAM_CKE<1>

RAM_ADDR<9>

NC_SODIMM97

NO_TEST

RAM_ADDR<7>

RAM_ADDR<5>

RAM_ADDR<3>

RAM_ADDR<1>

RAM_ADDR<10>

RAM_BA<0>

RAM_CS_L<0>

RAM_WE_L

RAM_DATA_A<32>

NC_SODIMM123

NO_TEST

RAM_DATA_A<33>

RAM_DQS_A<4>

RAM_DATA_A<34>

RAM_DATA_A<35>

RAM_DATA_A<40>

RAM_DATA_A<41>

RAM_DQS_A<5>

RAM_DATA_A<42>

RAM_DATA_A<43>

RAM_DATA_A<48>

RAM_DATA_A<49>

RAM_DATA_A<50>

RAM_DQS_A<6>

RAM_DATA_A<56>

RAM_DATA_A<51>

RAM_DQS_A<7>

RAM_DATA_A<57>

RAM_DATA_A<58>

RAM_DATA_A<59>

INT_I2C_DATA0

INT_I2C_CLK0

NC_SODIMM199

NO_TEST

NC_SODIMM200

NO_TEST

RAM_DATA_A<62>

RAM_DATA_A<61>

RAM_DATA_A<63>

RAM_DATA_A<60>

RAM_DATA_A<55>

RAM_DQM_A<6>

RAM_DATA_A<54>

RAM_DATA_A<53>

RAM_DATA_A<52>

SYSCLK_DDRCLK_A1

SYSCLK_DDRCLK_A1_L

RAM_DATA_A<45>

RAM_DQM_A<5>

RAM_DATA_A<44>

RAM_DATA_A<39>

RAM_DQM_A<4>

RAM_DATA_A<37>

NC_SODIMM124

NO_TEST

RAM_CAS_L

RAM_RAS_L

RAM_CS_L<1>

RAM_ADDR<4>

RAM_ADDR<0>

RAM_ADDR<6>

NC_SODIMM98

NO_TEST

RAM_ADDR<8>

RAM_ADDR<11>

RAM_ADDR<2>

RAM_BA<1>

RAM_CKE<0>

NC_SODIMM84

NO_TEST

NC_SODIMM86

NO_TEST

NC_SODIMM78

NO_TEST

NC_SODIMM80

NO_TEST

RAM_DATA_A<31>

RAM_DQM_A<3>

RAM_DATA_A<30>

RAM_DATA_A<29>

NC_SODIMM72

NO_TEST

NC_SODIMM74

NO_TEST

RAM_DATA_A<28>

RAM_DATA_A<23>

RAM_DATA_A<22>

RAM_DATA_A<21>

RAM_DATA_A<20>

RAM_DATA_A<15>

RAM_DATA_A<14>

RAM_DATA_A<13>

RAM_DQM_A<1>

RAM_DATA_A<12>

RAM_DATA_A<6>

RAM_DQM_A<0>

RAM_DATA_A<5>

RAM_DATA_A<4>

RAM_ADDR<12>

RAM_DQM_A<7>

RAM_DATA_A<47>

RAM_DATA_A<46>

RAM_DATA_A<38>

RAM_DATA_A<36>

NC_SODIMM77

NO_TEST

NC_SODIMM79

NO_TEST

RAM_DQS_A<0>

RAM_DQS_A<2>

RAM_DQS_A<3>

RAM_DQS_A<4>

RAM_DQS_A<6>

RAM_DQS_A<7>

RAM_DQS_A<5>

RAM_DATA_A<26>

SYSCLK_DDRCLK_A0

RAM_DATA_A<11>

RAM_DQM_A<2>

RAM_DATA_A<10>

DDR_VREF

MIN_LINE_WIDTH=20

RAM_DATA_A<19>

6914

13

051-6497

0.1UF

20%

10V

CERM

402

CERM

0.1UF

402

10V

20%

0.1UF

20%

10V

CERM

402

20%

10V

CERM

402

0.1UF

10V

20%

CERM

402

0.1UF

20%

0.1UF

402

CERM

10V

10UF

805

N20P80%

10V

Y5V

+2_5V_MAIN

+2_5V_MAIN

+3V_MAIN

F-RT-SM

AS0A42-D2R

402

CERM

10V

20%

0.1UF

805

Y5V

10V

N20P80%

10UF

+2_5V_MAIN

+2_5V_MAIN

+2_5V_MAIN

0.1UF

402

CERM

10V

20%

0.1UF

20%

10V

CERM

402

0.1UF

20%

10V

CERM

402

0.1UF

20%

10V

CERM

402

0.1UF

402

CERM

10V

20%

0.1UF

402

CERM

10V

20%

0.1UF

402

CERM

10V

20%

402

0.1UF

CERM

10V

20%20%

0.1UF

402

CERM

10V

0.1UF

20%

10V

CERM

402

0.1UF

20%

10V

402

CERM

20%

402

CERM

0.1UF

10V

CERM

10V

402

20%

0.1UF

+2_5V_MAIN

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

1/16W

470

5%

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

402

470

5%

1/16W

MF

NOSTUFF

1/16W

470

5%

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

1/16W

470

5%

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

470

5%

1/16W

MF

402

NOSTUFF

5%

402

MF

1/16W

470

402

MF

1/16W

5%

470

NOSTUFF

20%

CERM

10V

0.1UF

402

20%

CERM

10V

0.1UF

402402

10V

20%

0.1UF

CERM

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

0.1UF

402

20%

10V

CERM

0.1UF

20%

CERM

10V

0.1UF

402

+2_5V_MAIN

0.1UF

20%

10V

CERM

402

20%

10V

CERM

402

0.1UF

20%

10V

CERM

402

0.1UF

402

0.1UF

CERM

10V

20%

0.1UF

20%

10V

CERM

402

C244

1

2

C263

1

2

C320

1

2

C243

1

2

C255

1

2

C256

1

2

C275

1

2

C242

1

2

C313

1

2

C261

1

2

C304

1

2

C276

1

2

C311

1

2

C319

1

2

C929

1

2

J26

112111

115

100

99

110109

108107

106105

102101

117

116

120

35

37

160

158

9695

12

26

48

62

134

148

170

184

5

7

29

31

20

24

30

32

41

43

49

53

13

42

44

50

54

55

59

65

67

56

60

17

66

68

127

129

135

139

128

130

136

140

6

141

145

151

153

142

146

152

154

163

165

8

171

175

164

166

172

176

177

181

187

189

14

178

182

188

190

18

19

23

11

25

47

61

133

147

169

183

201

202

118

71 72

85 86

89

91

97 98

123 124

199 200

73 74

77 78

79 80

83 84

121 122

194

196

198

195

193

9

10

58

69 70

81 82

92

93 94

113 114

21

131 132

143 144

155 156

157

167 168

179

22

180

191 192

33 34

36

45 46

57

197

1 2

3 4

52

63 64

75 76

87 88

90

103 104

15

125 126

137 138

149 150

159

161 162

173

16

174

185 186

27 28

38

39 40

51

119

C1602

1

2

C1601

1

2

R1401

1

2

R1402

1

2

C1401

1

2

C1402

1

2

C1414

1

2

C1403

1

2

C1404

1

2

C1405

1

2

C1413

1

2

C1412

1

2

C1411

1

2

C1410

1

2

C1409

1

2

C1408

1

2

C1407

1

2

C1406

1

2

C1418

1

2

C1417

1

2

C1416

1

2

C1415

1

2

C1419

1

2

C1420

1

2

C1421

1

2

R1403

1 2

R1404

1 2

R1406

1 2

R1405

1 2

R1408

1 2

R1407

1 2

R1410

1 2

R1409

1 2

R1412

1 2

R1411

1 2

R1414

1 2

R1413

1 2

R1416

1 2

R1415

1 2

R1418

1 2

R1417

1 2

C46

1

2

C47

1

2

LAST_MODIFIED=Wed Sep 17 12:15:56 2003

52A6>

52A6>

53D6<

53D6< 53D6<

15D8<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15D8<

14C8<

14D6<>

53D6<

53D6<

14C8<

53D6<

53D6<

14D8<>

53D6<

53D6<

53D6<

14C8<

53D6<

53D6<

53D6<

14C8<

53D6<

53D6<

53D6<

15C1<

15C6<

15C6<

15C6<

15C4>

15B6<

15B4>

15B6<

53C6<

15B6<

53D6<

53D6<

14B8<

53D6<

53D6<

53D6<

53D6<

14B8<

53D6<

53D6<

53D6<

53D6<

53D6<

14B8<

53D6<

53D6<

14A8<

53D6<

53D6<

53D6<

34B3<

34B3<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53C6<

53C6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15B6<

15B4>

53C6<

15C6<

15B6<

15C4>

15C4>

15C4>

15C6<

15B6<

15C1<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

53D6<

15C4>

53D6<

53D6<

53D6<

53D6<

53D6<

14D6<>

14C6<>

14C6<>

14B6<>

14A6<>

14A6<>

14A6<>

53D6<

53C6<

53D6<

53D6<

53D6<

14D2<>

53D6<

12A8<>

13B5<>

13C7<>

13D7<>

13B5<>

13B5<>

13B5<>

13B5<>

12A7<

13D7<>

13D7<>

13D7<>

13D7<>

13D7<>

13C7<>

13C7<>

13C7<>

53C6<

13B5<>

13B5<>

13B5<>

12B1<

12C3<

12D3<

12C1<

12D3<

12C3<

12C3<

12B3<

12C1<

12B3<

13D4<>

13D4<>

13D4<>

13D4<>

13D4<>

13D4<>

13C4<>

13C4<>

13C4<>

13C4<>

13C2<>

13C2<>

13C2<>

13B2<>

13B2<>

13C2<>

13B2<>

13B2<>

13B2<>

13B2<>

15A6<

15A6<

13B2<>

13B2<>

13B2<>

13B2<>

13B2<>

13B2<>

13B2<>

13C2<>

13C2<>

12C4<

12B4<

13C4<>

13C4<>

13C4<>

13D4<>

13D4<>

13D4<>

12A2<

12A2<

12C1<

12D3<

12C3<

12D1<

12D1<

12B3<

12C3<

12B3<

12C1<

13B5<>

13A5<>

13B5<>

13B5<>

13B5<>

13B5<>

13B5<>

13B5<>

13B5<>

13C7<>

13C7<>

13C7<>

13C7<>

13C7<>

13D7<>

13D7<>

13D7<>

13D7<>

12D1<

13B2<>

13C4<>

13C4<>

13D4<>

13D4<>

13D7<>

13B5<>

13B5<>

13D4<>

13B2<>

13B2<>

13C4<>

13B5<>

12C4<

13C7<>

13B5<>

13C7<>

12A7<

13B5<>

剩余68页未读,继续阅读

428 浏览量

235 浏览量

1555 浏览量

2015-06-01 上传

390 浏览量

153 浏览量

320 浏览量

151 浏览量

thinkernb945

- 粉丝: 1

- 资源: 43

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 基于ADO数据访问技术的等边角钢参数化设计.doc

- 如何实现无刷新的DropdownList联动效果

- 网络工程投标书样本2009

- VS2005(c#)项目调试问题解决方案集锦(五)

- VS2005(c#)项目调试问题解决方案集锦(四)

- 《python核心笔记》

- H.264_中英文对照翻译(AVS264 V1.0)

- java cook book

- PHP在Web开发领域的优势

- Spring 入门书籍

- 《微内核工作流引擎体系结构与部分解决方案参考》

- PHP初学者头疼问题总结

- ArcObjects+GIS应用开发——基于C#.NET

- 工作流引擎核心调度算法与PetriNet_胡长城.pdf

- 《工作流模型分析》胡长城

- c8051f020文档资料

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功